lpddr5专题

LPDDR6与LPDDR5 State Diagram技术探讨

相对于LPDDR5: 1)去掉DSM 2)idle到per-bank-refresh变成per-2-bank-refresh,LPDDR6下可自由组合任两个bank刷新,以提高性能 3)sref到进入command bus training后可MRR、MRW、CAS、MPC等命令 4)idle power down期间可MRR、MRW、CAS、MPC等命令 5)idle到进入command bus

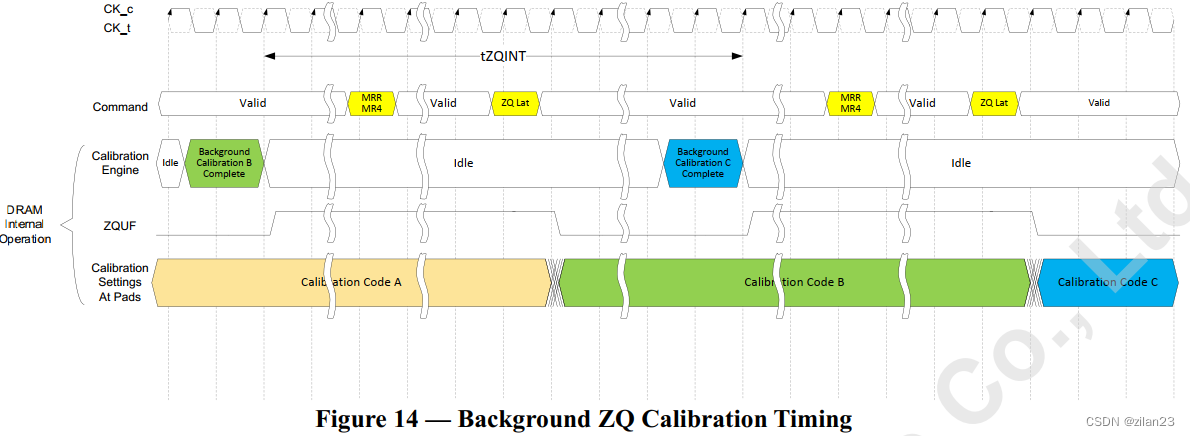

LPDDR6与LPDDR5 ZQ Calibration技术探讨

LPDDR6相比LPDDR5在ZQ校准这一块删除了command-based相关的描述,删除了ZQ校准模式切换的描述,仅支持background-based的校准。 回顾一下LPDDR5 基于background-based的校准: background ZQC是通过MR28 OP[5]来选择的,当选择为0(默认)即为background ZQC,当选择为background ZQC后还需

H58GG6MK6GX037N 海力士LPDDR5 6400Mbps 12GB 高性能内存解析

引言: 海力士(Hynix)最近推出的LPDDR5 6400Mbps 12GB内存开启了智能技术发展的新篇章。这款内存具备高速性能和低功耗,以及广泛的应用领域,如手机、PC和自动驾驶领域。我们将深入探讨LPDDR5的技术特点,以及它如何推动智能技术的进步。 高速性能和低功耗: H58GG6MK6GX037N LPDDR5 6400Mbps内存的出现标志着内存技术的重大突破。它不仅提供了极

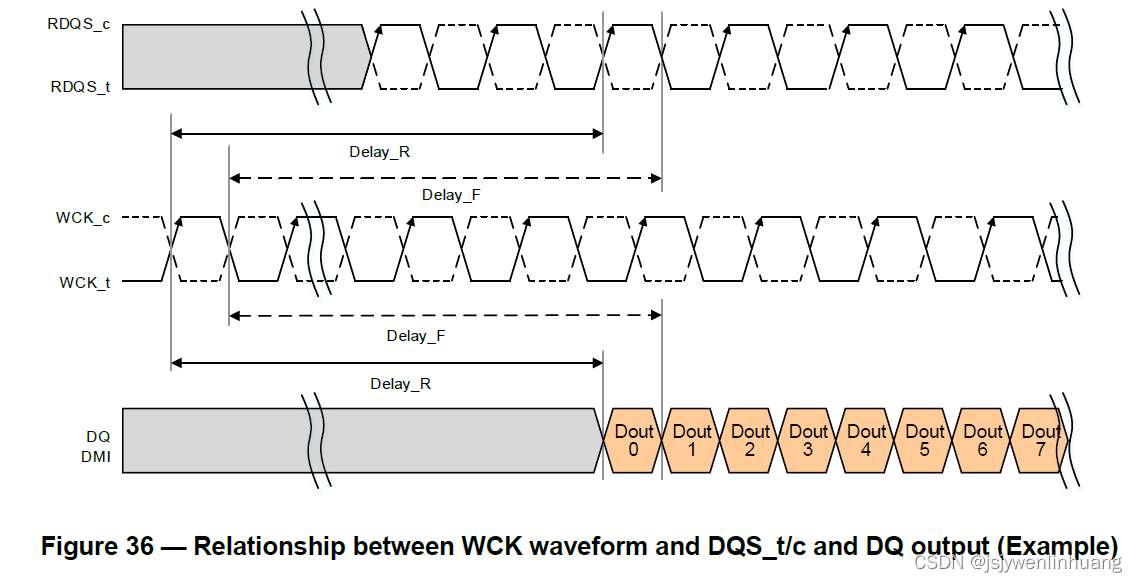

duty cycle adjuster (DCA) of LPDDR5 technology

The relationship between the DCA code change and delay time variation (Delay_R/F) only can define in a qualitative manner.