leveling专题

【转】DDR基础之Write_leveling简介

DDR基础之Write_leveling简介 2016年11月24日 09:31:37 雄关迈步 阅读数:2676 1)为了更好的提高信号完整性,DDR3存储模块采用了fly-by的拓扑结构。该拓扑应用于地址、控制、时钟线。Fly-by拓扑能有效减少stub的长度,但是较长的走线带来了CK-CK#与DQS-DQS#间的时延(由于CK-CK#的飞行时间,其到达每个DDR3颗粒的时间不同,而DQS

Cloud Design Pattern - Queue-Based Load Leveling(队列负载均衡)

1.前言 上一篇我们讨论了云计算设计模式之优先级队列模式,介绍了在消息队列中,按照消息的优先级来决定消息的被处理顺序.这一篇我们来讨论下如何基于队列的负载均衡模式. 2.概念 在传统的应用中,我们并没有使用消息队列,因为并发的请求量很小.在并发量很大的情况下,我们就需要使用消息队列来做一个缓冲,确保消息被处理的过程中不会并发太多而导致系统崩溃,所以,队列是一种负载均衡的机制,这种机制确保了系

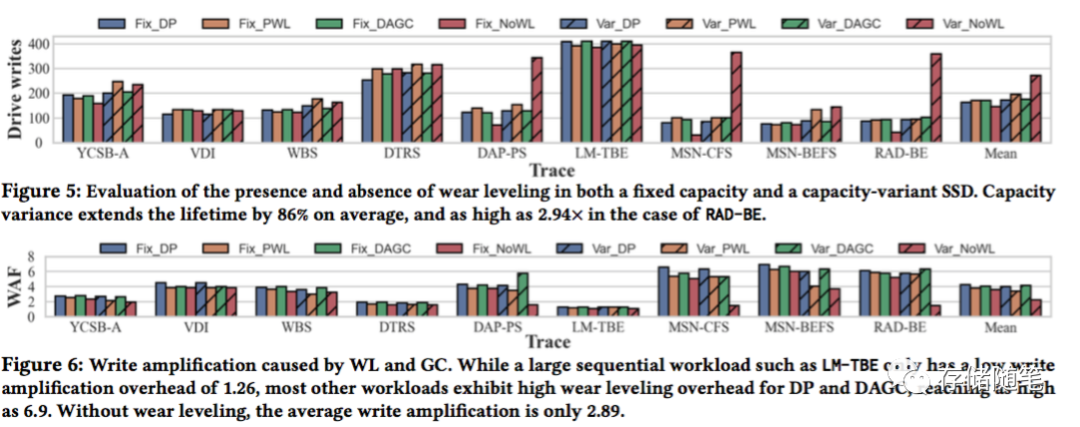

SSD Wear Leveling磨损均衡,并不是一直有效,甚至有负面作用!--part2

为了测试不同WL算法的性能影响,论文中在随机写压力下设定了两个参数:r,写IO比例;h,热数据比例。后续的测试基本采用的r/h=0.9/0.1的IO负载。 在这种工作负载压力下,PWL算法的在80遍写盘后的写放大增加了11.49,这个写放大已经非常严重了。 上图,根据CDF(Cumulative Distribution Function,即累积分布函数)曲线来看,在不同的工作

深入解析SSD Wear Leveling磨损均衡技术:如何让你的硬盘更长寿?

SSD的存储介质是什么,它就是NAND闪存。那你知道NAND闪存是怎么工作的吗?其实,它就是由很多个晶体管组成的。这些晶体管里面存储着电荷,代表着我们的二进制数据,要么是“0”,要么是“1”。NAND闪存原理上是一个CMOS管,有两个栅极,一个是控制栅极(Control Gate), 一个是浮栅(Floating Gate). 浮栅的作用就是存储电荷,而浮栅与沟道之间的氧化层(Oxide

DDR3基本概念6 - Write leveling(写入均衡)

为了提供更好的信号完整性,DDR3的memory controller可以使用write leveling来调整DQS差分对和CK差分对的相对位置,利用DQS差分对路径上的可调整延时来达成该目的。 对于简单的运用,比如on-board DDR memory,并且仅有一颗DDR内存的情况下可以考虑不需要做write leveling。 T型布线,如下图。该布线方式同步切换噪声(Si