hi3559av100专题

海思平台(hi3559av100)的pq_sample代码编译过程和执行过程

目录 1.文件目录结构 2.Makefile 3.源代码分析 3.1pq_sample.c文件 3.2pq_stream的注册过程: 3.3pq_control的实现过程: pq_sample的代码是用于海思的ISP在线调试的代码,本系统是采用的海思的异构方案(linux+liteos)的系统形式,pq_sample的代码是运行于a53上面的liteos系统中,实现了pq_

海思平台SDK中rootfs的文件添加和编译的操作(以hi3559av100为例)

由于项目需要,在系统启动后需要插入一些驱动程序以及运行一些应用程序。这就需要将所要执行的文件打包到根文件系统中,以便系统启动后可以运行。 一般我们在目录Hi3559AV100_SDK_V2.0.3.0/package/osdrv/中完整的编译了整个osdrv的情况下,yaffs2文件系统的编译工具mkyaffs2image100以及使用busybox制作的跟文件系统都应该是编译好了的,存放

【新版HI3559AV100开发注意事项(四)】

新版HI3559AV100开发注意事项(四) 三十、HI3559A参数中对输入分辨率限制的原因是? 答:分辨率限制有两个来源: 一个是时钟频率最高为600M,开启一拍两像素之后相当于1200M。你这个数据量太大了,61M像素又30帧那就需要1800M以上的时钟频率。假如降低分辨率用6000x6000=36M,30帧数据量只有1080M那是可以支持的。 另一个来源是图像处理模块设计支持的最大分辨率

新版HI3559AV100开发注意事项(三)

新版HI3559AV100开发注意事项(三) 十九、用的sdk是Hi3559V200_MobileCam_SDK_V1.0.1.5 播放AAC音频文件,adec->ao;adec的初始化里面包括了aaclc解码器的注册,可是在HI_MPI_ADEC_RegisterDecoder(&s32Handle, &stAac);出错了,错误代码为:0xA0188009 HI_ERR_ADEC_NOT_P

SLVS-EC接口的初步认识(以hi3559av100为例)

SLVS-EC 接口由 SONY 公司定义,用于高帧率和高分辨率图像采集,它可以将高速串行的数据转化为 DC(Digital Camera)时序后传递给下一级模块 VICAP(Video Capture)。 SLVS-EC 串行视频接口可以提供更高的传输带宽,更低的功耗,在组包方式上,数据的冗余度也更低。在应用中 SLVS-EC 接口提供了更加可靠和稳定的传输。 SLVS-EC 接口包含 PH

【复出Hi3559AV100 ultra-HD Mobile Camera SoC】

一、总体介绍 HI3559AV100是专业的8K Ultra HDMobile Camera SOC,它提供了8K30/4K120广播级图像质量的数字视频录制,支持多路Sensor输入,支持H.265编码输出或影视级的RAW数据输出,并集成高性能ISP处理,同时采用先进低功耗工艺和低功耗架构设计,为用户提供了卓越的图像处理能力。 Hi3559AV100支持业界领先的多路4K Sensor输入,

HI3516DV300/HI3519AV100/HI3559AV100 实现RTSP/RTMP视频流实时识别YOLOV3 识别速度14帧/S

本教程是基于yolov3在硬件实现硬件的实时视频处理! 不是SAMPLE中的处理单张图片照片! 未采用opencv库,数据处理全部采用硬件加速! 直接对摄像头数据直接进行图像识别! HI3516 识别速度 10帧/S HI3519 识别速度 14帧/S 教程目的: 在硬件实现视频流实时识别,将深度学习落地于实战项目中。 实现原理: VPSS 使用3路,部分芯片VPSS CH0 不支持缩小,为

【新版HI3559AV100开发注意事项(二)】

#新版HI3559AV100开发注意事项(二) 十一、请问海思HI3559AV100 SPC030资料里面的HI3559ADMEB_VER_C_PCB.pcb是用什么软件打开啊? 答:PADS VX 2.2 Altium designer 十二、hi3559级联问题请教 在SDK的文档中只看到了两块Hi3559板卡进行级联的操作。请问hi3559可以通过pcie与其他CPU级联吗? 答:

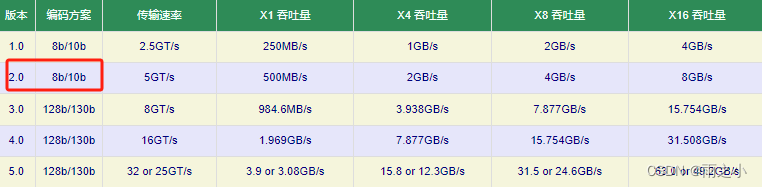

HI3559AV100和FPGA 7K690T的PCIE接口调试记录-续

上文https://blog.csdn.net/fzktongyong/article/details/134963814?spm=1001.2014.3001.5501 上一篇文中PCIE实测速度和理论计算有较大偏差,经过尝试后有所提升。 1、提升效果 1)、RC写操作,实测速度817MB/s(410+407) 先前为670MB