hcsl专题

差分逻辑电平 — LVDS、CML、LVPECL、HCSL互连

前言 首先了解差分逻辑电平、单端逻辑电平的基础知识 地址:常见的逻辑电平_常用的逻辑电平-CSDN博客 注: ECL >> PECL >> LVPECL演变; ECL速度快,驱动能力强,噪声小,但是功耗大,使用中需要负电源。为了简化电源,出现了PECL和LVPECL的输出模式。PECL电路速度快,驱动能力小,噪声小,高频。高功耗是PECL输出的主要缺点,且不同电平不能驱动

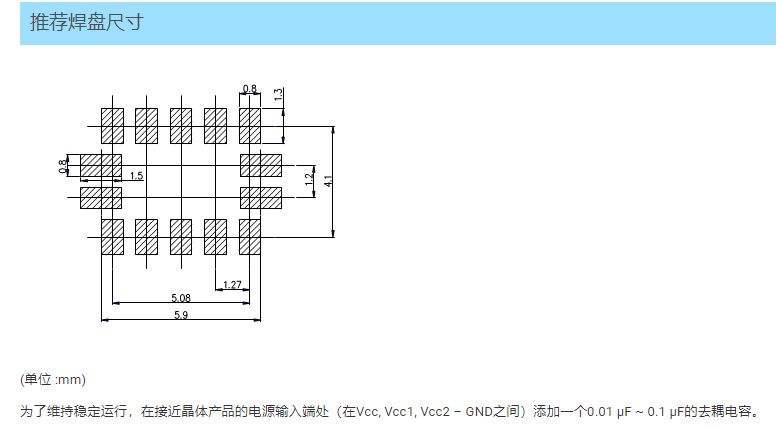

MG7050HAN 基于声表的差分多输出 晶体振荡器 (HCSL)

基于MG7050 HAN的声表差分多输出晶体振荡器(HCSL),采用两路或四路差分HCSL(高速电流驱动逻辑)输出,可以减少外部扇出缓冲区,特别适用于需要超低抖动、高频率范围内稳定工作的应用场合。其输出特性曲线超低抖动,最大相位抖动不超过0.3ps,非常适合对时钟信号的完整性有严格要求的系统。小体积晶振尺寸:7.0x5.0x1.6

普通时钟信号-TTL/CMOS LVPECL LVDS HCSL

1.TTL/CMOS 2.LVPECL Low Voltage Positive Emitter Coupled Logic 低电压正射极耦合逻辑 3.LVDS 4.HCSL Host Clock Signal Level 主机时钟信号电平