dphy专题

[RK3588-Android12] 调试MIPI-双通道-压缩屏(Video Mode/MIPI Dphy 8Lane/DSC 144HZ)

问题描述 被测屏幕:小米Pad6 分辨率:1800X2880 模式:Video Mode/MIPI Dphy 8Lane/DSC 144HZ PPS: 11 00 00 89 30 80 0B 40 03 84 00 14 01 C2 01 C2 02 00 01 F4 00 20 01 AB 00 06 00 0D 05 7A 06 1A 18 00 10 F0 03 0C 20 00 06

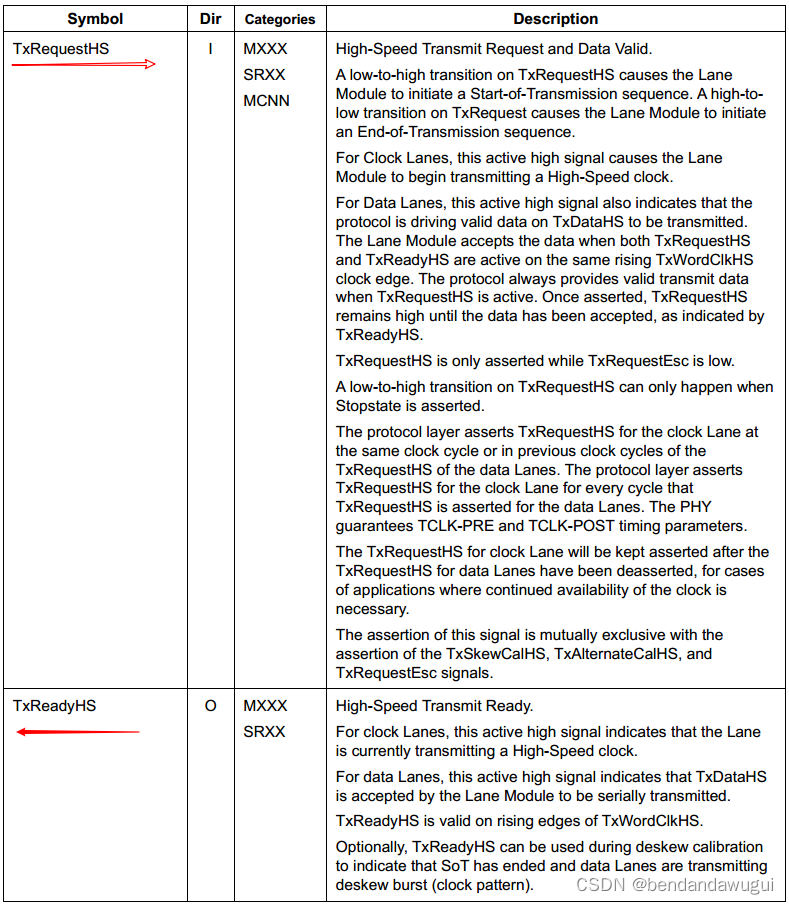

mipi DPHY学习记录

DPHY的内容很多,而且细节很多,我会一点一点的进行补充记录,今天要记录的是cdphy的LP-MODE数据传输的过程。 1:HS 和LP mode lane status 和 lane上的电压 HS mode时,差分线上的电压摆幅为200mv,LP mode时,差分线上的电压为1.2v 2:HS mode data Transmission start 在TX端,host contro

mipi DPHY学习记录

DPHY的内容很多,而且细节很多,我会一点一点的进行补充记录,今天要记录的是cdphy的LP-MODE数据传输的过程。 1:HS 和LP mode lane status 和 lane上的电压 HS mode时,差分线上的电压摆幅为200mv,LP mode时,差分线上的电压为1.2v 2:HS mode data Transmission start 在TX端,host contro

基于Xilinx ZYNQ和7 Serises FPGA的MIPI DPHY 接口实现分享

作者:Hello,Panda 这次分享一个在Xilinx FPGA实现MIPI DPHY接口的案例(包括CIS协议层)。截止目前为止,Xilinx仅在Ultrascale+及其以上版本的FPGA IO可直接支持MIPI 电平输入,其

DSI及DPHY的学习

DSI的物理层PHY只能是DPHY 本节讲述的DSI是V1.02.00---2010.6.28 从DSI V1.02开始DSI支持图像数据包RGB和YCbCr的传输,在此版本之前只支持RGB传输。 本节内容与CSI+CDPHY相同时 请参考: CSI2与CDPHY学习-CSDN博客 同时本节会做一些与CSI+CDPHY的比较 1 DSI的多lane分配与合并 2 DSI的长包格式

![[RK3588-Android12] 调试MIPI-双通道-压缩屏(Video Mode/MIPI Dphy 8Lane/DSC 144HZ)](https://img-blog.csdnimg.cn/direct/2ac86bc95b754720a4357ee834fd793c.png)