clb专题

TMS320F280049 CLB模块--输入输出连接(1)

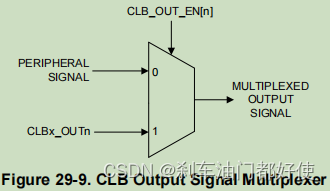

输入 下图是CLB外部输入框图,可以经其他外设或GPIO给到CLB X-BAR,然后给到CLB模块内部。 下面是CLB内部输入框图。可以看到CLB内部边界输入有3个来源:全局输入/本地输入/寄存器输入。 另外还可以选择同步/滤波等功能。 下图是信号选择的实例。 输出 下图是CLB的输出,可以看到CLB有8个输出,然后复制3份后向外输出,共24个对外输出。 输出信号多选

Xilinx FPGA底层逻辑资源简介(1):关于LC,CLB,SLICE,LUT,FF的概念

LC:Logic Cell 逻辑单元 Logic Cell是Xilinx定义的一种标准,用于定义不同系列器件的大小。对于7系列芯片,通常在名字中就已经体现了LC的大小,在UG474中原话为: 对于7a75t芯片,LC的大小为75K,6输入LUT的数量为75K/1.6,约为47K左右大小; 对于7k325t芯片,LC的大小为325K,6输入LUT的数量为325K/1.6,约为203K

阿里云的应用型负载均衡(ALB)、网络型负载均衡(NLB)、传统型负载均衡(CLB)区别

阿里云的应用型负载均衡(ALB)、网络型负载均衡(NLB)和传统型负载均衡(CLB)各自具有独特的特点和适用场景。以下是它们之间的主要区别: 定位与处理能力: 应用型负载均衡(ALB):主要面向应用交付,其七层处理能力强大。它特别适合处理HTTP、HTTPS和QUIC等应用层负载场景,具备超强的弹性及大规模应用层流量处理能力。此外,ALB提供了最高99.995%的SLA可用性保障。网络型负载均

【Qt 学习之路】Jetson Orin Nx CLB 开发套件上的 Qt 部署安装

文章目录 1、Jetson Orin Nx简介1.1、概述1.2、优势1.3、设计思路1.4、实现步骤1.5、应用领域1.6、实物图片 2、Qt 部署安装2.1、安装方法2.2、开发套件环境2.3、命令安装2.3.1、安装Qt Creator2.3.2、安装Qt默认库2.3.2.1、qt5-default安装遇到错误2.3.2.2、安装子包qtbase5-dev遇到两个依赖错误2.3.2.3

FPGA原理与结构(1)——可配置逻辑块CLB(Configurable Logic Block)

系列文章目录:FPGA原理与结构(0)——目录与传送门 一、什么是CLB 1、CLB简介 可配置逻辑块CLB(Configurable Logic Block)是xilinx系类FPGA的基本逻辑单元(在各系列中CLB可能有所不同,以下我们主要讨论Xilinx 7系类),是实现时序逻辑电路和组合逻辑电路的主要逻辑资源。 2、CLB的组成

Xilinx官方文档学习之7系列CLB资源解读(UG474)

Xilinx官方文档学习之7系列CLB资源解读(UG474) 一、写在前面二、CLB2.1 Slice(SliceM and SliceL)2.1.1 LUT2.2.2 触发器(Flip-Flop)2.1.2 DRAM(分布式RAM)2.1.3 移位寄存器2.1.4多路复用器4:1 MUX8:1 MUX16:1 MUX 2.1.5进位逻辑 三、写在后面 一、写在前面 FPG

UltraScale FPGA 可编程逻辑块(CLB)

写在前面 AMD Adaptive Computing Documentation Portal 本文为作者对AMD UltraScale FPGA可编程逻辑块的资源和设计方法的学习笔记,主要参考文献为AMD官方文档:UltraScale Architecture Configurable Logic Block User Guide(UG574)。官方文档链接已放在文章最前面,以供大家参考学