cic专题

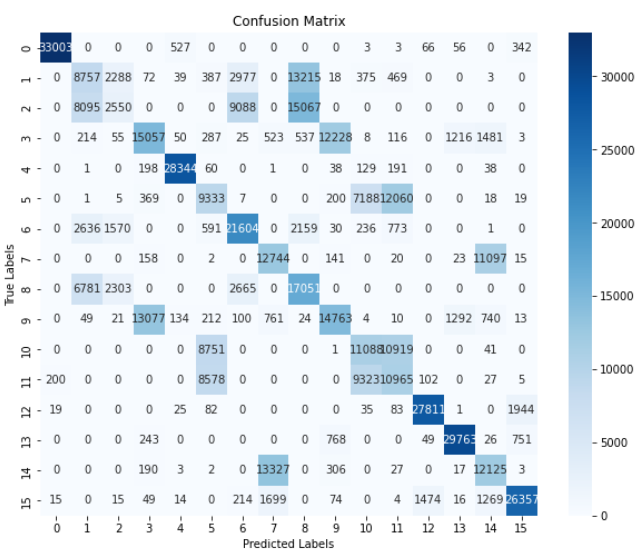

CIC-DDoS2019-Detection

CIC-DDoS2019 对CIC-DDoS2019数据集进行检测,本文提供了如下内容: 数据清洗与合并机器学习模型深度学习模型PCA,t-SNE分析数据,结果可视化 代码地址:[daetz-coder](https://github.com/daetz-coder/CIC-DDoS2019-Detection) 1、数据集加载 选择的数据集是这里的csv文件CIC-DDoS2019 (

ZYNQ实验--CIC插值滤波器实验

一、CIC滤波器介绍 CIC (Cascaded Integrator-Comb) 滤波器是一种常用的数字信号处理滤波器,主要用于降采样(decimation)和升采样(interpolation)操作。它具有简单的硬件实现、高效的运算速度以及适用于需要快速处理的应用场景等优点。半带滤波器具有较好的通带平坦特性,但考虑到面积和功耗,通常只能实现偶数倍的采样率变化。CIC滤波器在信号带宽为8分

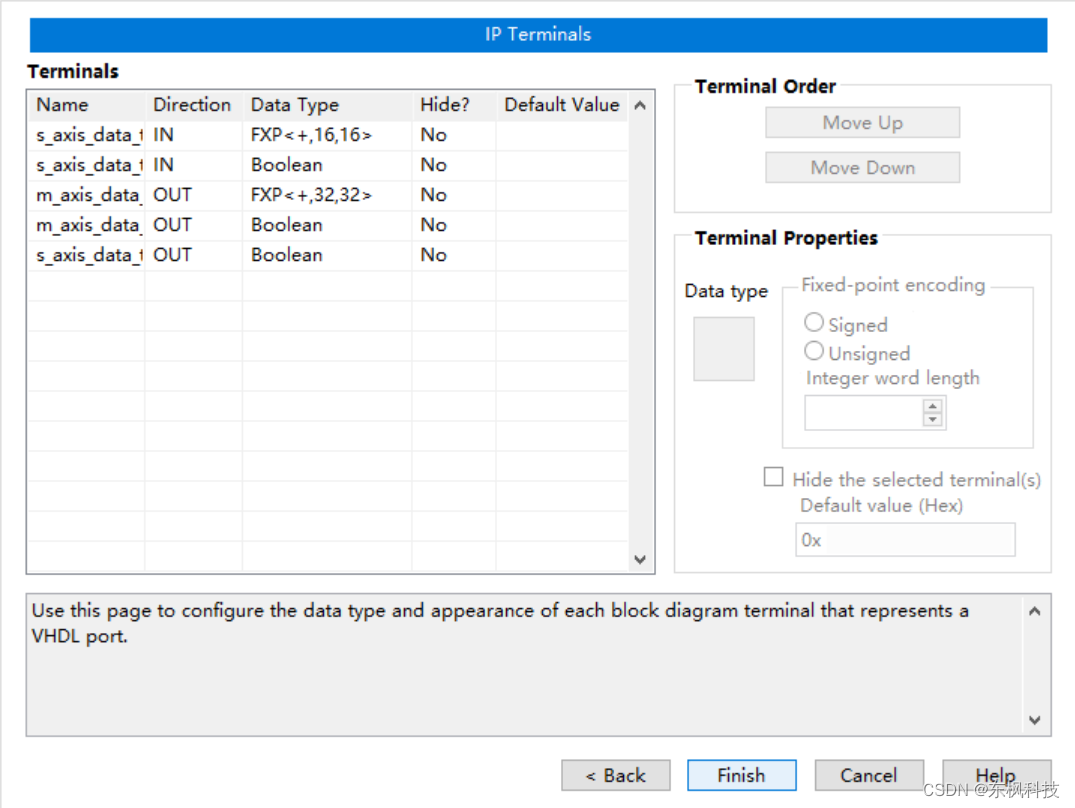

【LabVIEW FPGA】CIC滤波器

一、CIC滤波器应用概述 在通信数字信号上下变频时,经常会用到对数字信号的升采样和降采样,即通过CIC数字速率器实现变采样率。 二、滤波器IP 首先设置滤波器基本参数(filter specification) 滤波器类型(Filter Type):设置CIC滤波器模式为抽取Decimation或插值Interpolation;级联数目(Number Of Stages):设置级联的C

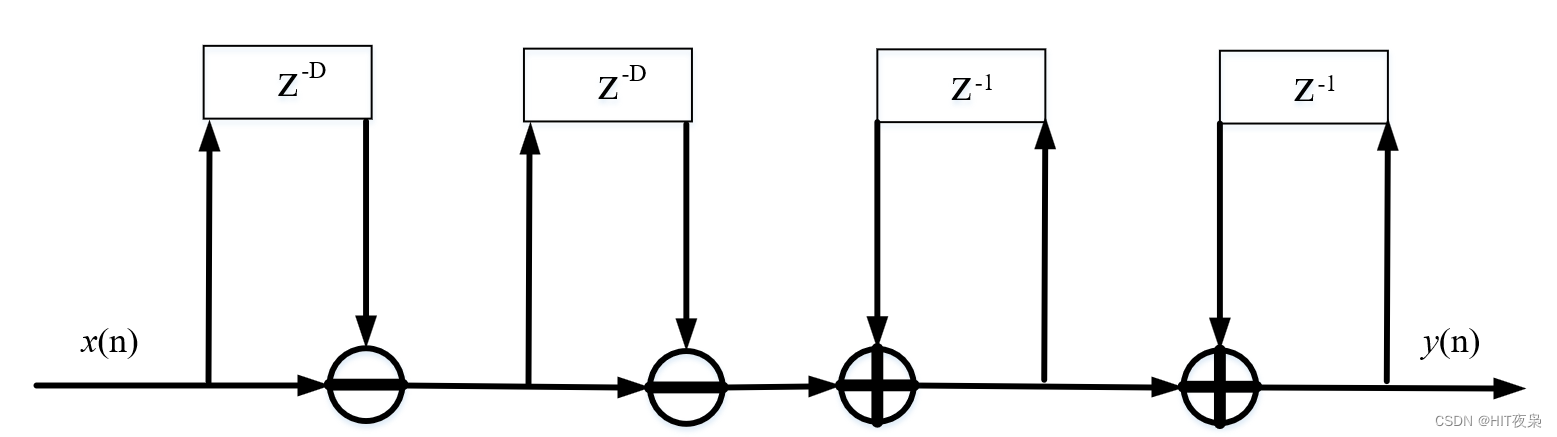

积分梳状滤波器CIC原理与实现

CIC(Cascade Intergrator Comb):级联积分梳状滤波器,是由积分器和梳状滤波器级联而得。滤波器系数为1,无需对系数进行存储,只有加法器、积分器和寄存器,资源消耗少,运算速率高,实现简单,可实现高速滤波,常用在输入采样率最高的第一级。 (1)应用背景 CIC滤波器是一种数字信号处理中常用的滤波器结构,主要用于降低采样率。它在应用中有一些特定的背景和优势:

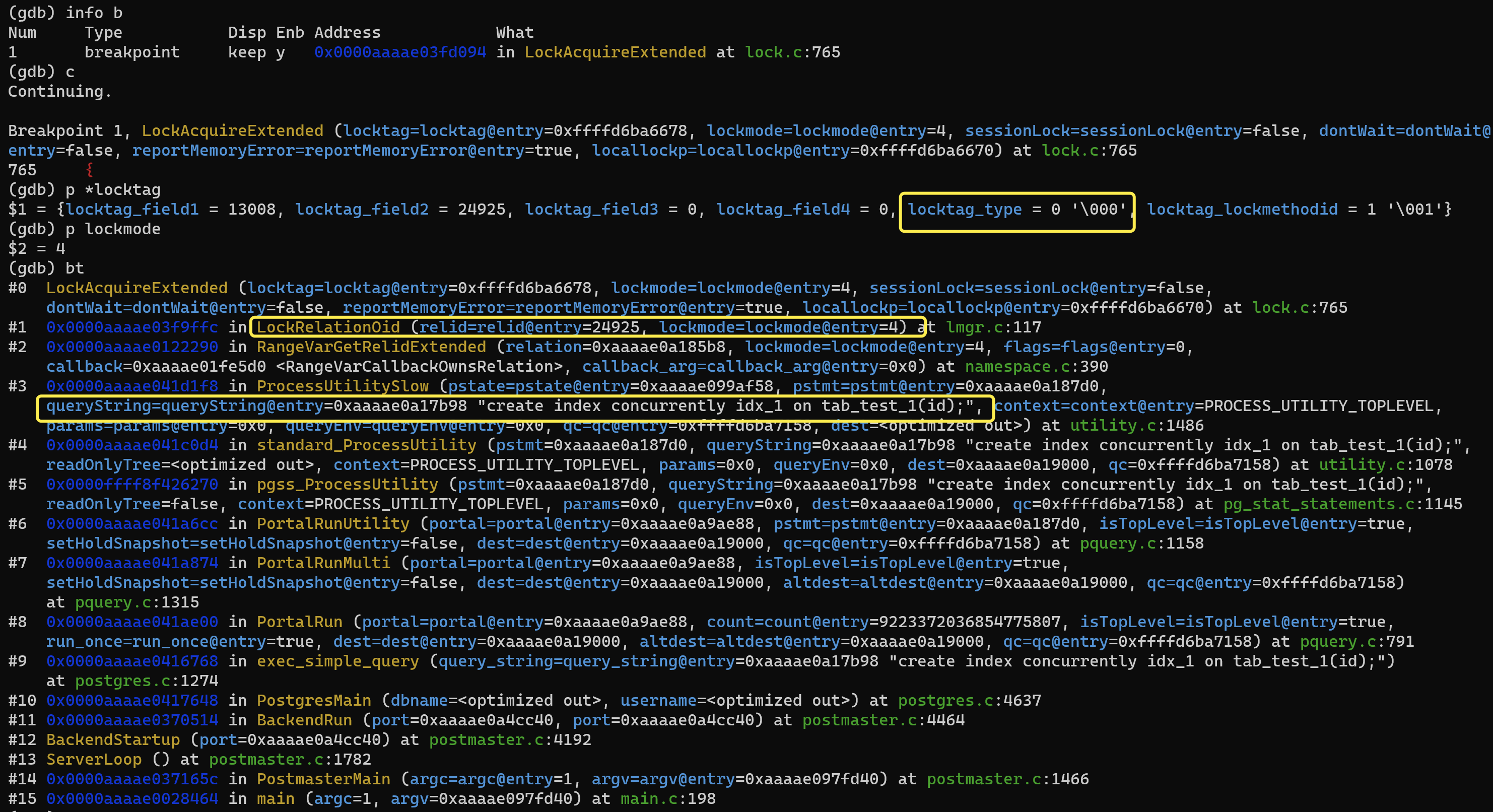

【PostgreSQL在线创建索引(CIC)功能的锁分析以及使用注意】

前一篇文章提到了普通创建索引会阻塞DML操作 PostgreSQL创建索引的锁分析和使用注意 而PostgreSQL里可以使用create index concurrently 在线创建索引(CIC)功能,降低创建索引在表上申请的锁的级别,ShareUpdateExclusiveLock级别的锁和RowExclusiveLock不冲突,不会阻塞表上的DML操作。 1.1 在线创建索引(CIC

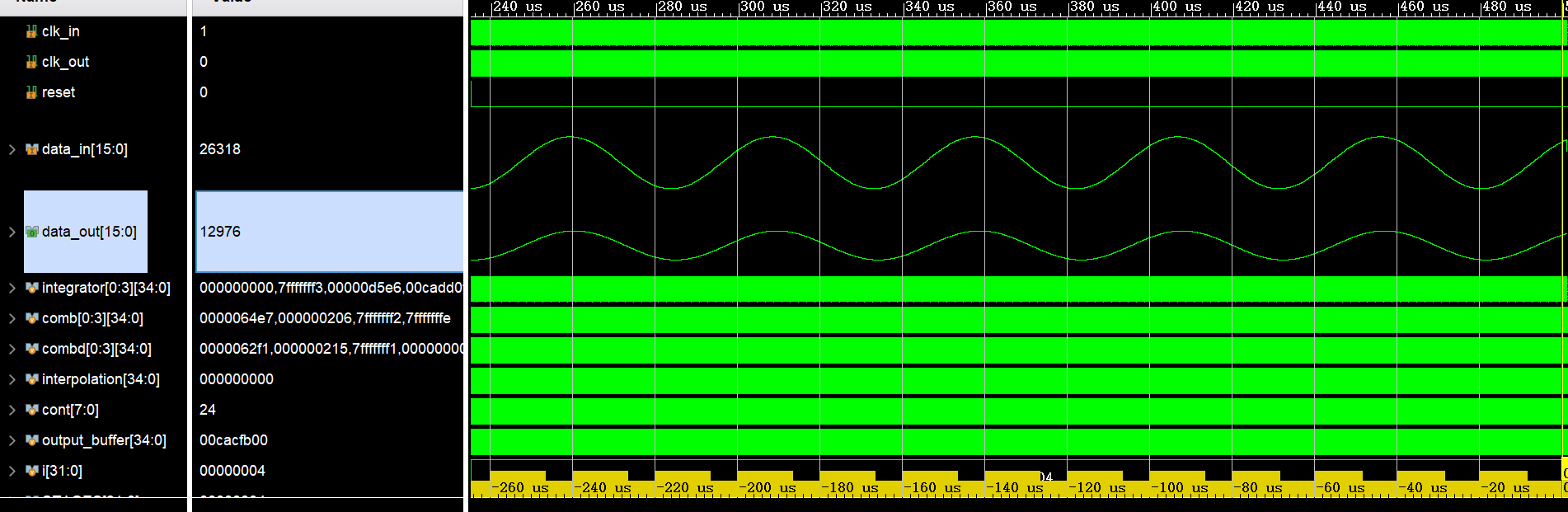

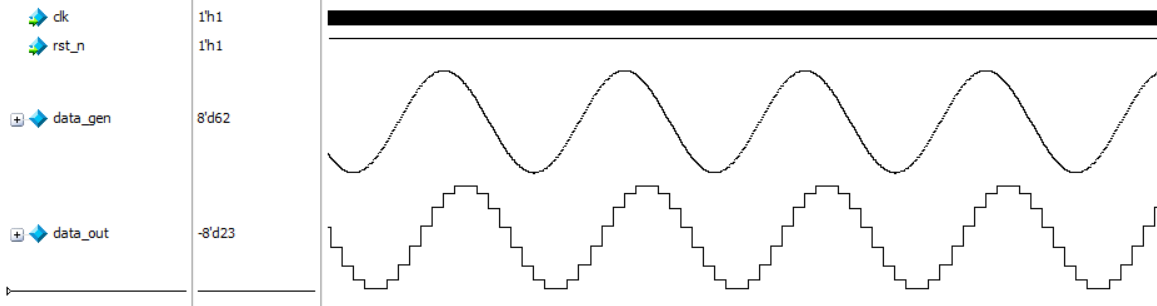

孩子都能学会的FPGA:第二十六课——用FPGA实现CIC抽取滤波器

(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家

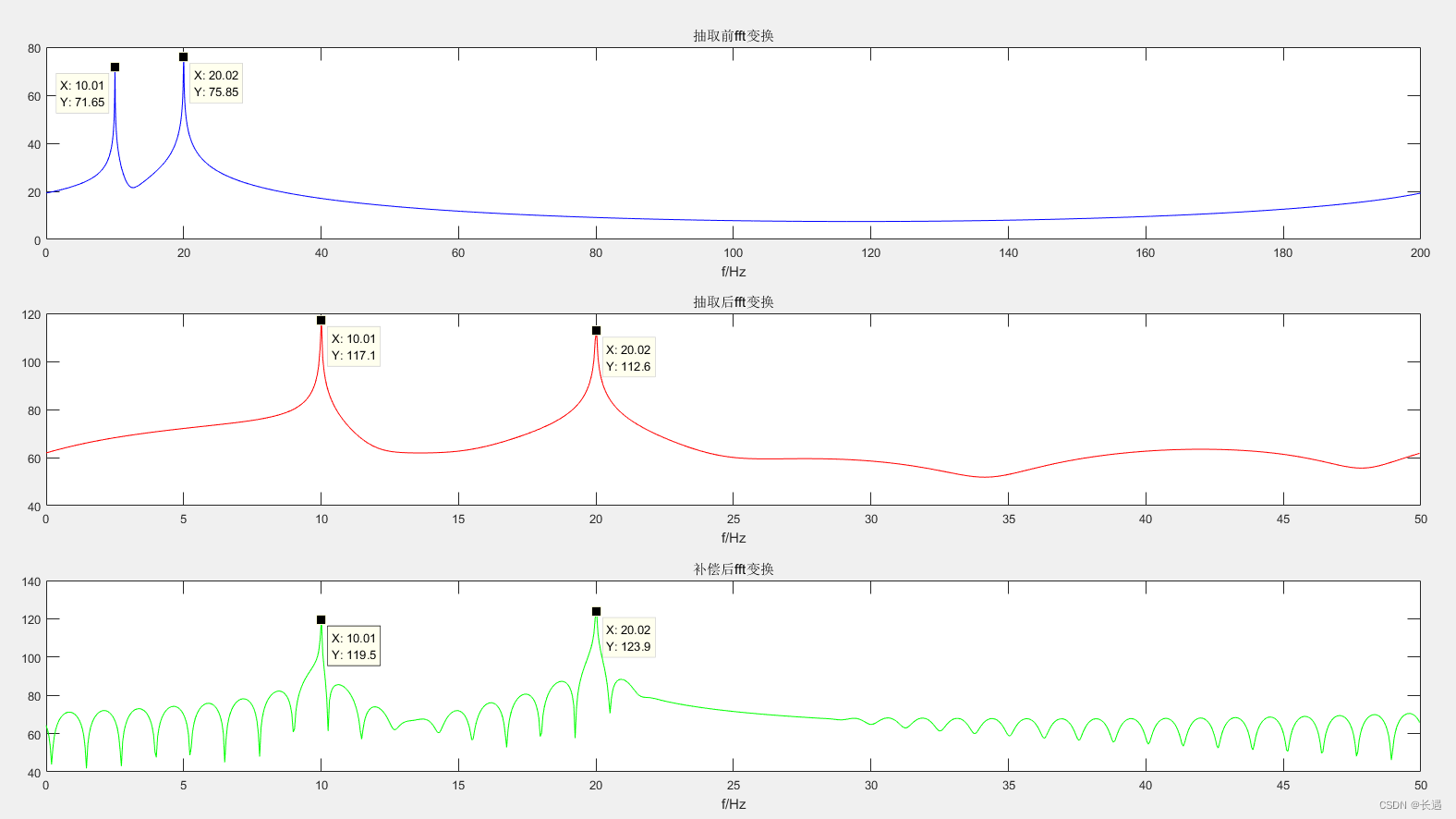

CIC滤波器的matlab仿真与实现

CIC滤波器的matlab仿真与实现 介绍 在数字信号处理中,由于后级硬件如FPGA的处理速度无法跟上前级ADC的采样速度,因此需要对ADC的采样数据进行降速处理,也就是对采样数据进行抽取,简单的抽取描述就是对其中连续几个点取一个点进行处理。 由抽取理论知识可以知道,抽取相当于对时域做压缩,相应的就会对频谱做扩展,同时由于采样信号都是离散的,因此反映在频谱上会有一连串的延拓频谱。这样抽取后可能