aval专题

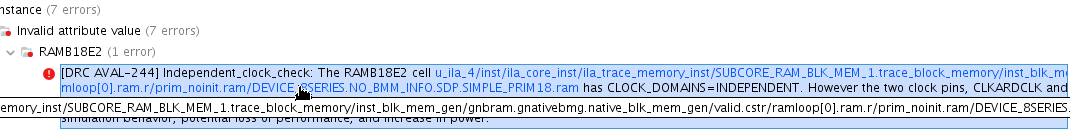

vivado bit生成报 DRC AVAL-244

经常在添加Debug Core ILA 后会遇到这个问题,字面意思就是说“这个调试ram需要独立的时钟CLKARDCLK和CLKBRWCLK,但实际DRC时发现这两个时钟是一样的。”虽然不太明白,但可以看到问题定位在u_ila_4模块,打开debug页面,确认下u_ila_4模块所用的采样时钟。 第一步:先把Messages的Critial waring/Warning过一遍,把代码里的b