本文主要是介绍CSAPP笔记——第四章处理器结构,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

Instruction Set Architecture

Programmer-Visible State

Y86-64 Instructions

Instruction Encoding

MOV

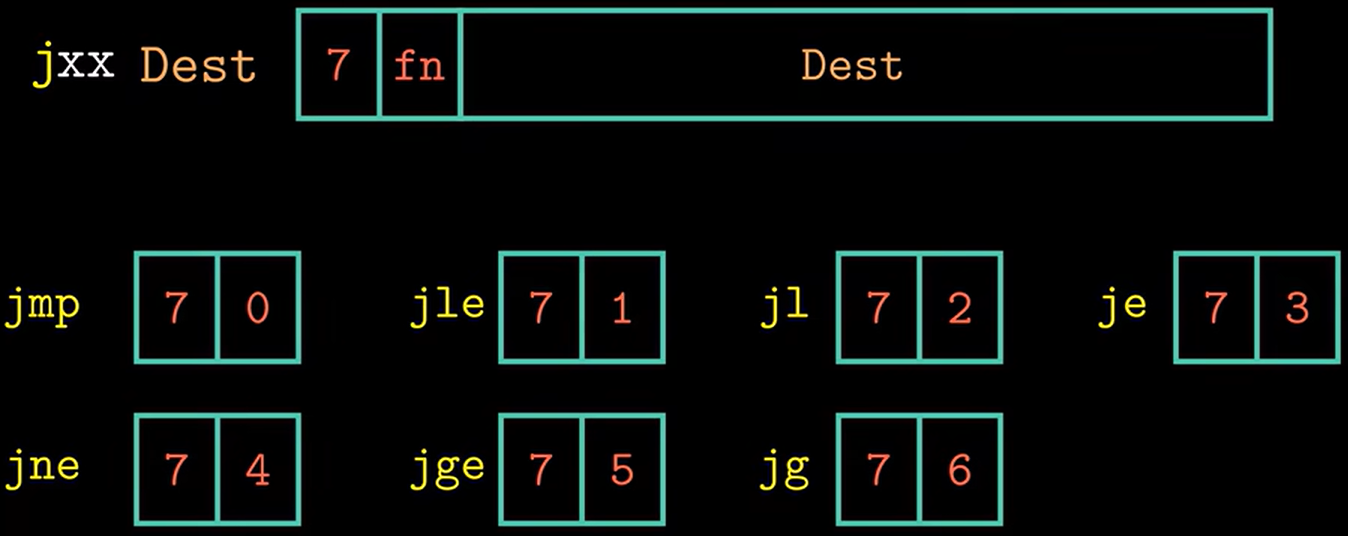

JMP

其他通用指令

指令集翻译

Y86-64 Exceptions

数字电路与处理器设计

CPU内部的处理器布局

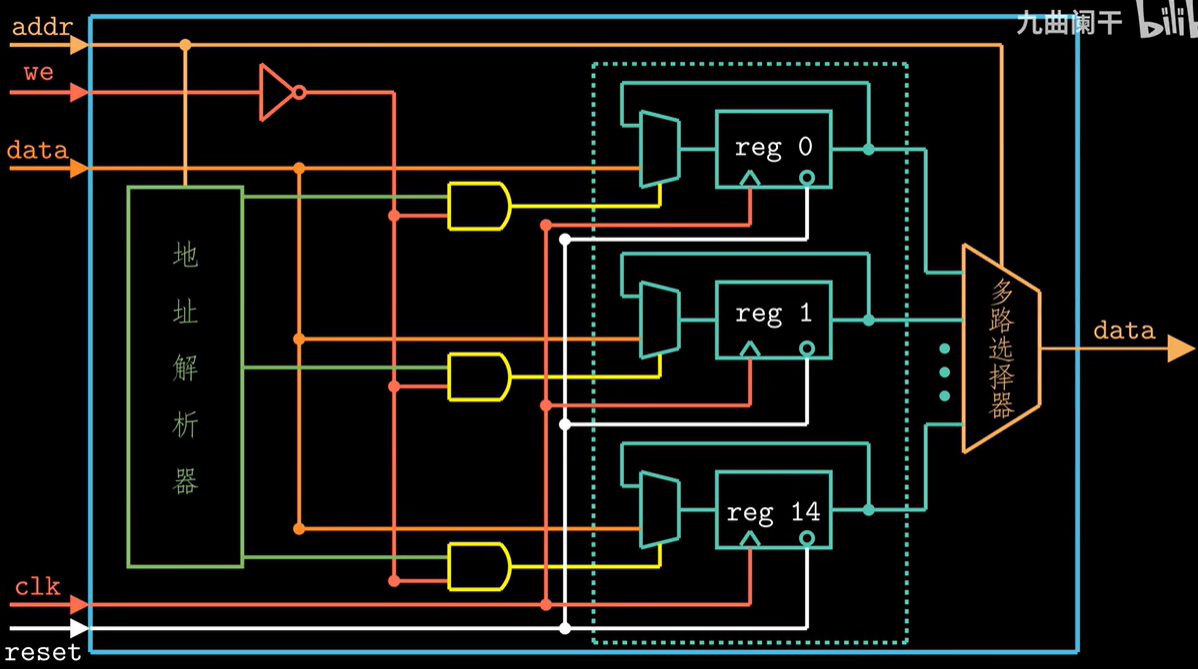

这是寄存器文件内部的详细实现

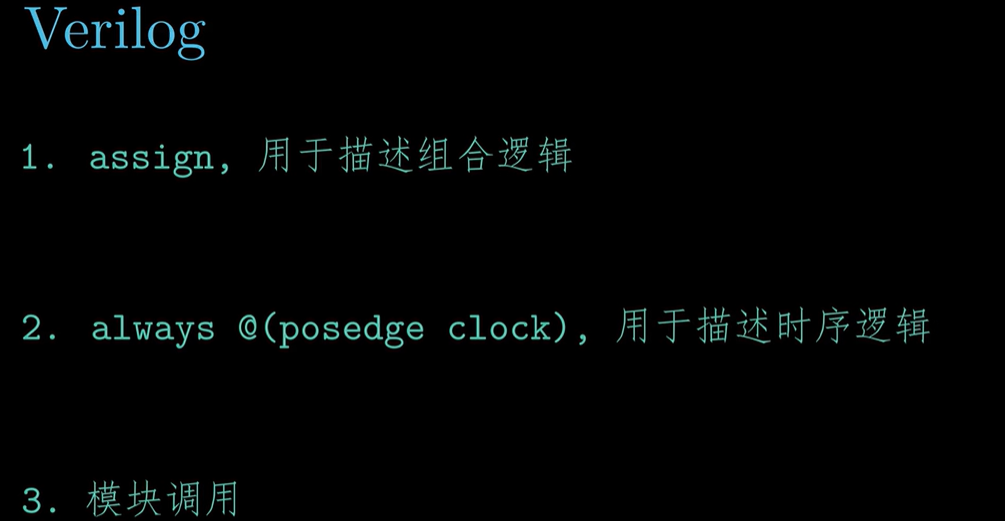

verilog只用下面这三种语句就全够了

Y86-64的顺序实现

Organizing Processing into Stages

rmmovq %rsp, 100(%rbx)指令执行详细解释

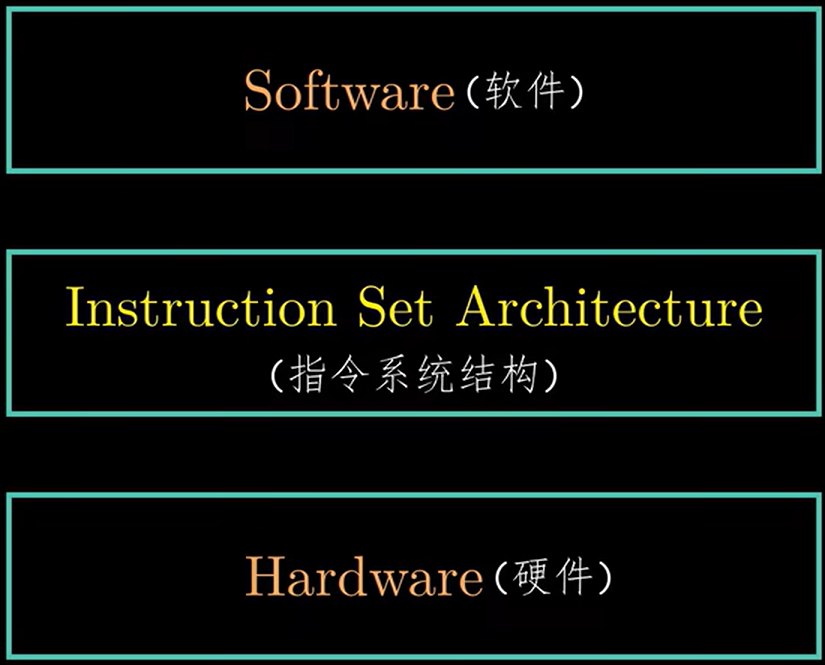

Instruction Set Architecture

指令系统结构

指令集是计算机的软件和硬件的接口,本章节自定义一个类似于X86的处理器——Y86。

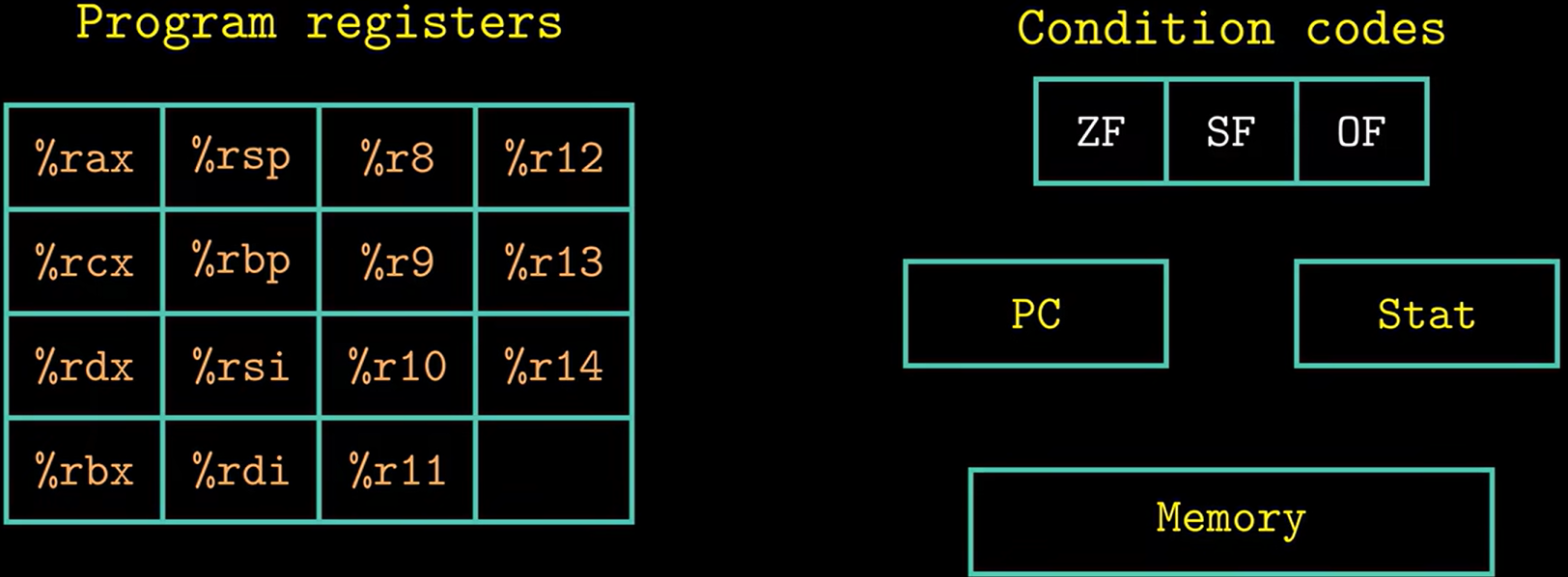

Programmer-Visible State

程序员的可见状态

这里的程序员可以是写代码的人,也可以是用汇编代码产生机器代码的编译器。

可见状态是指每条指令都会去读取或者修改处理器的某些部分

指令系统

Y86-64 Instructions

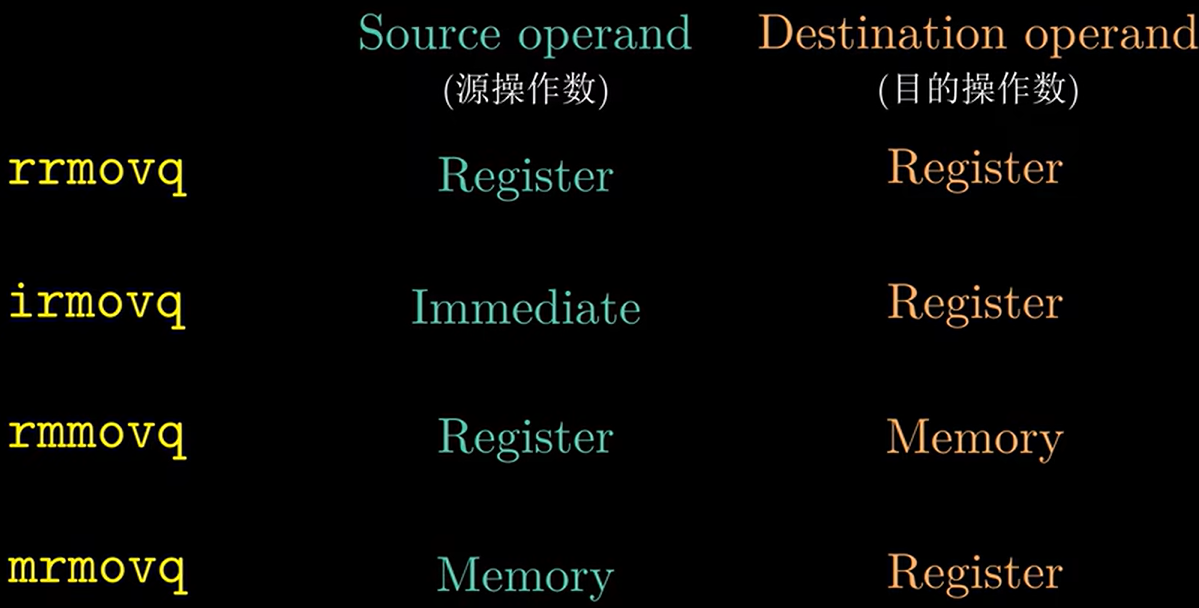

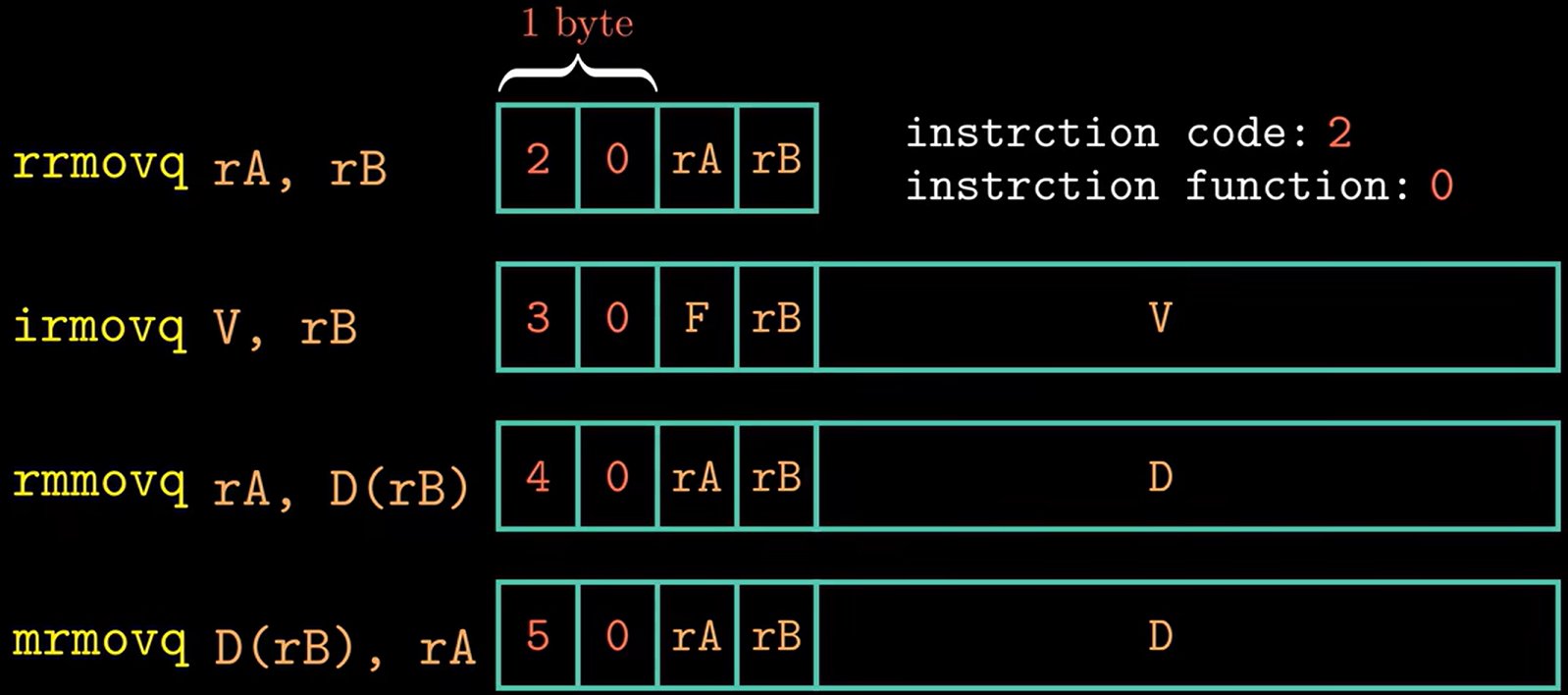

下面对数据传送指令进行编码

Instruction Encoding

指令编码——

低8位表示指令类型,其中低4位表示指令代码,高4位表示指令功能。

如果还有寄存器的操作,则会再加上一个字节,表示寄存器指示符字节。用来指定一个或者两个寄存器。

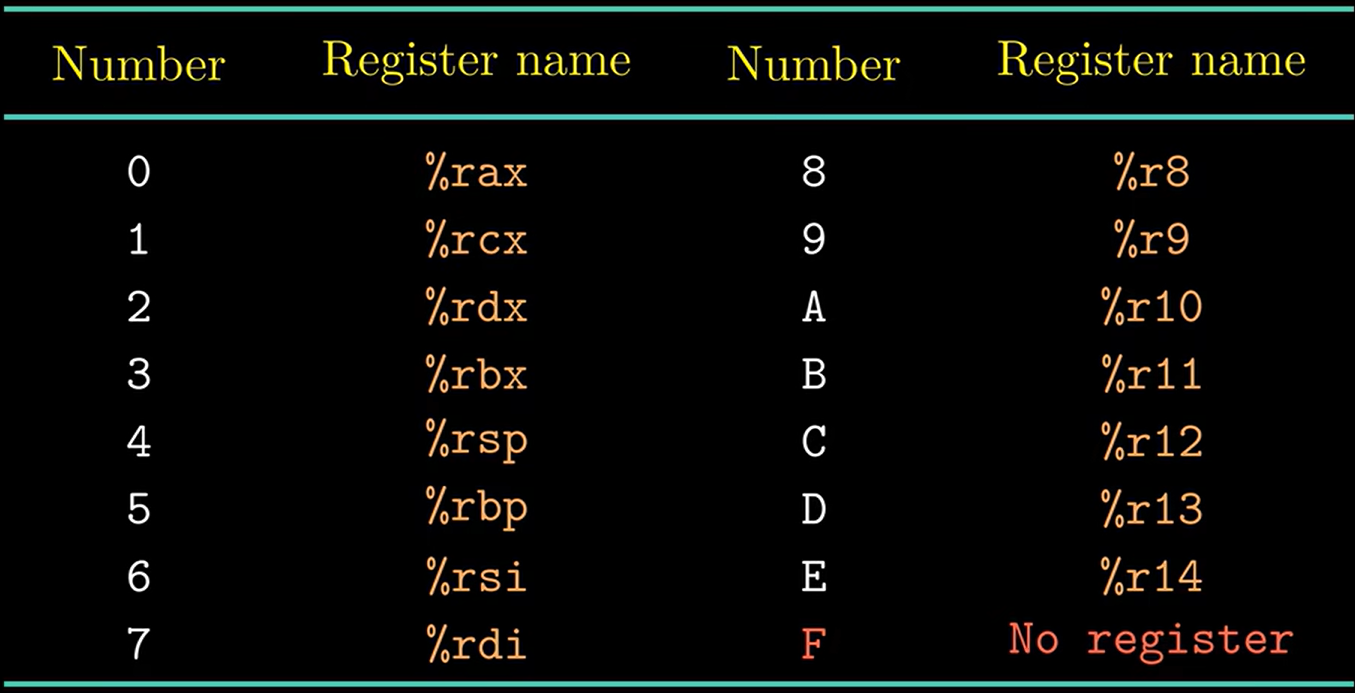

所以这里还需要对寄存器进行编码,如下:

MOV

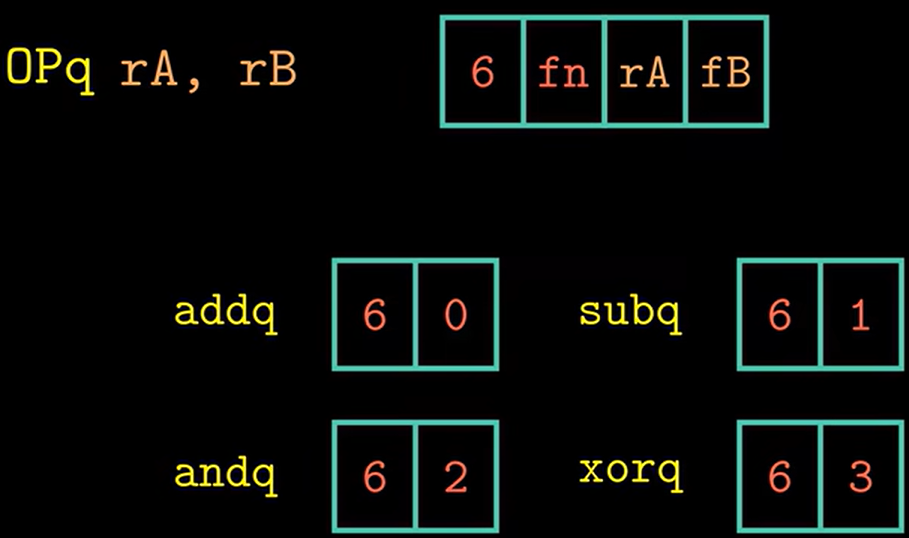

这是整数操作的4条指令代码:指令类型相同但是指令功能不同

JMP

其他通用指令

综上所述,Y86的指令集就定义完成了。通过以上,我们可以将Y86的汇编代码翻译成二进制代码表示。

指令集翻译

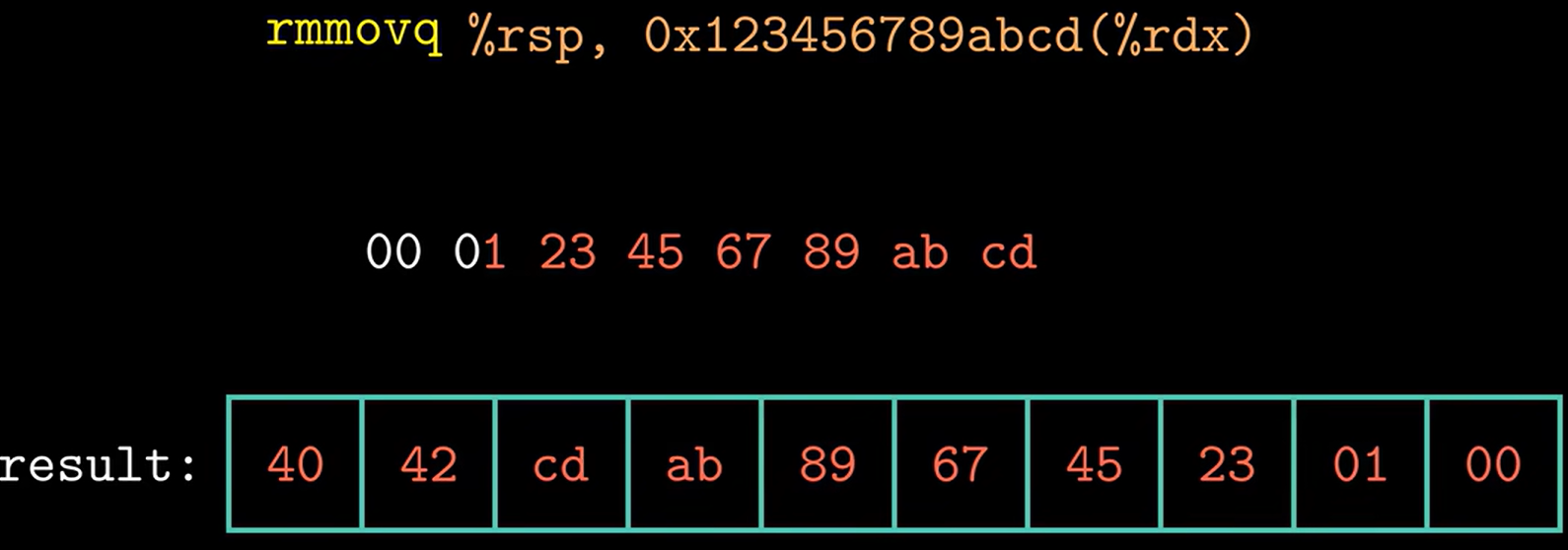

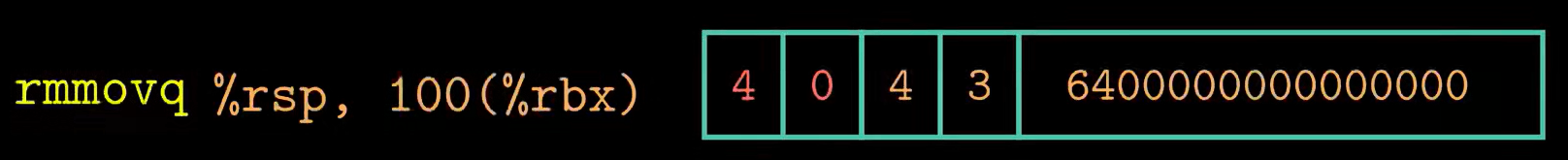

因为rmmovq指令对应的类型及功能代码是40,寄存器%rsp对应的指令编码是42,由于Y86采用小端法表示,所以这里的偏移量需要反序,最后的长度为10字节的二进制指令表示如图:

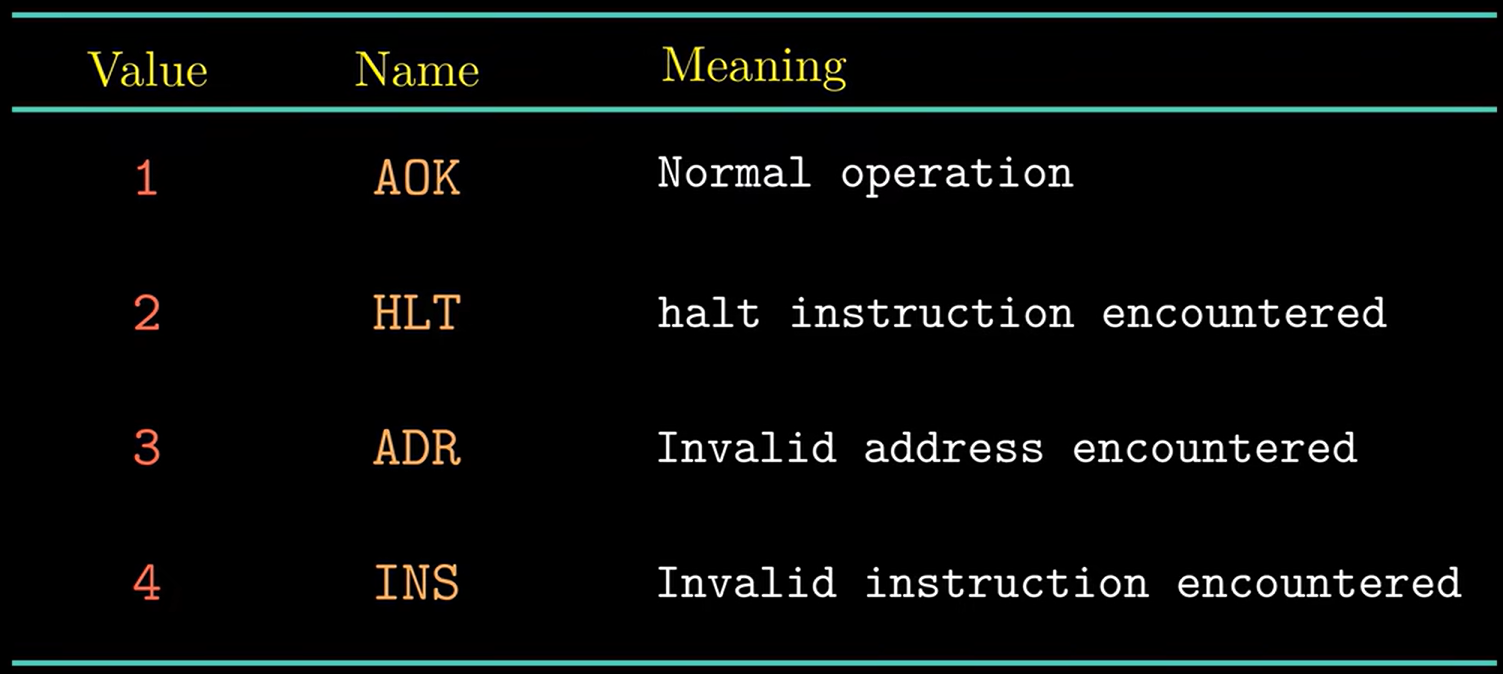

Y86-64 Exceptions

各种指令执行状态如下:

数字电路与处理器设计

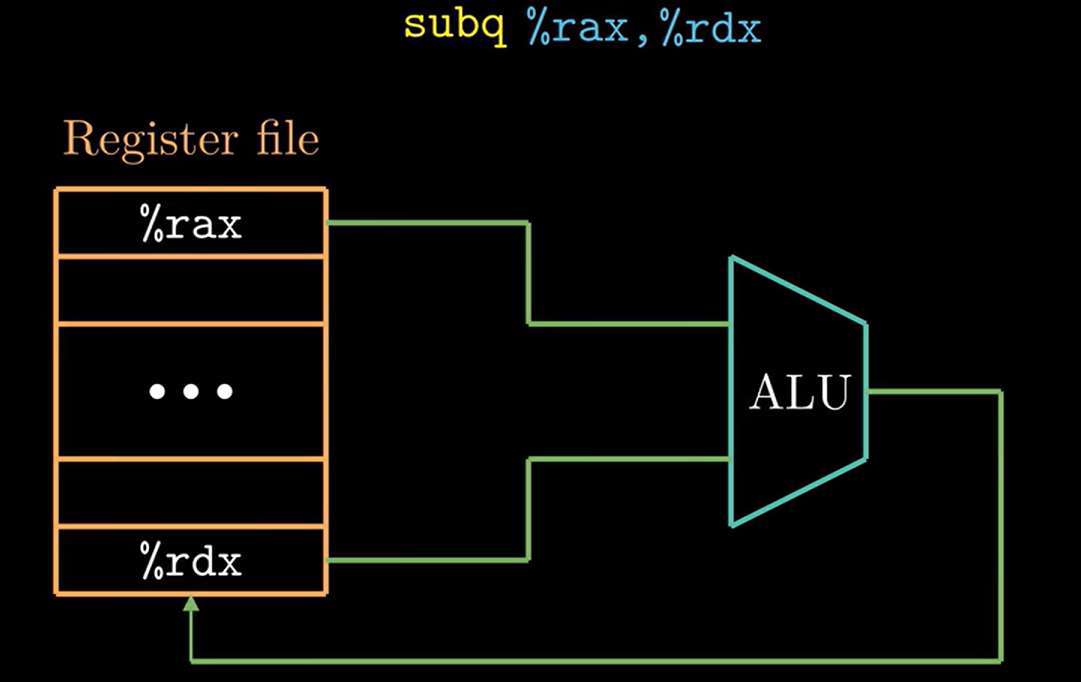

通常我们将寄存器集合称为寄存器文件,或者寄存器堆。

CPU内部的处理器布局

本期视频,以寄存器文件为例,通过剖析他的具体实现,来阐述处理器设计与数字电路之间的关系。

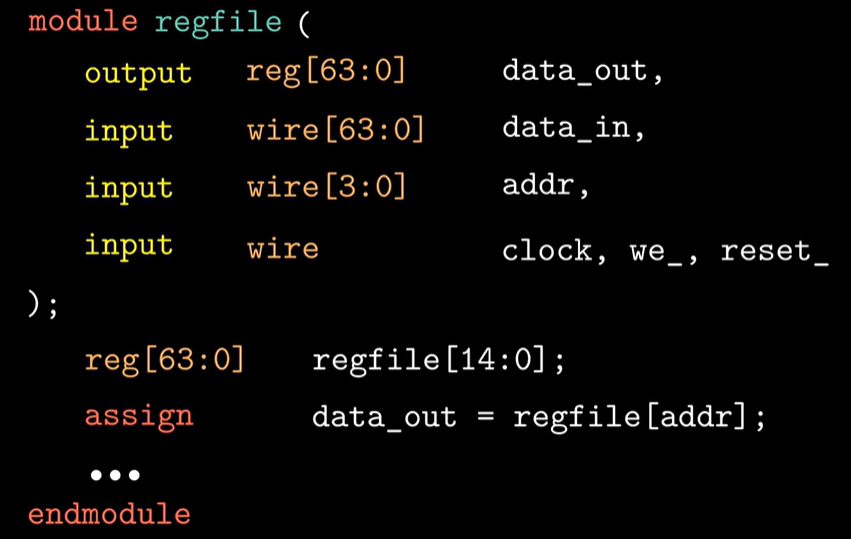

上面的寄存器文件实现可以用这个verilog代码片段实现

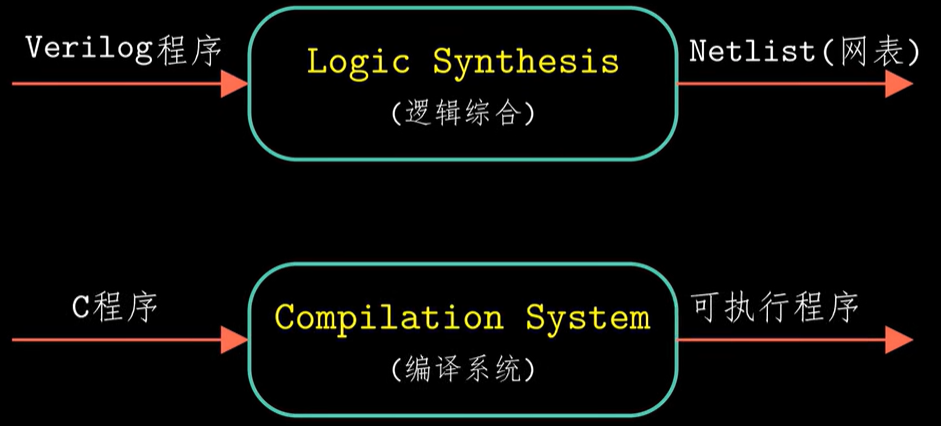

关于verilog与C语言类比

这是寄存器文件内部的详细实现

verilog只用下面这三种语句就全够了

Y86-64的顺序实现

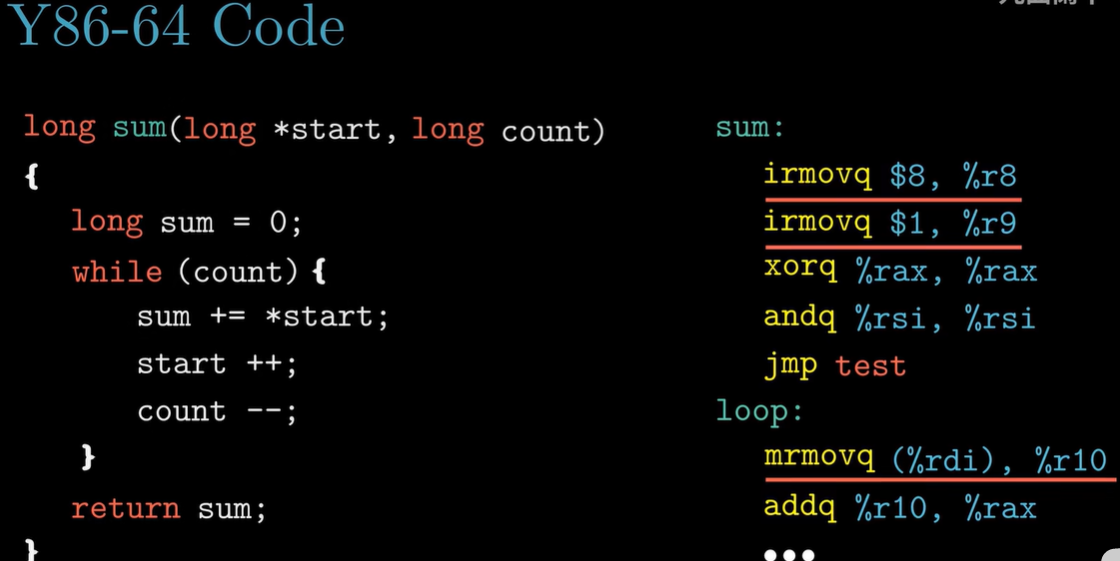

如图C语言代码翻译成汇编代码:

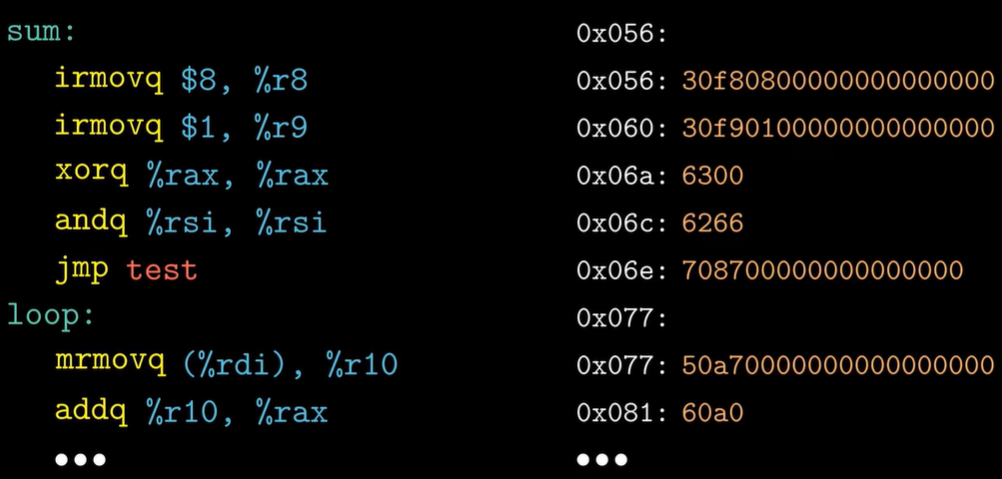

如图汇编代码翻译成能够运行在Y86处理器上的机器码

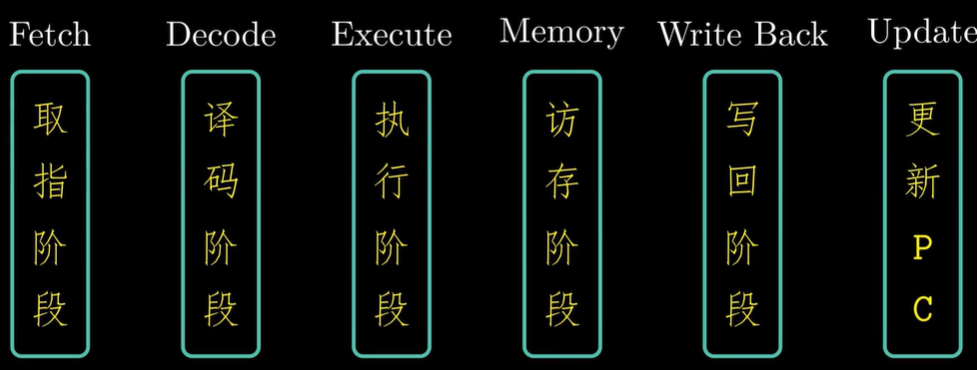

Organizing Processing into Stages

按阶段组织处理器运行过程

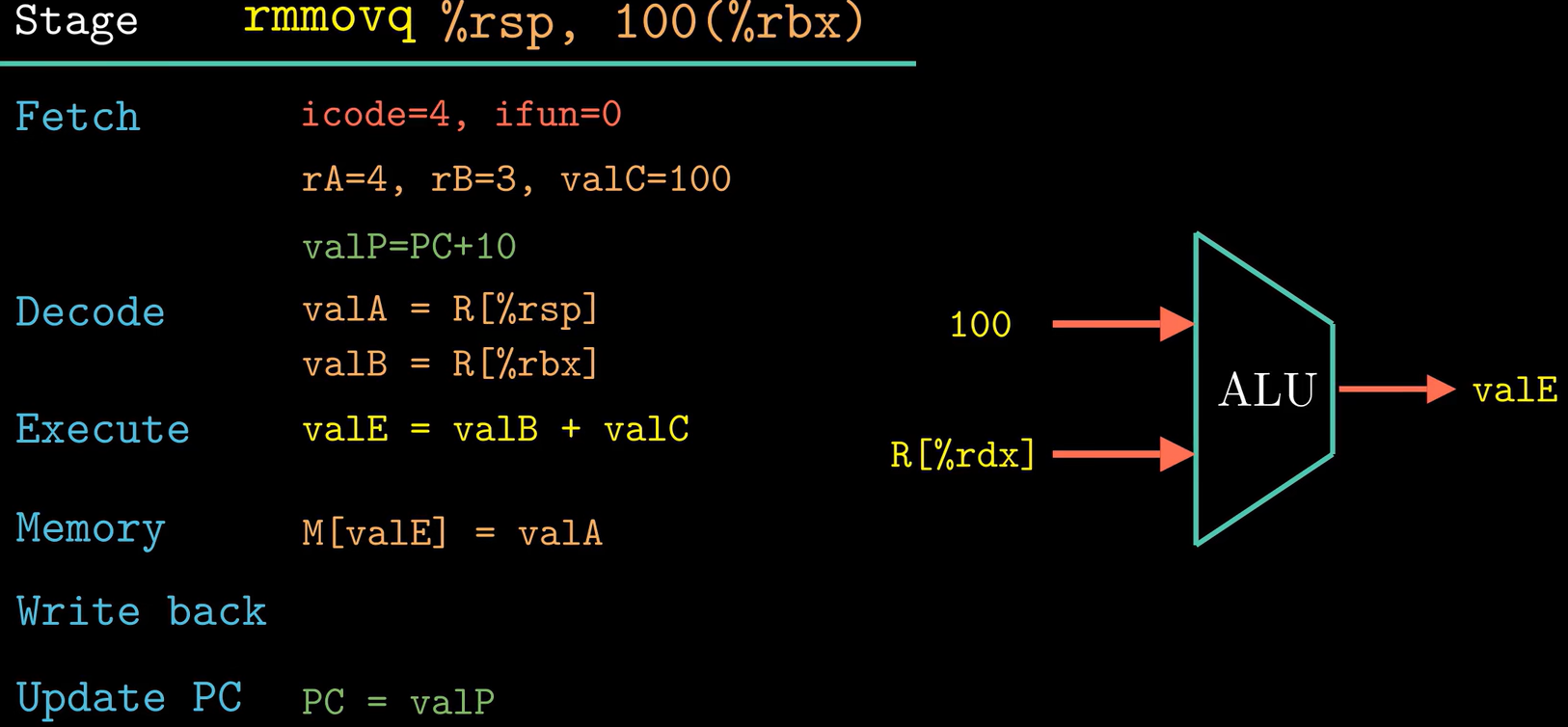

rmmovq %rsp, 100(%rbx)指令执行详细解释

例子——指令 rmmovq %rsp, 100(%rbx) 执行的全过程如下:

1.取指阶段

这里的指令长度——指令类型与指令功能占一个字节,寄存器编码占一个字节,地址偏移量占8个字节(64位),共10字节

2.译码阶段根据寄存器指示符来读取寄存器的值,并设为valA、valB

3.重点:执行阶段——

ALU根据偏移量和基址寄存器来计算访存地址 valE = valB + valC

4.访存阶段将寄存器%rsp的值写入地址ValE之中

5.没有涉及写回阶段

6.最后更新PC

这篇关于CSAPP笔记——第四章处理器结构的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!