本文主要是介绍FSMC的NOR Flash/PSRAM 控制器功能介绍(STM32F4),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

概述

1 FSMC支持的类型

1.1 信号类型概述

1.2 FSMC的应用

2 外部存储器接口信号

2.1 I/O NOR Flash

2.2 PSRAM/SRAM

3 支持的存储器和事务

4 通用时序规则

5 NOR Flash/PSRAM 控制器异步事务

5.1 模式 1 - SRAM/PSRAM (CRAM)

5.2 模式 A - SRAM/PSRAM (CRAM) OE 切换

5.3 模式 D - 扩展地址异步访问

5.4 复用模式 - 复用异步访问 NOR Flash

5.5 异步访问中的 WAIT 管理

概述

本文主要讲述FSMC的NOR Flash/PSRAM 控制器功能,包括FSMC支持的信号类型以及应用方法,还介绍外部接口信号的特性、存储器类型,以及控制模式等类型。

1 FSMC支持的类型

1.1 信号类型概述

FSMC 会生成适当的信号时序,以驱动以下类型的存储器:

● 异步 SRAM 和 ROM

— 8 位

— 16 位

— 32 位

● PSRAM( Cellular RAM)

— 异步模式

— 突发模式

— 复用或非复用

● NOR Flash

— 异步模式或突发模式

— 复用或非复用

1.2 FSMC的应用

FSMC 会为每个存储区域输出唯一的片选信号 NE[4:1]。所有其它信号(地址、数据和控制)均为共享信号。

对于同步访问, FSMC 只有在读/写事务期间才会向所选的外部器件发出时钟 (CLK)。 HCLK时钟频率是该时钟的整数倍。每个存储区域的大小固定,均为 64 MB。

每个存储区域都通过专用的寄存器进行配置。

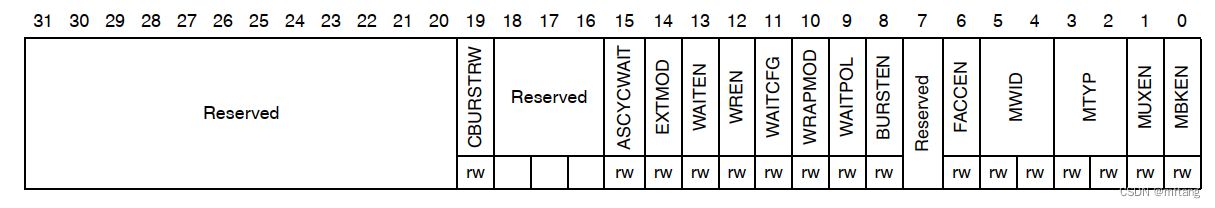

NOR/PSRAM 控制寄存器

NOR/PSRAM 控制寄存器必须按字( 32 位)进行访问。

SRAM/NOR-Flash 片选控制寄存器 1..4 (FSMC_BCR1..4)

SRAM/NOR-Flash chip-select control registers 1..4

偏移地址: 0xA000 0000 + 8 * (x — 1), x = 1...4

复位值: 0x0000 30DX

该寄存器包含每个存储区域的控制信息,用于 SRAM、 ROM 和异步或突发 NOR Flash。

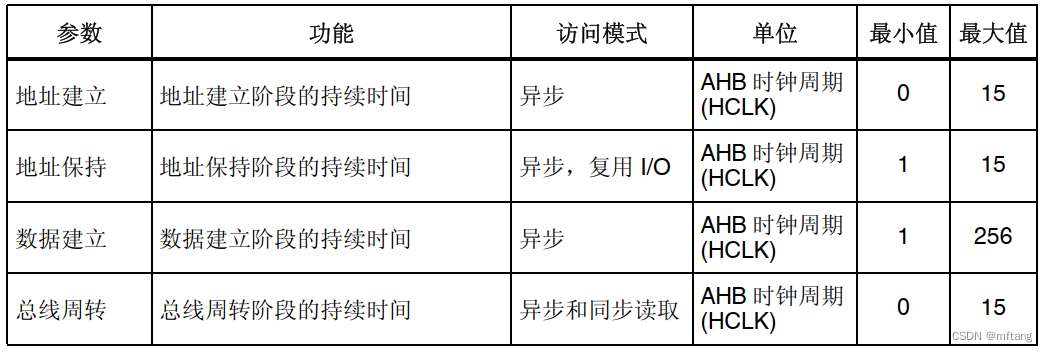

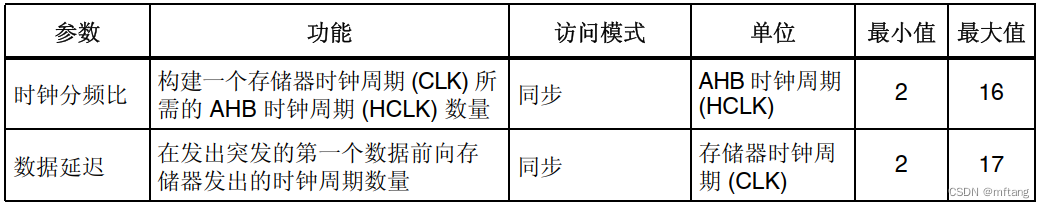

存储器的可编程参数包括访问时序和对等待管理的支持(用于在突发模式下访问 NOR Flash 和 PSRAM)。

NOR/PSRAM 的可编程访问参数

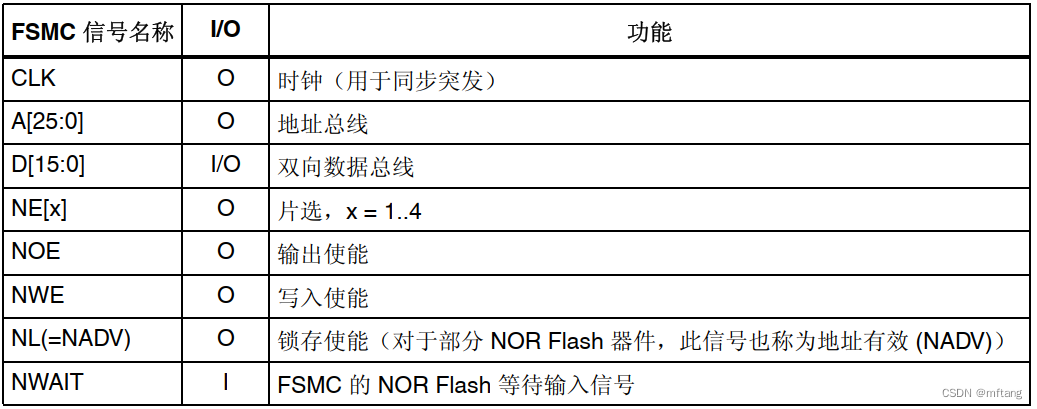

2 外部存储器接口信号

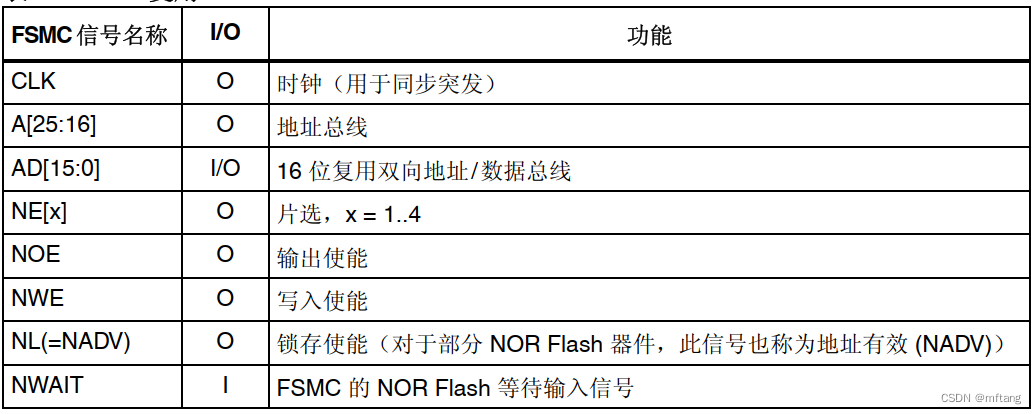

2.1 I/O NOR Flash

1) 非复用 I/O NOR Flash

NOR Flash 存储器采用 16 位字寻址。最大容量为 512 Mb( 26 个地址线)。

2)复用 I/O NOR Flash

NOR-Flash 存储器采用 16 位字寻址。最大容量为 512 Mb( 26 个地址线)。

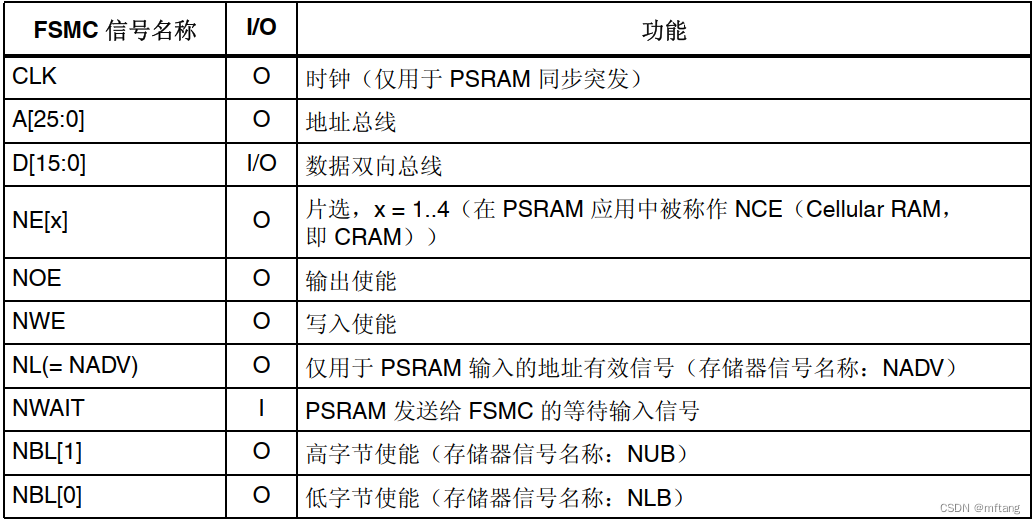

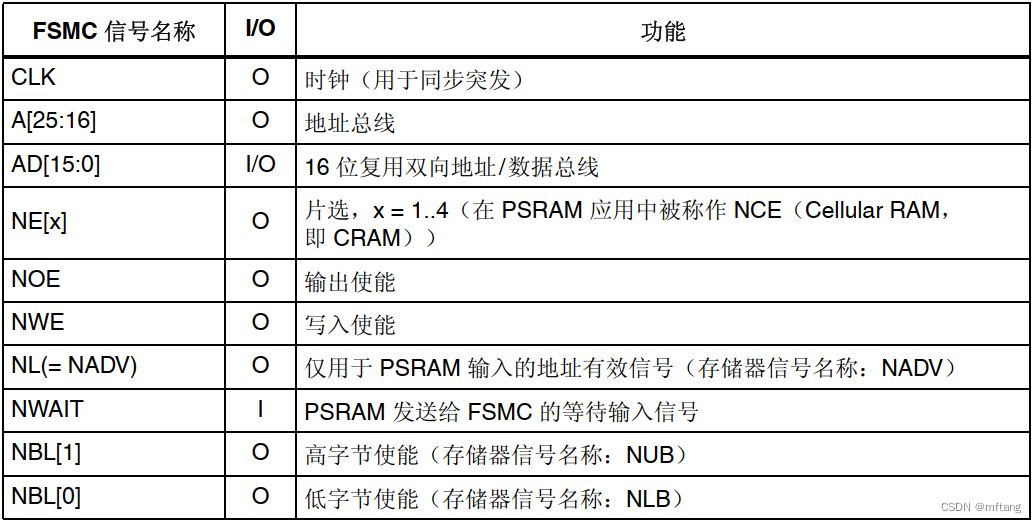

2.2 PSRAM/SRAM

1)非复用 I/O PSRAM/SRAM

PSRAM 存储器采用 16 位字寻址。最大容量为 512 Mb( 26 个地址线)。

2) 复用 I/O PSRAM

PSRAM 存储器采用 16 位字寻址。最大容量为 512 Mb( 26 个地址线)。

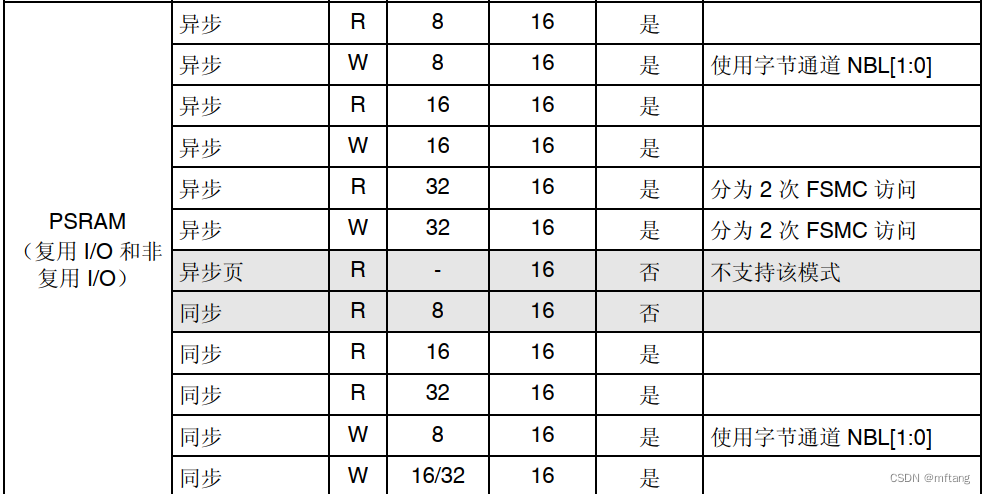

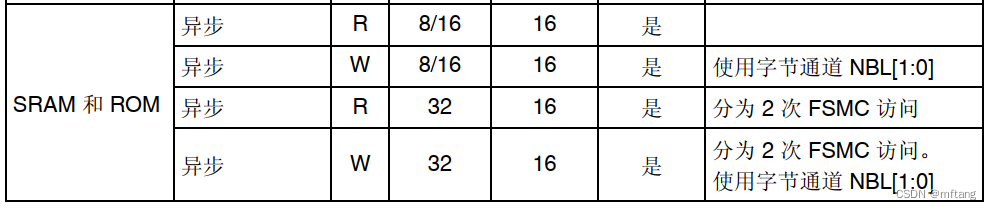

3 支持的存储器和事务

下面的表显示的是当 NOR、 PSRAM 和 SRAM 的存储器数据总线为 16 位时所支持的设备、访问模式和事务的示例。在此示例中, FSMC 不允许(或不支持)的事务显示为灰色。

4 通用时序规则

信号同步

● 所有的控制器输出信号在内部时钟 (HCLK) 的上升沿变化

● 在同步模式(读取或写入)下,输出的数据在 HCLK 的上升沿变化。无论 CLKDIV 值为何,所有输出均会按以下方式变化:— 当出现 FSMC_CLK 时钟的下降沿时, NOEL/NWEL/NEL/NADVL/NADVH/NBLL/ 地址有效输出可发生变化。

— 当出现 FSMC_CLK 时钟的上升沿时, NOEH/NWEH/NEH/NOEH/NBLH/ 地址有效输出可发生变化。

5 NOR Flash/PSRAM 控制器异步事务

异步静态存储器( NOR Flash、 PSRAM、 SRAM)

1) 信号通过内部时钟 HCLK 进行同步。不会将此时钟发送到存储器

2)FSMC 总是会先对数据进行采样,而后再禁止片选信号 NE。这样可以确保符合存储器数据保持时序的要求(数据转换的芯片使能高电平,通常最低为 0 ns。)

3)如果使能扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位置 1),则最多可提供四种扩展模式( A、 B、 C 和 D)。可以混合使用 A、 B、 C 和 D 模式来进行读取和写入操作。

例如,可以在模式 A 下执行读取操作,而在模式 B 下执行写入操作。

4)如果禁用扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位复位),则 FSMC 可以在模

式 1 或模式 2 下运行,如下所述:

— 当选择 SRAM/CRAM 存储器类型时,模式 1 为默认模式( FSMC_BCRx 寄存器中

MTYP = 0x0 或 0x01)。

— 当选择 NOR 存储器类型时,模式 2 为默认模式( FSMC_BCRx 寄存器中 MTYP =

0x10)。

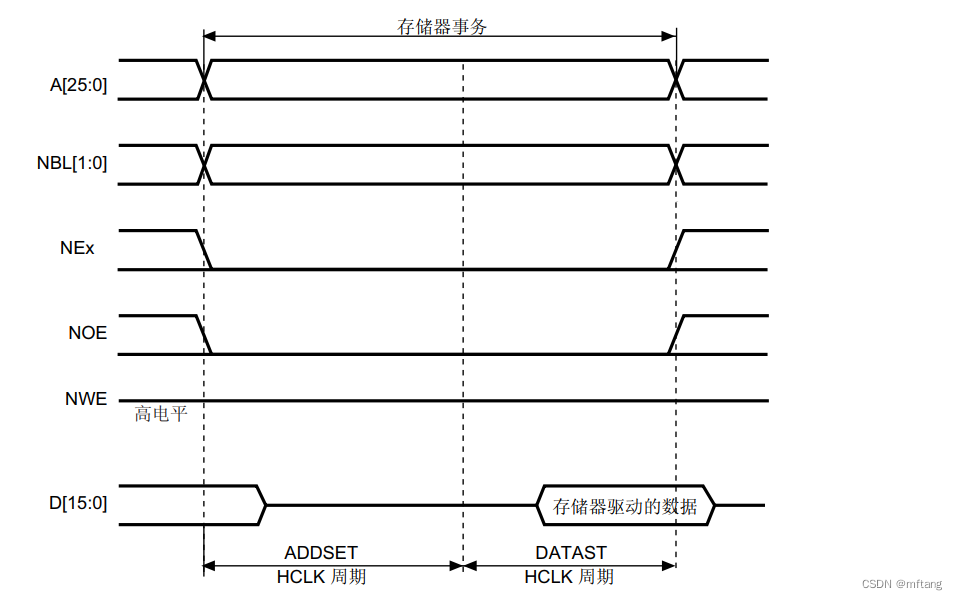

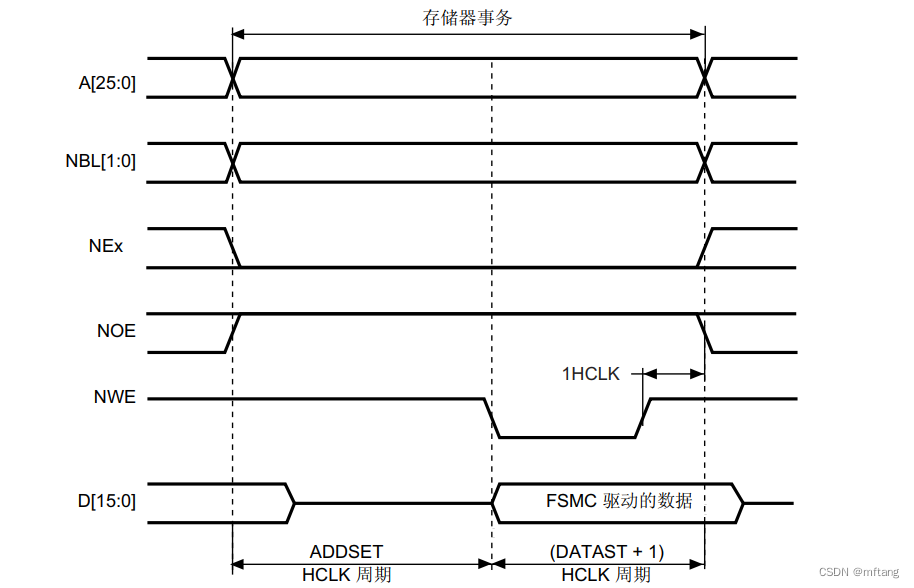

5.1 模式 1 - SRAM/PSRAM (CRAM)

1)模式 1 读取访问

NBL[1:0] 在进行读取访问时为低电平。

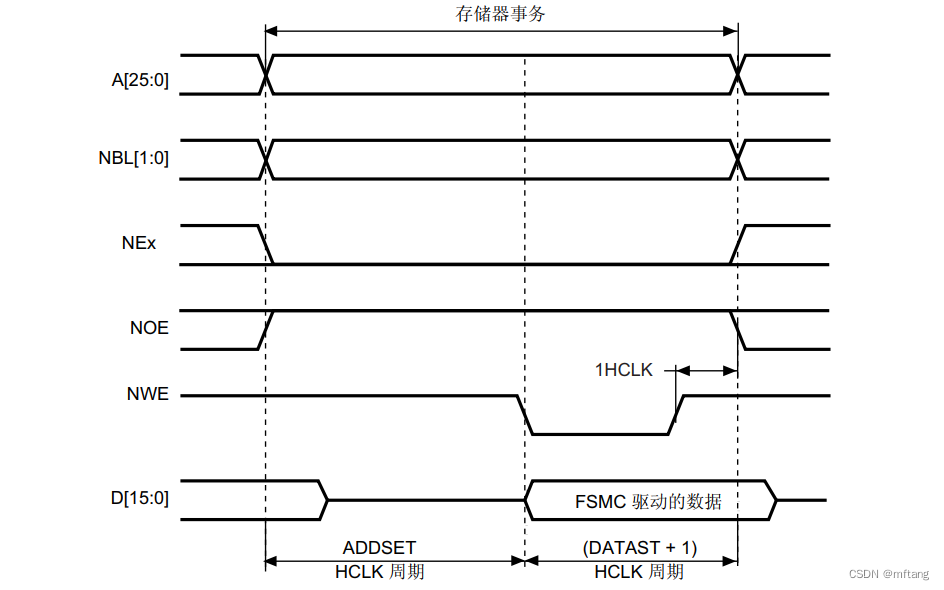

2) 模式 1 写入访问

位于写入事务末尾的一个 HCLK 周期有助于确保 NWE 上升沿之后的地址和数据保持时间。

由于存在此 HCLK 周期, DATAST 值必须大于零 (DATAST > 0)。

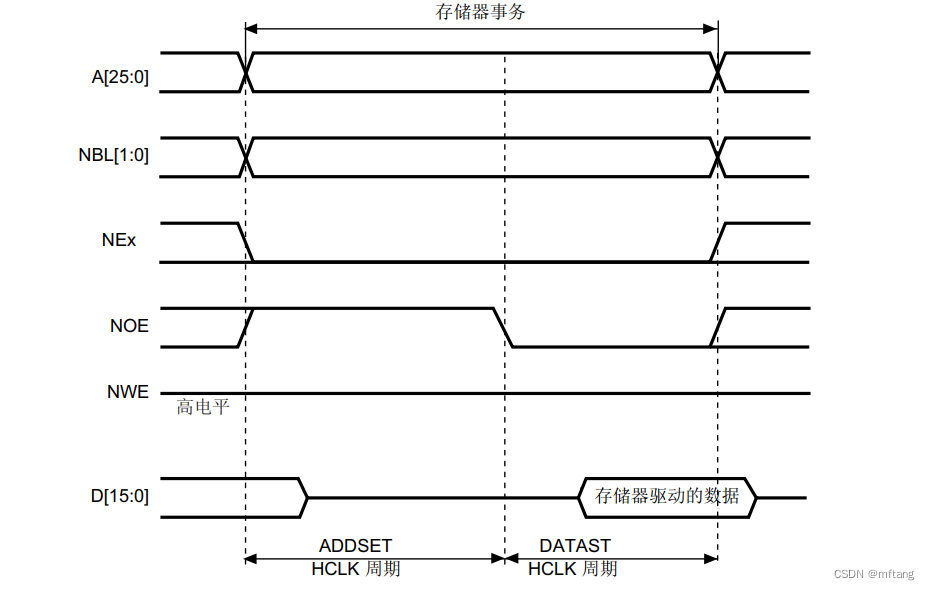

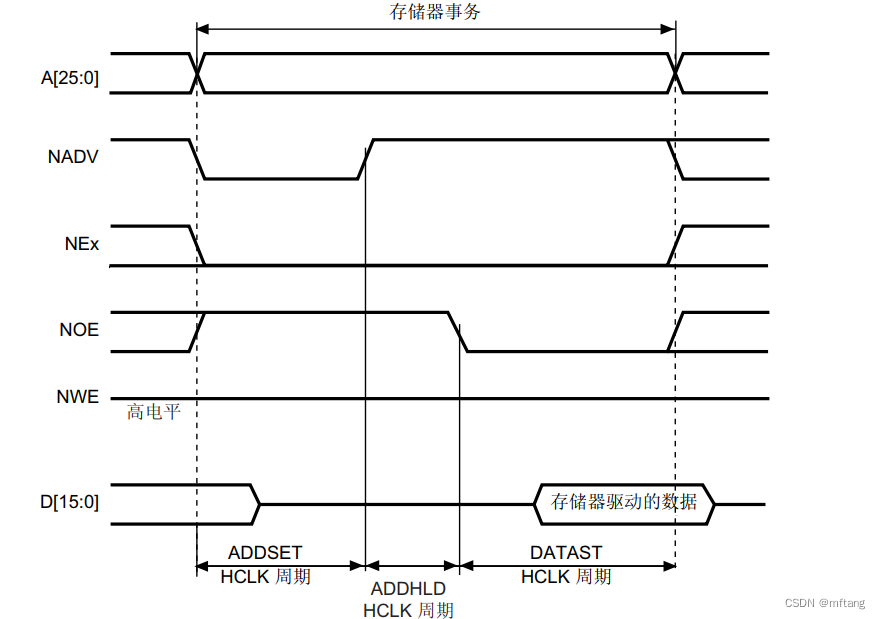

5.2 模式 A - SRAM/PSRAM (CRAM) OE 切换

1)模式 A 读取访问

NBL[1:0] 在进行读取访问时为低电平。

2)模式 A 写入访问

与模式 1 的不同之处在于 NOE 的切换与独立的读取和写入时序。

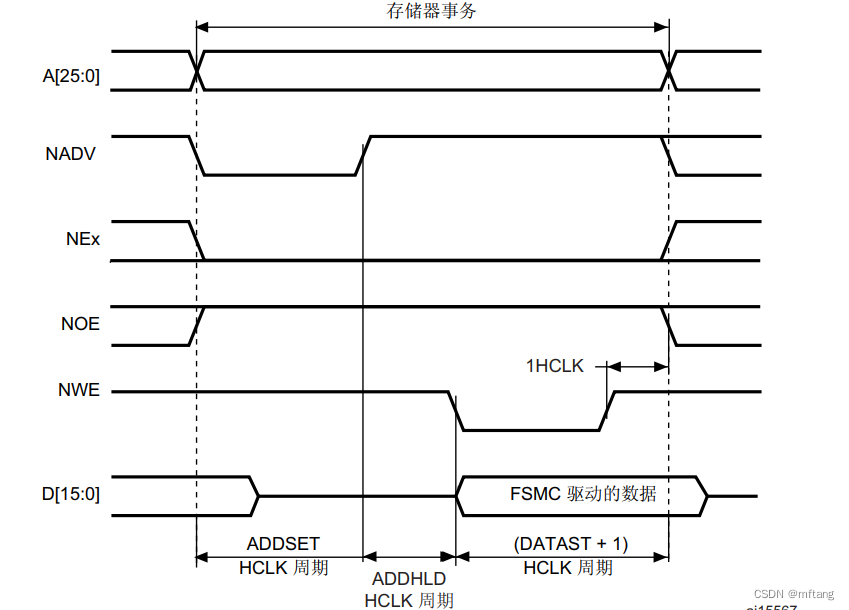

5.3 模式 D - 扩展地址异步访问

1)模式 D 读取访问

2)模式 D 写入访问

与模式 1 的不同之处在于 NADV 变化后 NOE 的切换与独立的读取和写入时序。

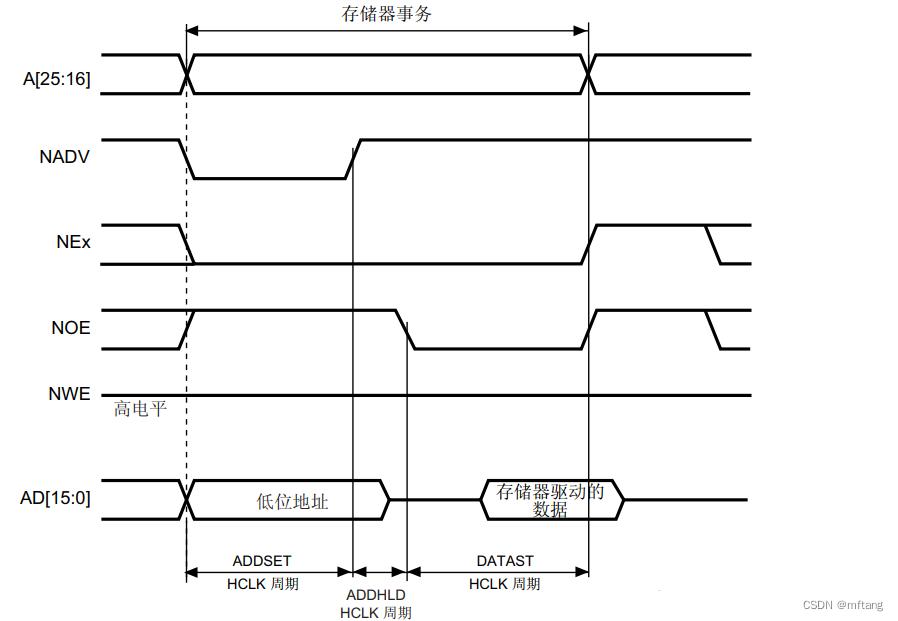

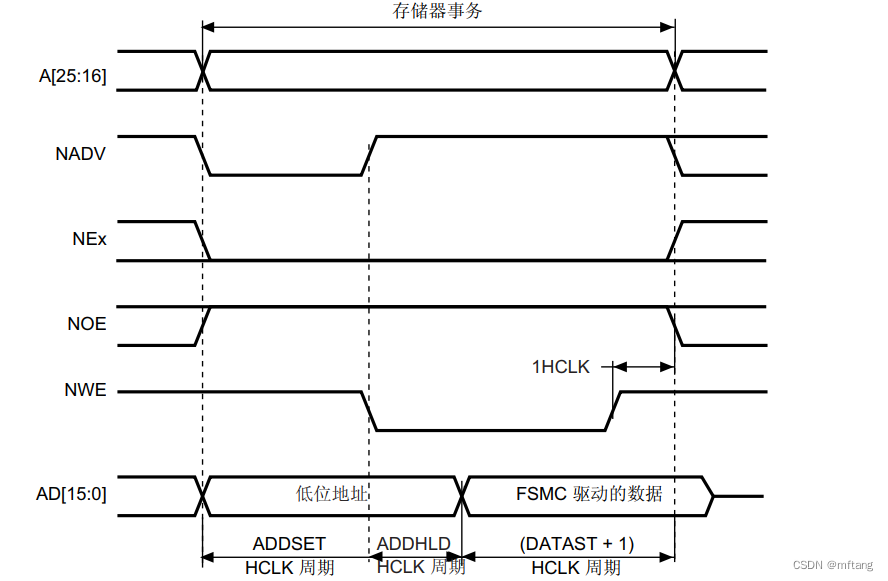

5.4 复用模式 - 复用异步访问 NOR Flash

1)复用读取访问

2)复用写入访问

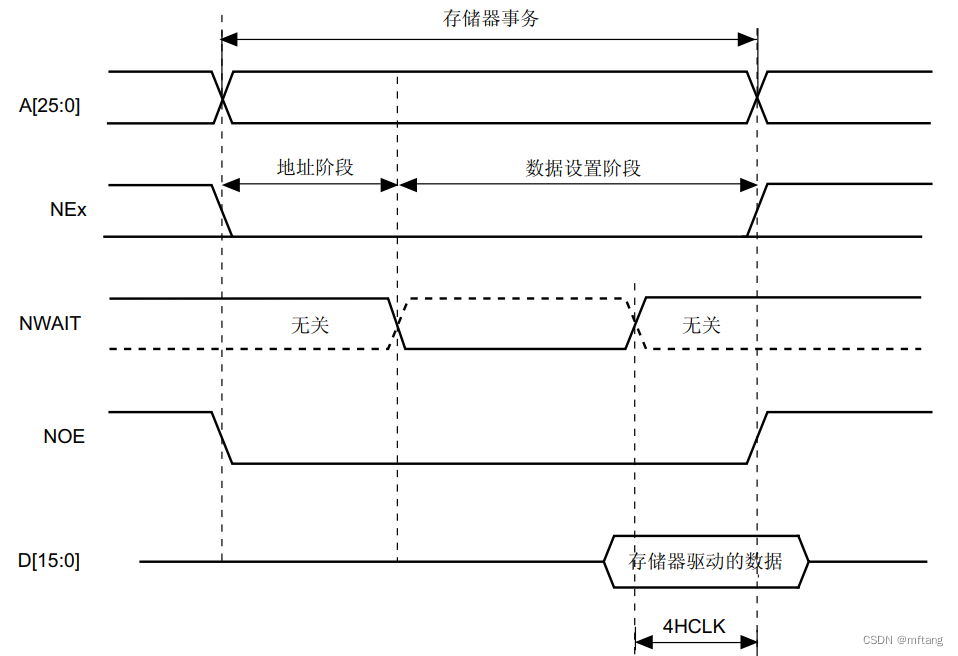

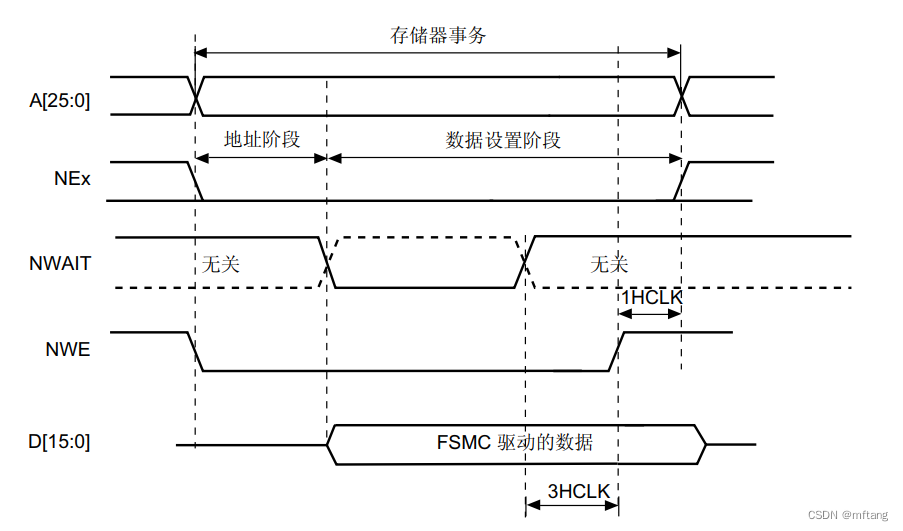

5.5 异步访问中的 WAIT 管理

如果异步存储器发出 WAIT 信号,指示尚未准备好接受或提供数据,则 FSMC_BCRx 寄存器中的 ASYNCWAIT 位必须置 1。

如果 WAIT 信号处于有效状态(电平高低取决于 WAITPOL 位),则由 DATAST 位控制的第二个访问阶段(数据建立阶段)将延长,直到 WAIT 变为无效状态。与数据建立阶段不同,由 ADDSET 和 ADDHLD 位控制的第一个访问阶段(地址建立和地址保持阶段)对WAIT 不敏感,因此第一个访问阶段不会延长。

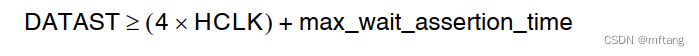

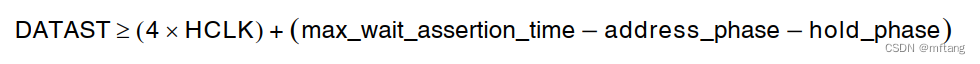

必须配置数据建立阶段(FSMC_BTRx 寄存器中的 DATAST),以便在存储器事务结束前 4 个HCLK 周期检测到 WAIT。必须考虑以下情况:

1)存储器发出的 WAIT 信号和 NOE/NWE 信号对齐:

2)存储器发出的 WAIT 信号和 NEx 对齐(或者 NOE/NWE 信号不翻转):

if 如下条件:

![]()

do:

else:

参数

其中, max_wait_assertion_time 是在 NEx/NOE/NWE 变为低电平后存储器使能 WAIT

信号所花费的最长时间。

图 1和 图2显示了异步存储器释放 WAIT 之后,在存储器访问过程中增加的 HCLK 时钟周期的个数(与上述情况无关)。

图1:读取访问期间的异步等待

图2:写入访问期间的异步等待

这篇关于FSMC的NOR Flash/PSRAM 控制器功能介绍(STM32F4)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!