本文主要是介绍NRF52832时钟控制系统,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

NRF52832时钟控制系统可以从内部或外部高频、低频振荡器获得系统时钟,并根据模块的各自需要给他们分配时钟,时钟分配是自动化的,并通过模块独立分组,以限制未使用的电流消耗。

HFCLK clock controller

下面是时钟的主要特点:

• 64 MHz 内部振荡器

•64 MHz 晶体振荡器,使用外部32 MHz的晶振

• 32.768KZ +- 250 ppm的RC振荡器

•32.768 kHz晶体振荡器,使用外部32.768 kHz晶振

•32.768 kHz合成振荡器,从64 MHZ振荡器合成

•固件(FW)覆盖振荡器控制活动的低延迟启动

•自动振荡器和时钟控制,以及超低功耗的分布

当系统从HFCLK控制器请求一个或多个时钟时,HFCLK控制器将会自动提供。 如果系统没有请求由HFCLK控制器提供的任何时钟,控制器将进入省电模式。

当系统需要HFCLK时钟时,如果HFXO尚未启动时,将使用HFINT振荡器。

可以通过触发HFCLKSTART任务启动HFXO振荡器,触发HFCLKSTOP任务停止HFXO振荡器。

当HFXO启动并且其频率稳定时产生HFCLKSTARTED事件

HFXO必须运行才能使用RADIO,NFC模块或与之相关的校准机制

19.1.1 64 MHz crystal oscillator (HFXO)

64 MHz晶体振荡器(HFXO)由32 MHz外部晶振控制

这个晶体振荡器是使用的无源晶振,为了实现正确的振荡频率负载电容必须匹配的晶体数据表规范。

下图是32M晶振连接电路图

负载电容CL由C1和C2串联得出

C1和C2为贴片电容,如图所示连接,

Cpcb1和Cpcb2是PCB上的杂散电容。

CPIN

是XC1以及XC2引脚间的分布电容

C1和C2应该用相同容量的电容,详细信息请查表。

为了可靠的运行,晶体负载电容,并联电容,等效串联电阻和

驱动电平必须符合第104页表64 MHz晶体振荡器(HFXO)中的规格

建议使用低于最大负载电容和/或并联电容的晶体。 低一点

负载电容会降低启动时间和电流消耗

19.2 LFCLK clock controller

该系统支持多种低频率的时钟源。

•32.768 kHz RC振荡器(LFRC)

•32.768 kHz晶体振荡器(LFXO)

•从HFCLK(LFSYNT)合成的32.768 kHz

首先选择寄存器LFCLKSRC中的首选时钟源来启动LFCLK时钟

然后触发LFCLKSTART任务

如果选择LFXO作为时钟源

当LFXO启动时,LFCLK将先从32.768 kHz LFRC开始运行,

一旦LFOX启动成功,则自动切换到LFOX运行,LFXO将生成LFCLKSTARTED事件。

通过触发LFCLKSTOP任务来停止LFCLK时钟

当LFCLK正在运行时,不允许写寄存器LFCLKSRC

触发LFCLKSTOP任务将停止LFCLK振荡器。 但是,LFCLKSTOP任务只能在寄存器LFCLKSTAT中的STATE字段为“LFCLK运行状态"才能被触发。

在OFF模式下,LFCLK时钟控制器和所有LFCLK时钟源始终为关闭。

19.2.1 32.768 kHz RC振荡器(LFRC)

低频时钟(LFCLK)的默认源是32.768 kHz RC振荡器(LFRC)。

LFRC频率将受温度的影响而变化。

LFRC振荡器可以校准

通过在校准期间使用HFXO作为参考振荡器来提高精度。

LFRC振荡器不需要额外的元件。

19.2.2校准32.768 kHz RC振荡器

32.768 kHz RC振荡器启动和运行后,可通过触发CAL任务进行校准。 在在这种情况下,HFCLK将被暂时打开并用作参考。校准完成后,将产生DONE事件。 只要HFCLK从HFCLK晶体振荡器产生,校准机制才有效,因此在开始校准之前需要明确地启动该晶体振荡器,参见HFCLKSTART任务。

19.2.4 32.768 kHz晶体振荡器(LFXO)

对于更高的LFCLK精度(当要求的精度要好于+/- 250 ppm时),必须使用低频晶体振荡器(LFXO)

支持以下外部时钟源:

•低频时钟信号施加到XL1引脚。 然后XL2引脚接地。

•轨至轨时钟信号施加到XL1引脚。 XL2引脚应接地或未连接。

在LFCLKSRC寄存器配置时钟源

19.2.5由HFCLK(LFSYNT)合成的32.768 kHz

LFCLK也可以从HFCLK时钟源合成。 那么LFCLK的精度就是HFCLK的精度。

使用LFSYNT时钟避免了对32.768 kHz晶振的要求,但增加了平均功耗。

下面是寄存器表了

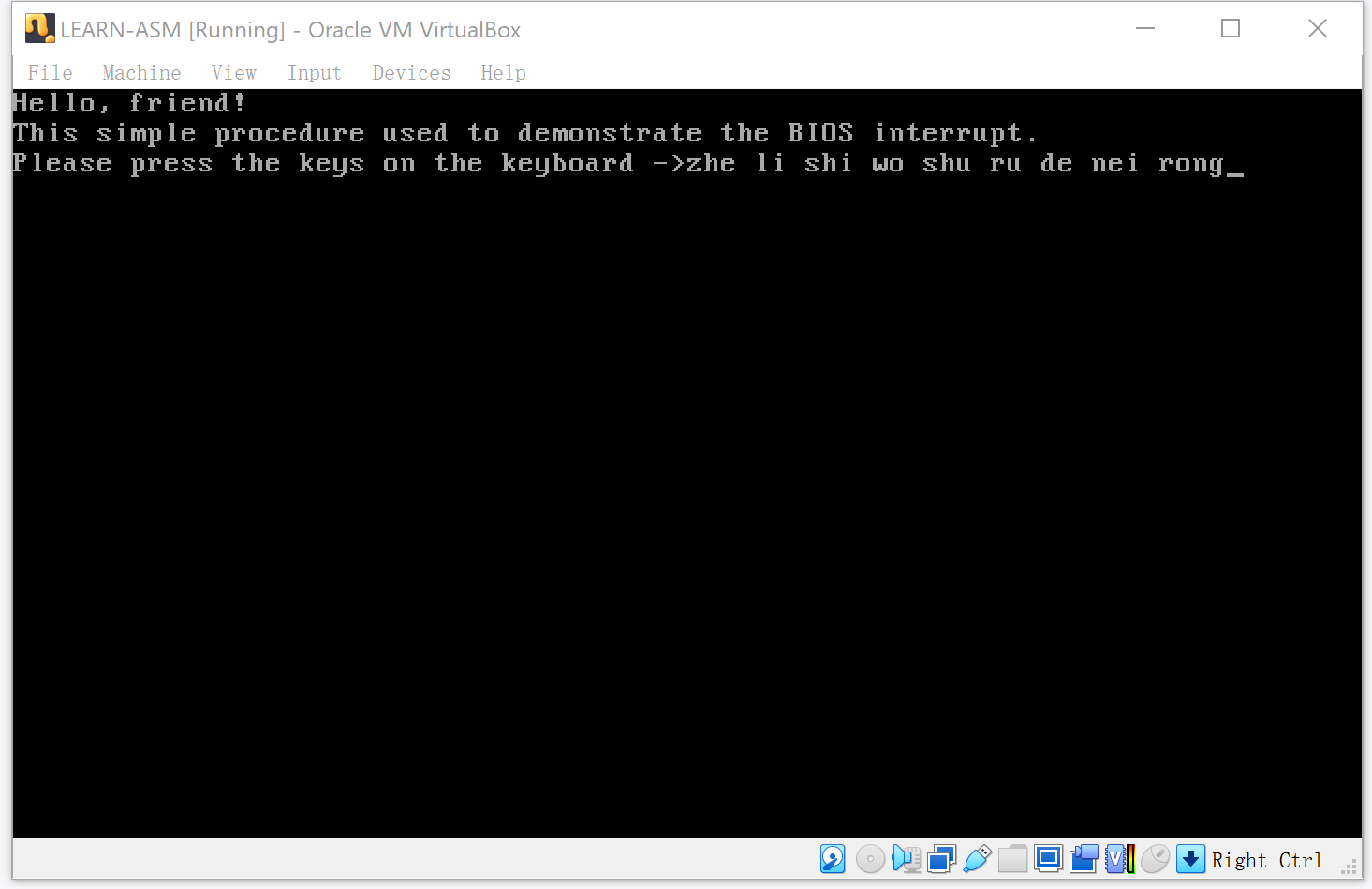

下面代码实现:

启动32M外部晶振

NRF_CLOCK->EVENTS_HFCLKSTARTED = 0; //HFCLK晶振状态寄存器清0 如果HFCLK也就是32M晶振启动并频率稳定后,这个寄存器会自动置1

NRF_CLOCK->TASKS_HFCLKSTART = 1; //启动HFCLK的晶振 也就是32M的外部晶振

while (NRF_CLOCK->EVENTS_HFCLKSTARTED == 0)

{

//外部晶振启动并稳定后跳出循环

}

启动外部32.768晶振:

和HFCLK类似

先配置LFCLK时钟源

寄存器LFCLKSRC

我们只要把SRC写1就配置成了外部32.768的晶振,其他的默认即可。

NRF_CLOCK->LFCLKSRC = (1 << 0);

NRF_CLOCK->EVENTS_LFCLKSTARTED = 0; //状态清0

NRF_CLOCK->TASKS_LFCLKSTART = 1; //启动LFCLK时钟源

while (NRF_CLOCK->EVENTS_LFCLKSTARTED == 0)

{

//LFCLK启动成功后跳出

}

总结一下:

NRF52832由HFCLK高速时钟和LFCLK低速时钟两大块组成

HFCLK高速时钟可以自动提供PCLK1M PCLK16M PCLK32M HCLK64M给处理器及外设

HFCLK时钟源有内部HFINT64M振荡器和HFXO64M晶体振荡器,HFXO64M晶体振荡器由外部32M无源晶振提供。

当刚开机时,由内部HFINT振荡器提供HFCLK时钟,如果触发HFCLKSTART启动外部32M晶振时,当32M晶振启动并稳定时,

将自动切换为外部32M晶振时钟源,并产生HFCLKSTARTED事件。

使用RADIO NFC必须使用HFXO也就是32M外部晶振。

当 没有请求使用HFCLK高速时钟时,HFCLK控制器自动休眠。

LFCLK低速时钟源由一下三种

内部RC

32.768晶振,

HFCLK合成32.768

需要配置寄存器LFCLKSRC选择时钟源。

当配置了外部32.768源,触发LFCLKSTART来启动时,LFCLK先由内部RC振荡器提供

当外部32.768稳定启动后,自动切换为外部32.768.

需要注意的是

触发TASKS_HFCLKSTART任务是启动的HFXO 也就是外部32M晶振

触发TASKS_LFCLKSTART任务是启动HFCLK时钟,(具体哪个时钟源由你自己配置)

这篇关于NRF52832时钟控制系统的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!