本文主要是介绍【冬瓜哥手绘】上/下页、快/慢页、MSB/LSB都些什么鬼?,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

【本文背景】

事情是这样的:冬瓜哥一直没弄清楚标题中的这些鬼概念,一直是心头一大疙瘩。昨天,在ssdfans群里,冬瓜哥就抛出了这个问题向大家请教,果不其然,一石激起千层浪,大家纷纷发表看法,结果并没有能让人看懂的表述,主要原因是群聊就根本不适合解释如此复杂的问题,其中瑞耐斯的创始人兵哥还画了个图来解释,但是冬瓜哥比较愚钝,未能理解。后来,热心群友Vic.Ye以及他的其他两位同事(就职于深圳硅格半导体,消费类Flash主控)恰好在北京出差,就邀请冬瓜哥前去一聊,冬瓜哥很兴奋的赴约,结果在他的提示下,在纸上画了个图,三句话就解释清楚了上面所有这些概念,冬瓜哥茅塞顿开,这才知道为什么这几个东西用打字很难讲清楚的原因,遂决定用典型的冬瓜哥式思路和表述方式来将该问题表述清楚,方能放下心中这块疙瘩。有些遗留和衍生问题,冬瓜哥在今天上午还与Vic通了电话又请教了一番,最终才有了这个问题的全貌,也就是前因后果来龙去脉。在此,向Vic.Ye表示由衷感谢!同时也感谢兵哥一直在尝试给鄙人解释清楚但是由于沟通不便没能如愿。 本文所有赞赏冬瓜哥会转交给Vic.Ye,希望大家踊跃赞赏。

【NAND Flash基本原理】

目前的NAND Flash中包含SLC、MLC和TLC的介质类型,SLC可以用一个Cell保存1bit数据,MLC可以用一个Cell中的4个状态表示2bit,而TLC可以表示3bit,将来还会有可存储4bit的QLC类型出现。

假设, 向SLC Cell中充入电子到电压绝对值1v则表示0,不充电则表示1,那么,在读出该Cell中数据的时候,就需要判断 “该Cell中是否有电” 即可,有,或者没有,就可以判断其是0还是1了。

Cell中不充电时,该Cell为截止态,也就是关断态,但是并不意味着这个开关一点电流都不能通过完全绝缘,其有一定的非常微弱的漏电流,只是因为这个漏电流不足以驱动下游的响应高电压的逻辑门的状态改变,所以被视为逻逻辑0(其实这个说法是不严谨的,应该是高阻态而不是逻辑0,只是Flash中的Cell是存储器件而不是逻辑门器件,所以把高阻态视为0是没有问题的)。而如果Cell中的微型电容被充了电子,那么其基底半导体区域受到负电场的影响,漏电流将会更加微弱。相反,如果在CG电极上加正电压,用正电场影响基底半导体区,则Cell的漏电流就会增加,也就是处于导通态,如果足以驱动下游的响应高电压的逻辑门,则可视为逻辑1。所以,很自然的,判断一个Cell中是否有电,就得判断其漏电流的大小来决定,或者换个物理量,判断其压降大小来确定。不好意思,如果你高中物理不及格,不知道压降啥意思的话,那还是别继续看了,回去补习吧,哈哈。

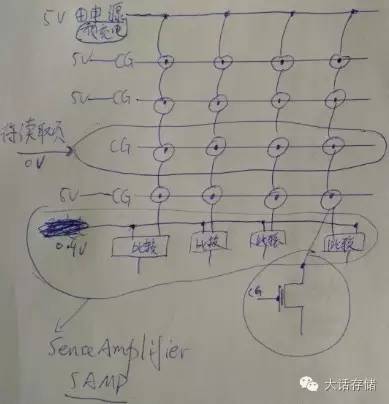

那么,如何判断某个Cell的压降?实际上很复杂,是按照下图的原理来做的:

NAND Flash每次IO单元为一个Page,一般为8K/16K。要读取某个Page,需要将该Page所在的Block中的所有其他Page里的所有Cell强行导通,方法是在CG电极上加正电压,但是又不会击穿微型电容外围的绝缘体而导致Cell被充电。这样,从电源的电压会透过所有其他Cell传递而几乎没有压降。而电压在压入待读取页面的Cell时,由于该页面的CG没有施加正电压(实际上需要加一点点正电压比如图中的2v,以增强Cell的导通性,否则漏电流太过微弱无法检测),所以其导通性完全取决于Cell内是否充了电。比如假设,充了电,压降大,电源的5v透过该列之后被降为0.5v; 没充电的压降小,该列的输出电压比如为1v。很显然,只要用电路来获取每一列输出的电压值即可获知带读取page中每个cell有没有充电。但是我们知道,每次充电并不是恰好就充到某个电压值的,可能不足也可能超过,充入之后,过了一段时间可能会漏电,所以最终输出的电压其实并不是某个绝对值,而是一个范围,比如充了电的Cell产生压降之后的列输出电压值范围可能在0v~0.8v之间,没充电的cell所在列的电压输出值基本恒定为1v左右。

这样的话,就需要找一个参考电压来与列输出电压进行比较,列输出电压高于这个参考电压统统认为是1v也就是逻辑1,低于这个参考电压统统认为是0v也就是逻辑0。显然,上述例子中参考电压需要设置在0.9v。实际上,电路中是采用Sense Amplifier比较电路来实现上述逻辑的,其本质上是一个数字差分放大器,其能够将微弱的电压差值直接放大为足以驱动逻辑门的电流从而让逻辑门为1或者0状态,其具体电路可参考《大话存储 终极版》中Flash一节。所以,列输出电压值高,SAMP的输出为逻辑1,表示待读取Cell中没有充电(压降小);反之则为0。这就是NAND,Not AND中Not的意义,也就是实际含义与表象电压值相反。而AND则表示一列Cell是串联的开关,很显然就是一个多输入与门,也就是AND的关系,NAND因此由来。

实际上,电源的电压并不是一直加在列导线(bitline,位线)上的,而是在每次读取某个page的时候,对bitline预充电到某个电压,在经过某个时间后(该时间是经过充分设计出来的,时间太短的话漏电太少,检测到的都是逻辑1,时间太长的话,所有bitline电全漏光了,检测到的就全是逻辑0),在列输出端对透过来电压用模拟信号电压跟随器进行采样比较,漏电快的列先达到参考电压从而直接被放大成逻辑0,漏电慢的则未达到参考电压而直接被放大为逻辑1,之后输送到数字电路锁存该状态并输出到前端总线。

【MLC NAND咋个弄法】

上述介绍了NAND Flash基本运作原理,只是个铺垫,下面才是进入正题,介绍标题中的这些让人摸不着门的概念。

那么,要想用一个容器存2bit信息,那么这2个bit就会产生4种组合:00,01,10和11,你到底想表示这4个组合里的哪个?那自然就得让这个容器表示出4种不同的状态,通过判断其状态是哪一个从而获知其表示的是哪一种位元的组合。对于Cell来讲,其状态就是内部微型电容器里所被充入的电子电量的多少了,假设,不充电时表示11,充电到绝对值1v表示10, 2v表示01, 3v表示00。

那么,我们很自然朴素的想到了图下图所示的设计,既然现在一个Cell可以表示2bit,那么同样容量的页面,只需要用一半数量的Cell即可承载了。向Cell中写入数据的时候,根据待写入数据来判断对Cell充电到哪个电压。比如,从E(Erase)态,也就是2个bit都为1,改变到D1态,那么就直接充电到1v;如果从E直接到D2态,那么直接充电到2v。可以是这样的顺序:E->D1->D2->D3, 或者E->D2->D3, 或者是E->D3,或者是D1->D2->D3,或者是D1->D3,或者是D2->D3。总之,充电量必须逐级增加,而不可能一开始冲过头了再放电,我们知道NAND Flash放电要放掉整个Block的电的。

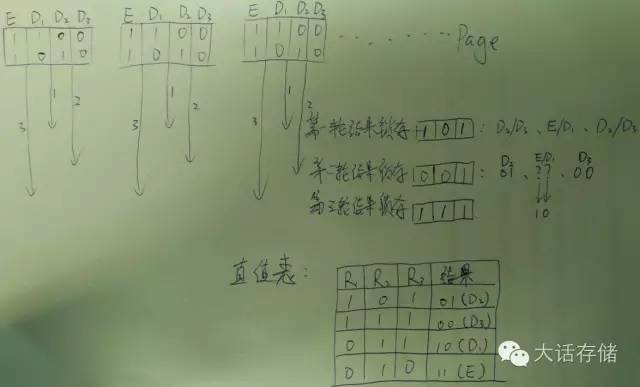

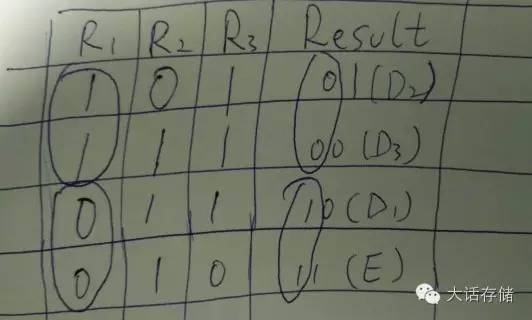

对于读操作,就比较复杂了,需要大家仔细研读。由于一个page中的任何一个cell可以是上述四个电压中的任何一个,我们预先根本就不知道某个cell中会是什么状态,所以,只能用二分法逐次检测。所以我们先将SAMP的参考电压设置为4个状态正中间的电压值,根据SAMP的输出可以得出一组逻辑1或者0的结果,这组结果可以用于初步判断该Cell中的电压是高于还是低于这个参考电压,但是不管高还是低,都无法判断出具体是哪个,还需要第二轮判断。那么第二轮应该把参考电压设置在哪个档位呢?由于有些Cell可能电压较低,有些则较高,只能先选择一个来检测,所以上述例子中我们选择了先队高电压段位进行第二轮二分,显然,第一轮结果为逻辑1(证明cell电压高于中间电压)的cell,如果在第二轮检测中仍然为1,则证明其内部电压位于最高档位D3上,如果第二轮为0则证明其档位位于D2态上。如果第一轮结果为0的cell,第二轮是仍然无法判断其档位的,第二轮检测结果仍会是0,需要第三轮检测,也就是对低段位电压进行二分,此时,第1轮结果为0且第三轮结果也为0,表明该cell处于E态,第三轮如果为1则表明其处于D1态。经过三轮检测之后,所有的Cell状态都可以读出来。

有人会问,为何不根据第一轮的判断结果并行的对该在高段位二分的cell加高的参考电压,对该在低段位二分的cell加低的参考电压?答案就是因为参考电压是同时加载所有bitline SAMP上的,如果要做到如此精细的区分,电路的面积就会非常大,NAND Flash就不会有现在的密度和成本了。

可以看到,需要将三轮的结果进行暂存,所以该处需要三倍于SLC介质的寄存器,另外,由于需要组合判断上述逻辑,需要一个组合逻辑电路来完成上述工作,而且每一列都需要这样一个组合逻辑电路。该电路的真值表如上图所示(R是Round的意思),根据这个真值表做出逻辑电路不费吹灰之力,该电路也比较简单,但就是由于每一列都需要一份,其总量会非常庞大,耗费非常多的电路面积。

【巧妙设计加快读取速度同时还能节省资源】

如上文所述,读取一个page竟然需要三次电压检测,这会极大的影响性能。于是人们开始琢磨着怎么来规避这种开销。也不知道历史上是哪位眼前一亮,看出了奇妙的端倪。

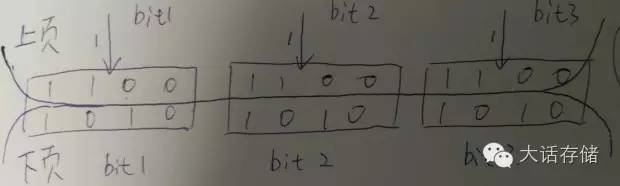

如上图所示,每个MLC Cell中有两个逻辑比特,我们之前的思路是将这两个bit连续放置在同一个page中。上图的思路则是:将其中一个bit分给一个page,另一个bit则分配给另一个page,这样,一个物理Cell就被逻辑的分割为两个各属于不同page的两个bit,上方的bit被称为 MSB ,由多个cell的上方的bit组成的page就叫做 Upper Page/上页 ,下方的bit被称为 LSB ,由多个cell的下方的bit组成的page就叫做 Lower Page/下页 。要理解的一点是,cell中的这两个bit的组合依然还是原来的4种状态以及电压,没有变化。那么这样去逻辑分割的意义何在呢?可以看出来,对于由上方的bit随着电压的升高恰好呈现1100的组合,这又能咋样呢?仔细想想,如果要读出上页的bit来,采用二分法探测电压之后,在第一轮就可以判断出MSB的值。其实这个规律在前文中已经可以看得出来了,看看真值表里的逻辑,只要第一轮结果是1,则MSB必定为0,结果是0则MSB必定为1。

这样处理之后,上页中的数据就可以仅用一轮电压探测即可读出了。那么我们再看看下页的情况,下页无法用一次二分,而必须依然维持三次二分查找才能读出整个页面的全部数据。所以,上页又被称为 快页 ,而下页则是 慢页 。

值得一提的是,这两个逻辑上分开的页面是处于同一个Block中的,那是当然,因为其承载者是同一行Cell,要擦除则这两个页面一起被擦除。另外,将数据写入这两个页的时候,可以任意写入,这两个页并没有牵连。比如从原始状态也就是E态,如果某个应用需要将上页中的该cell位改为0,那么可以直接将该cell充电到D2态,也就是上0下1;如果后面某个时刻应用又想把下页该cell位写为0,则从D2态继续充电到D3态即可,也就是上0下0。如果应用先写下页,则从E到D1态,然后后面如果再写上页的话则从D1直接充电到D3态。一旦写了0,就不能单bit再回退到1,除非擦除整个block。

【先人是怎么解决下页依然速度过慢的】

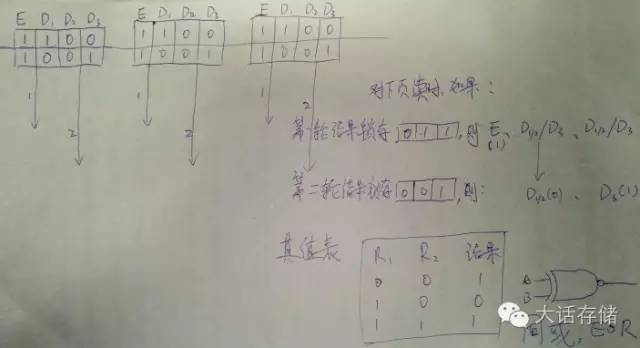

不得不佩服人们的奇思妙想。读下页还是需要三轮电压探测,不过人们想了个办法,巧妙地规避了其中一轮探测,使得读下页只需要两轮探测即可,提升了33%的速度。如下图所示。我们把电压值与位元组合的编码映射方式变一变,让E态为11,D1为10,D2为00,D3为01,也就是将之前D2和D3的状态对调一下。然后巧妙的事情就会发生。可以看到MSB依然按照1100的方式排列,读上页依然可以一次探测读出。而下页则按照1001的方式排列,那么我们是否可以在读出下页的时候,将第一轮探测电压档位放在1和001之间呢,这样的话,探测到的电压低于第一轮参考电压的话,那么LSB一定为1。第二轮的档位则放在001和00和1之间,那么对于那些在第一轮探测中的结果为1的cell,在第二轮中的结果如果低于第二轮参考电压,则其值一定为0,结果为1的话则其值一定为1。这样就可以节省一轮探测了。

这种编码方式称为格雷码,其特点是:相邻的两个位元组状态之间只有1bit的变化,而不会从01变为10,或者10变为01。这样做的好处众多,比如在异步FIFO的硬件实现中,就必须使用格雷码,否则会导致异步时钟域采样到的信号编码越变过大而逻辑上出错。而本例中,格雷码则帮助节省了一轮探测。另外,采用格雷码还可以提升纠错率,如果不采用格雷码,01到10有两位跃变,一旦出错,两个状态都受到影响,而每个相邻状态间只有一位跃变的话,可以提升纠错率。这些奇思妙想真是太伟大了。

此外可以看到,应用了格雷码之后,真值表规模也少了,现在不用套用逻辑算式都可以看得出来,这个逻辑就是一个同或门,这样对电路面积的耗费就会进一步降低。

但是,这种设计有个代价,那就是写入数据的时候,必须先写 下页。为什么呢?写就是充电的过程,擦1写0,写就是写0,如果先写了上页,也就是从E态直接充电到D3态,那么之后将无法再写入下页(也就是从D3态回到D2态),因为从D3回到D2意味着将Cell中的电容放电,而除非整block擦除,电路是无法做到对某个Cell放电的。所以,必须先写下页,也就是从E到D1态,从D1可以到D2也可以到D3。其中,从D1到D3的跃变比较有趣,LSB会从0变成1,我们说NAND Flash是不能将某个Cell单独从0变成1的,但是这仅对SLC有效,MLC则不然,从D1跃变到D3对应底层其实是充电的过程,而不是放电。

那么,如果应用程序就是铁了心要把上页/MSB从1改为0呢?(在下页依然为1的前提下),那么底层其实是将下页映射成应用要访问的目标地址,也就是改映射表,让下页先上,上页垫后,这样就可以了。

对于TLC,做法是相同的,大家可以自行演绎,冬瓜哥就不再多叙述了。

------END------

本文所有赞赏冬瓜哥会转交给Vic.Ye,希望大家踊跃赞赏。

其他相关阅读(点击可直接进入):

《 和唐杰说相声之:SSD性能测试之“玉” 》

《【冬瓜哥画PPT】最完整的存储系统接口/协议/连接方式总结》

《【冬瓜哥论文】 原子写,什么鬼?! 》

《固态存储到底怎么做Raid? 》

《 【冬瓜哥手绘】大话众核心处理器体系结构 》

《关于SSD元数据及掉电保护的误解 》

《 关于闪存FTL的Host Base和Device Based的误解 》

《关于SSD HMB与CMB》

这篇关于【冬瓜哥手绘】上/下页、快/慢页、MSB/LSB都些什么鬼?的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!