本文主要是介绍1.2 HD-GR-1底板,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

\qquad HD-GR-1底板的设计目标是为HD-GR接收机提供可重开发、重配置的硬件逻辑,以及可定制的嵌入式软核。它的标准配置包括一个功能强大的FPGA芯片Altera Cyclone IV(具有22,320个逻辑单元)、一个8-MByte SDRAM、一个64-Mbit串行配置存储设备。为了能够不间断地维持时间信息,HD-GR-1底板还配置了一个RTC。

\qquad 此外,底板包括一个用于编程和调试FPGA芯片的JTAG口,两个用于连接射频前端模块的通用I/O口插头,两个RS232串行端口,一个PPS信号接口,等等。底板用外部电源供电。

1.2.1 主要特性

\qquad 底板主要特性如下:

-

FPGA芯片

- Altera Cyclone® IV EP4CE22E144 FPGA

- 79个用户信号I/O引脚

-

配置设备

- Numonyx M25P64(兼容EPCS64)

-

射频前端接口

- 两个16-针插头(GPIOs)提供32个I/O引脚,用于接收射频前端信号(包括时钟信号),以及提供5V/3.3V电源和用于接地。

-

内存芯片

- 8-MByte SDRAM

-

实时时钟

- Maxim DS32X35

-

时钟系统

- 两个底板时钟振荡器(可选焊接)

- 两个外部时钟信号(通过射频前端接口引入)

-

电源

- 10~30V外部电源接头

- 3.3Vn内部钮扣电池

- 5V/3.3V电源提供射频前端接口

-

其它

- 两个串行端口

- 一个PPS信号接口

- 一个系统复位按钮

- 四个测试用LEDs

1.2.2 布局和器件

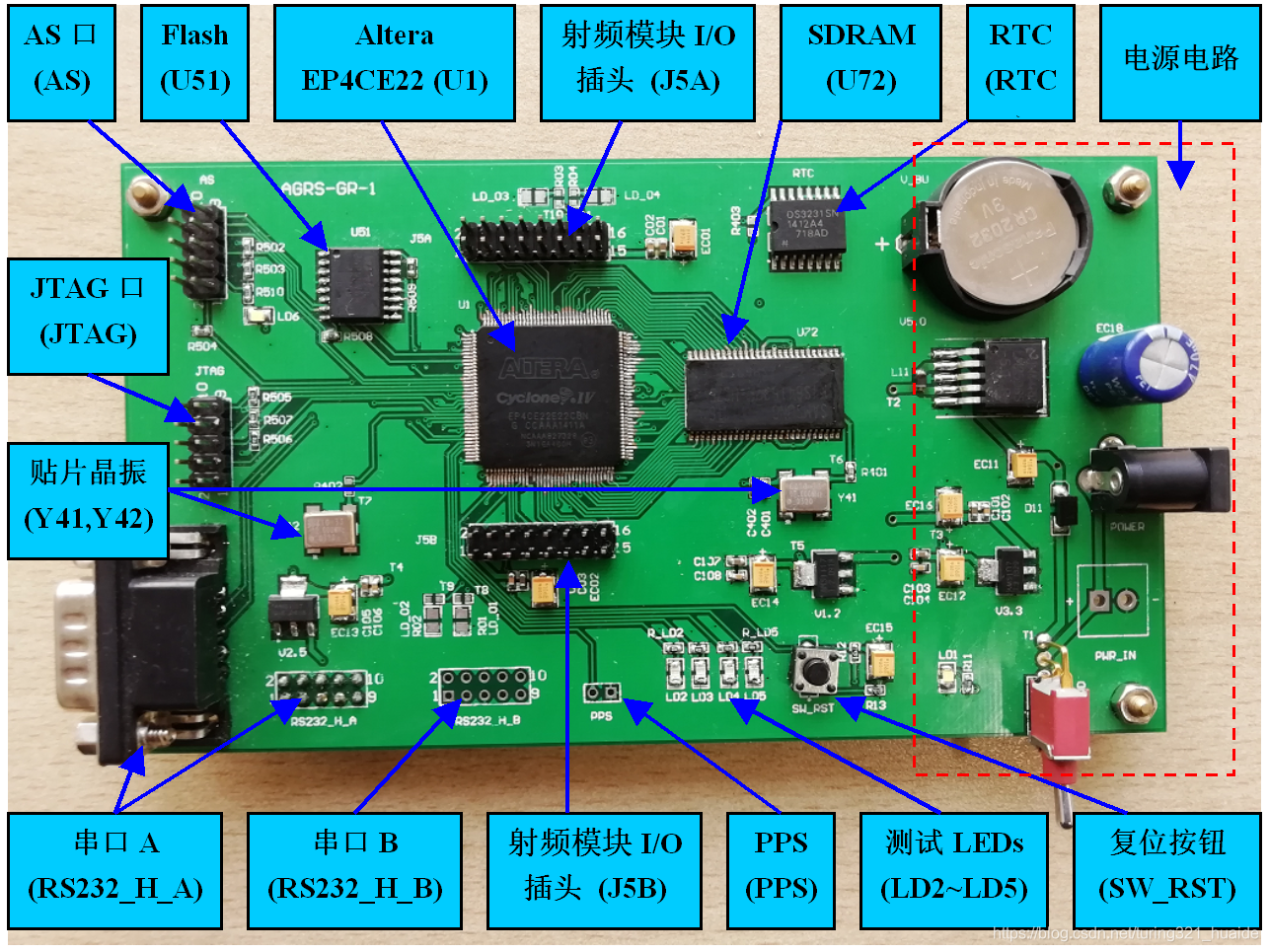

\qquad 图1-4显示了HD-GR-1底板正面布局,并对连接器和关键器件位置进行了标注:

-

底板中间偏左是核心芯片Altera Cyclone-IV EP4CE22 FPGA (U1),实现的功能包括:基带模块、软核(处理器)、运行在软核中的基带控制软件和导航软件、以及其它一些外围组件和逻辑。围绕这片FPGA:

- 左上方有一个Flash芯片(U51, Numonyx M25P64),右边有一个SDRAM芯片(U72),用于存储基带硬件逻辑、基带及导航软件、等等;

- 左右下方各有一个贴片晶振(可选焊接)(Y41, Y42),用于为EP4CE22芯片提供时钟信号;

- 上下各有一个通用I/O口插头(J5A, J5B),用于将射频前端模块(HD-2769-2RF-2) 连接到底板。

-

底板左边有一个JTAG口(JTAG)和一个AS口(AS),用于对EP4CE22芯片进行编程和调试;

-

底板右边包括:

- 一个电源电路;

- 一个实时时钟电路(RTC, Maxim DS32X35)。用于在断开外部电源时,为运行在微处理器中的软件维护时间、用户参数等信息。

-

底板下部包括:

- 两个串行端口(RS232_H_A, RS232_H_B),用于参数设置和数据输出;

- 一个PPS信号接口(PPS),用于输出秒脉冲信号;

- 一个系统复位按钮(SW_RST)以及若干测试用LEDs (LD2~LD5)。

1.2.3 底板框图

\qquad 图1-5给出了底板框图。为了赋予接收机开发的最大灵活性,所有重要连接都通过Cyclone IV FPGA芯片(U1)。图中射频接口(J5A, J5B)各引脚的信号定义参见1.3.3小节.

这篇关于1.2 HD-GR-1底板的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!