本文主要是介绍计算机组成原理(超详解!!) 第五节 只读存储器和闪速存储器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.只读存储器(Read Only Memory)

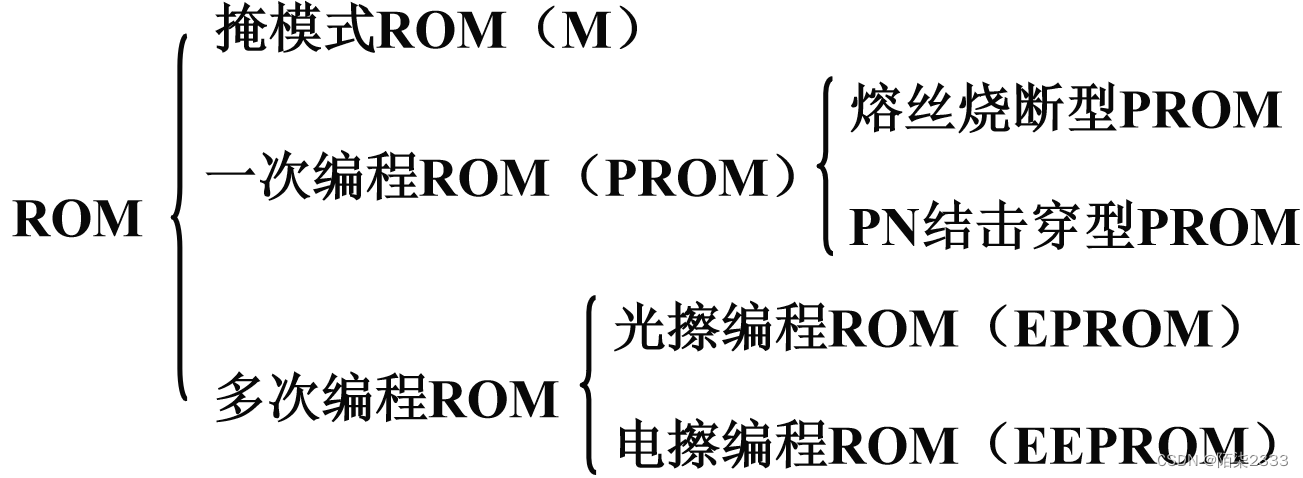

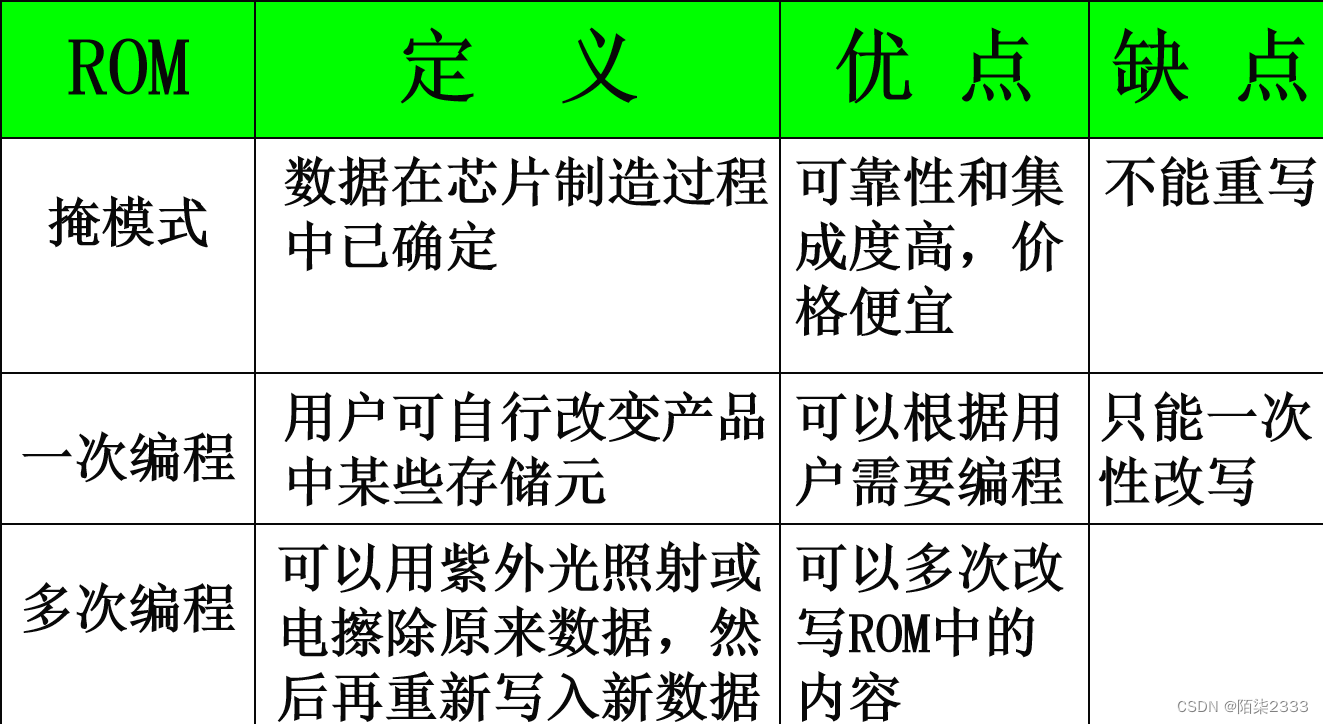

1、ROM的分类

最大优点:具有非易失性

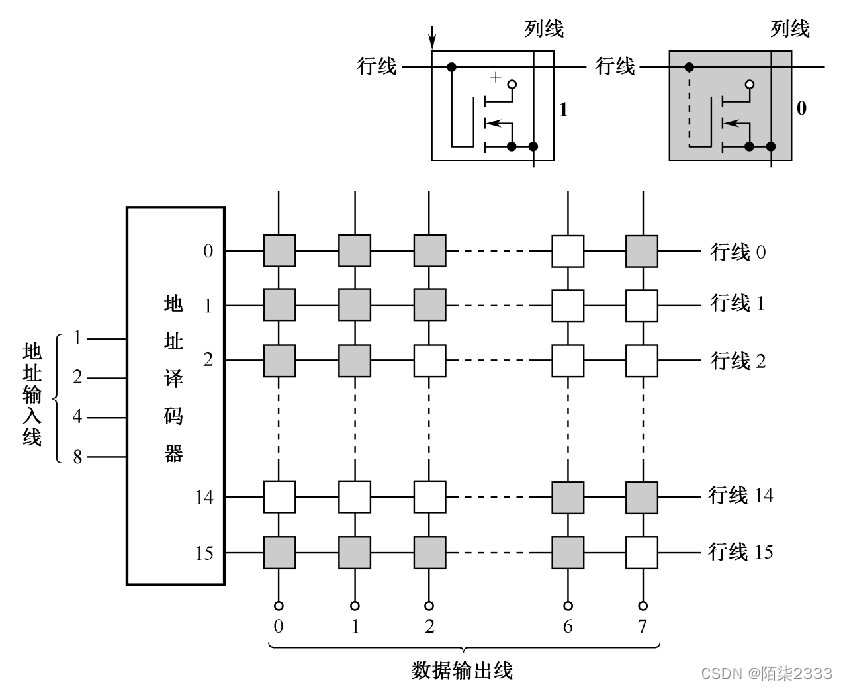

掩膜ROM:

PROM基本存储电路:

2.闪速存储器

FLASH存储器也翻译成闪速存储器,它是高密度非失易失性的读/写存储器。高密度意味着它具有巨大比特数目的存储容量。非易失性意味着存放的数据在没有电源的情况下可以长期保存。总之,它既有RAM的优点,又有ROM的优点,称得上是存储技术划时代的进展。

由INTEL公司于90年代发明的一种高密度、非易失性的读/写半导体存储器。

特性:固有的非易失性;廉价的高密度:成本低,不需后援存储器;直接执行:不从后援存储器加载,可直接执行;固态性能:低功耗、高密度且没有机电移动装置的半导体技术;

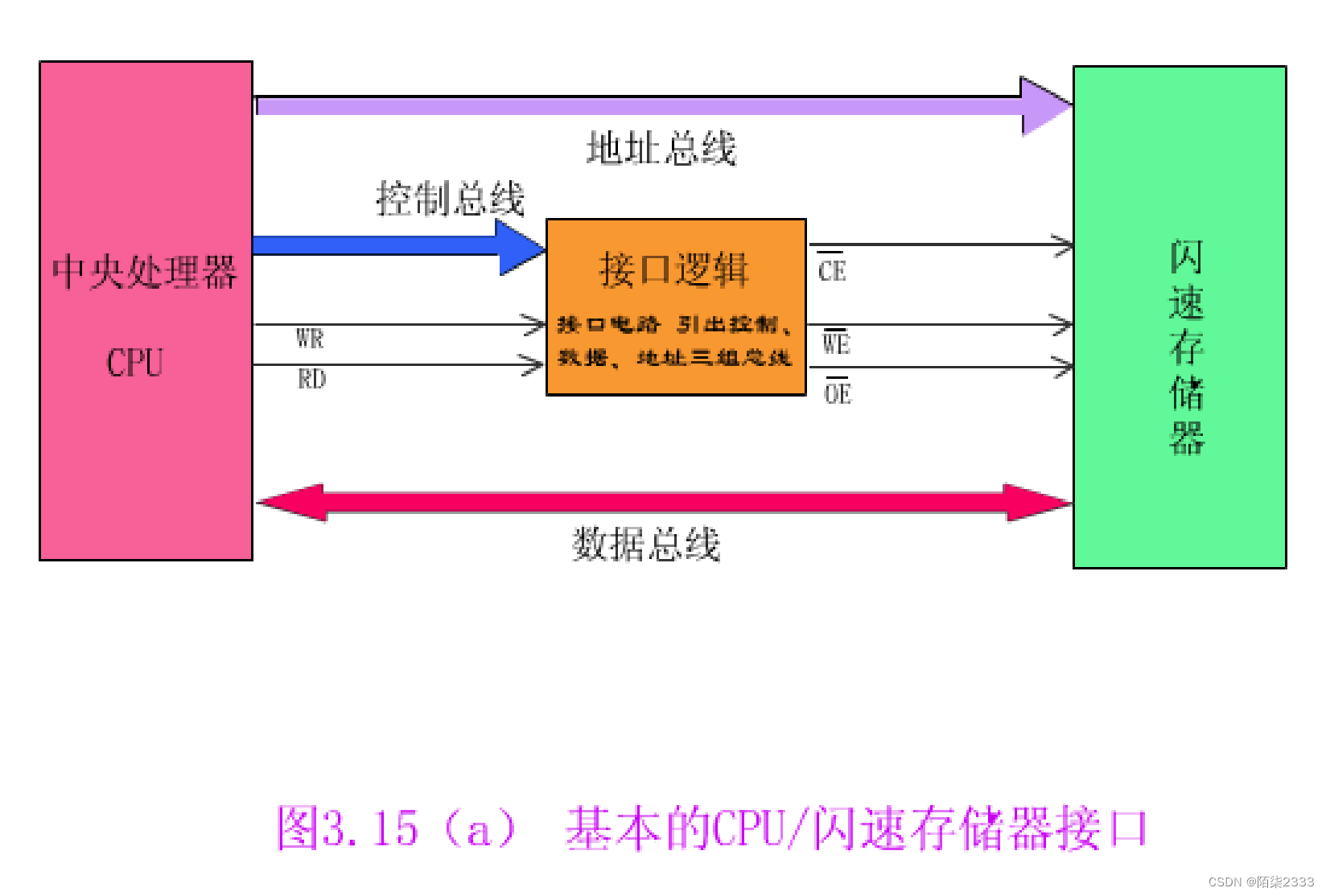

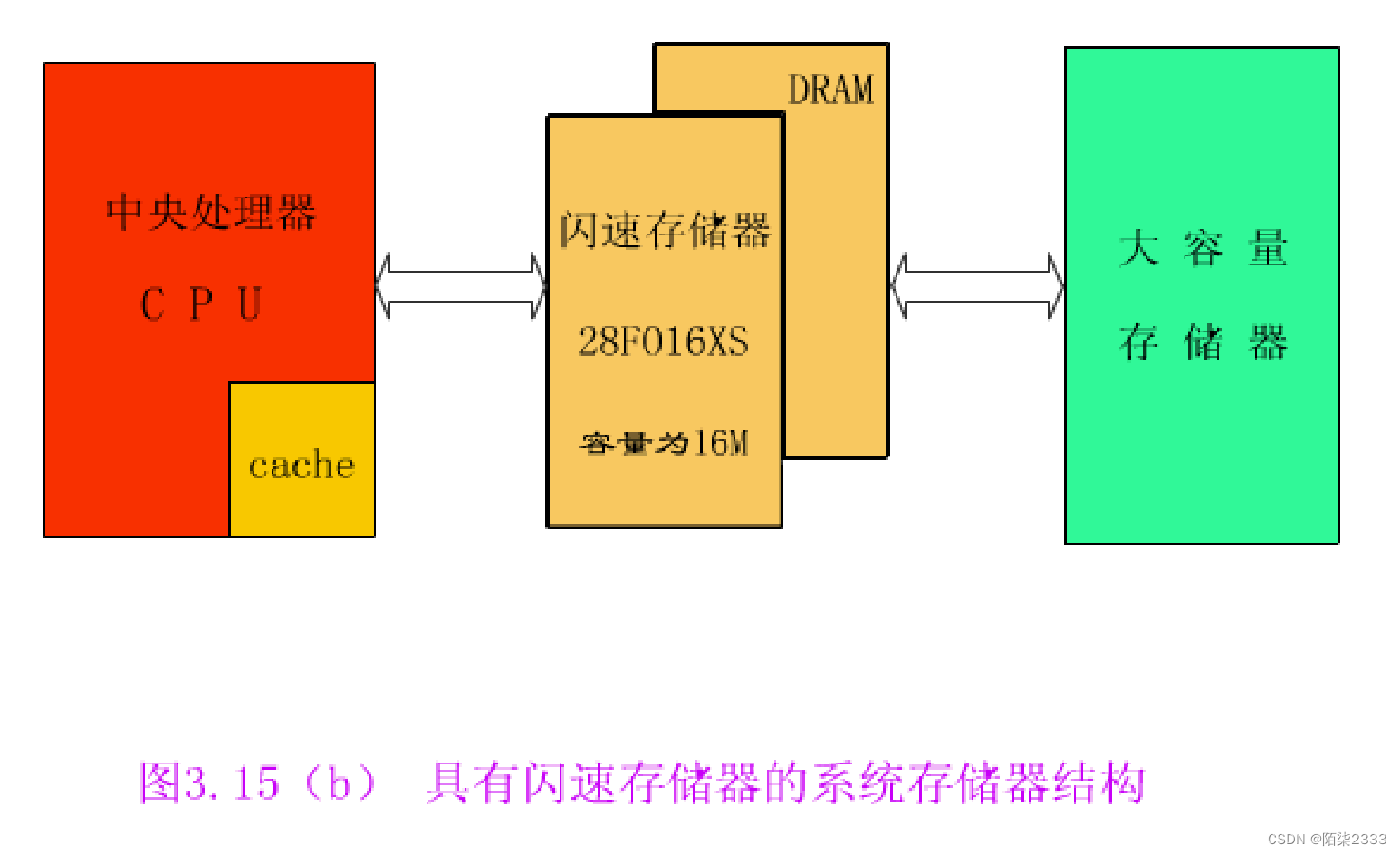

闪速存储器与CPU的连接

三部分通过三组信号线连接,地址与控制总线发向存储器和接口电路。地址总线宽度决定存储器的寻址空间;数据总线宽度决定存储器的字长。

例题:

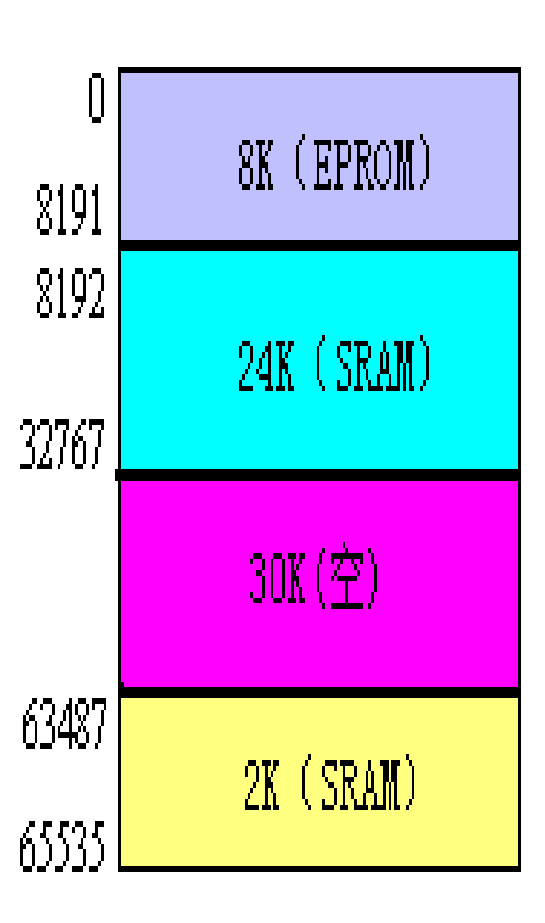

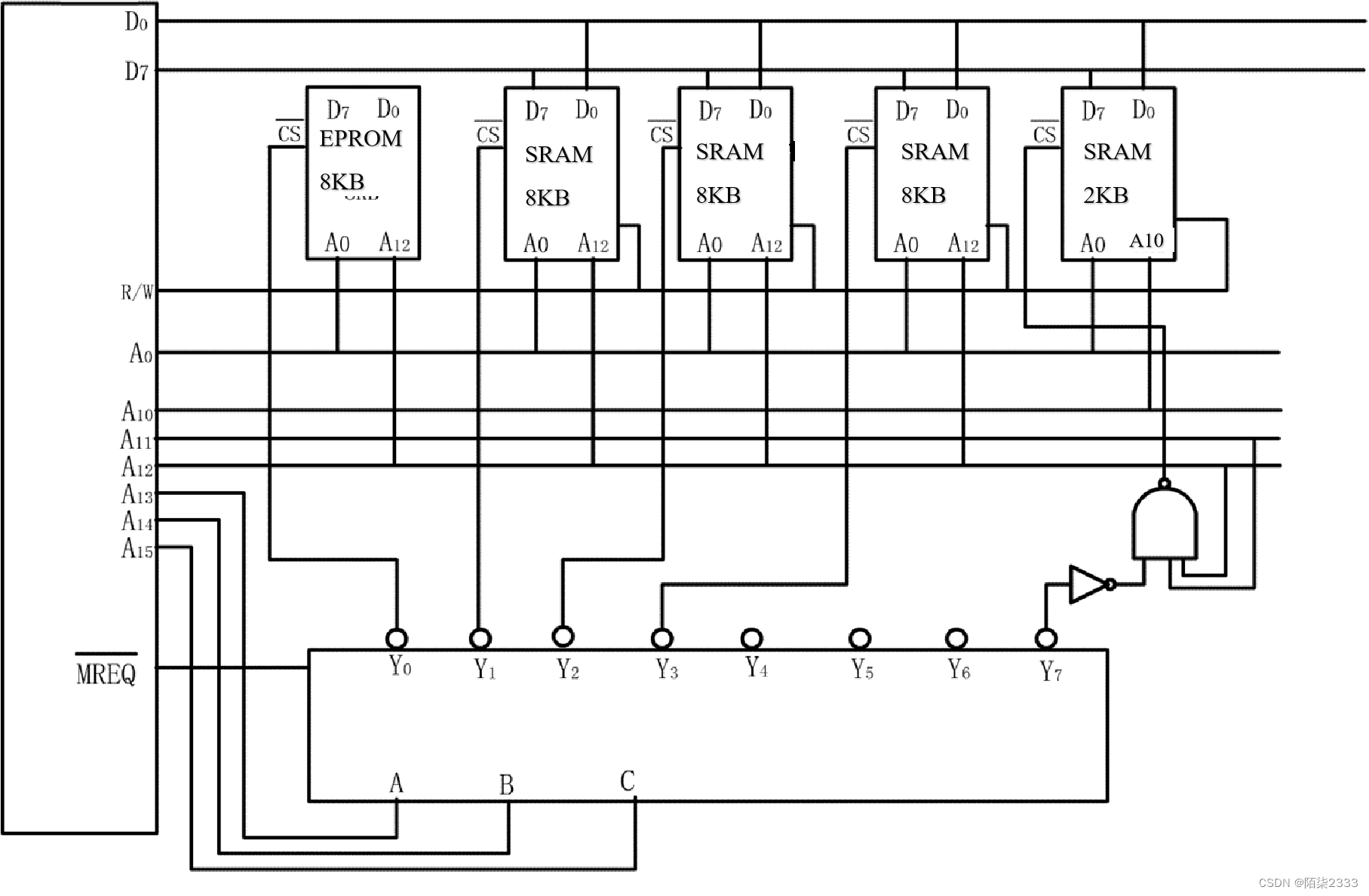

CPU的地址总线16根,双向数据总线8根,控制总线中与主存有关的信号有MREQ(允许访存,低电平有效),R/W(高电平为读命令,低电平为写命令)。 主存地址空间分配如下:0—8191为系统程序区,由只读存储芯片组成;8192—32767为用户程序区;最后(最大地址)2K地址空间为系统程序工作区。上述地址为十进制,按字节编址。现有如下存储器芯片: EPROM:8K×8位; SRAM:16K×1位,2K×8位,4K×8位,8K×8位。请从上述芯片中选择适当芯片设计该计算机主存储器,画出主存储器逻辑框图,注意画出选片逻辑(可选用门电路及3∶8译码器74LS138)与CPU 的连接,说明选哪些存储器芯片,选多少片?

解:主存地址空间分布如图所示。 根据给定条件,选用 EPROM:8K×8位芯片1片 SRAM:8K×8位芯片3片,2K×8位芯片1片。

3∶8译码器仅用Y0,Y1,Y2,Y3和Y7输出端,且对最后的2K×8位芯片还需加门电路译码。

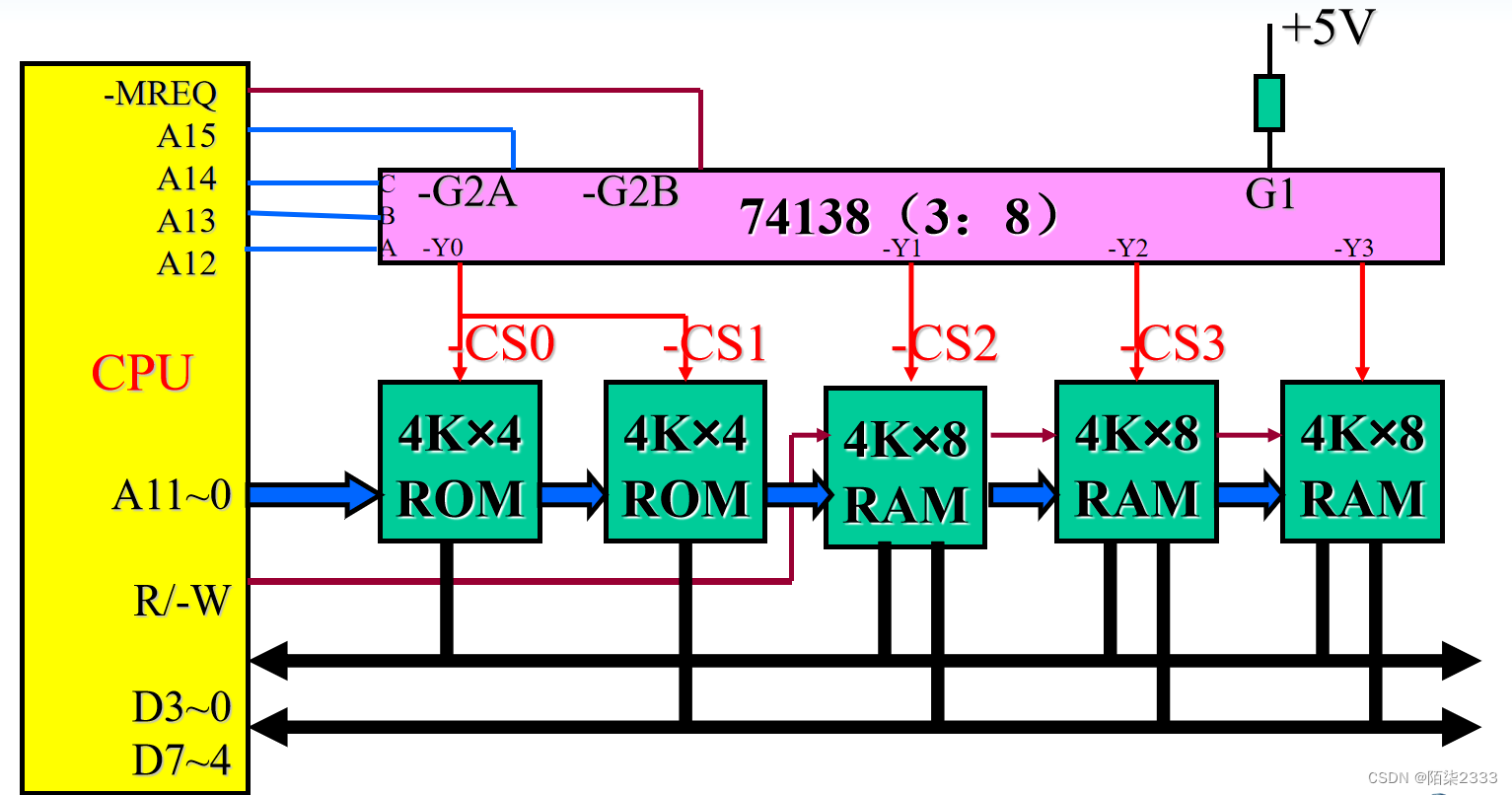

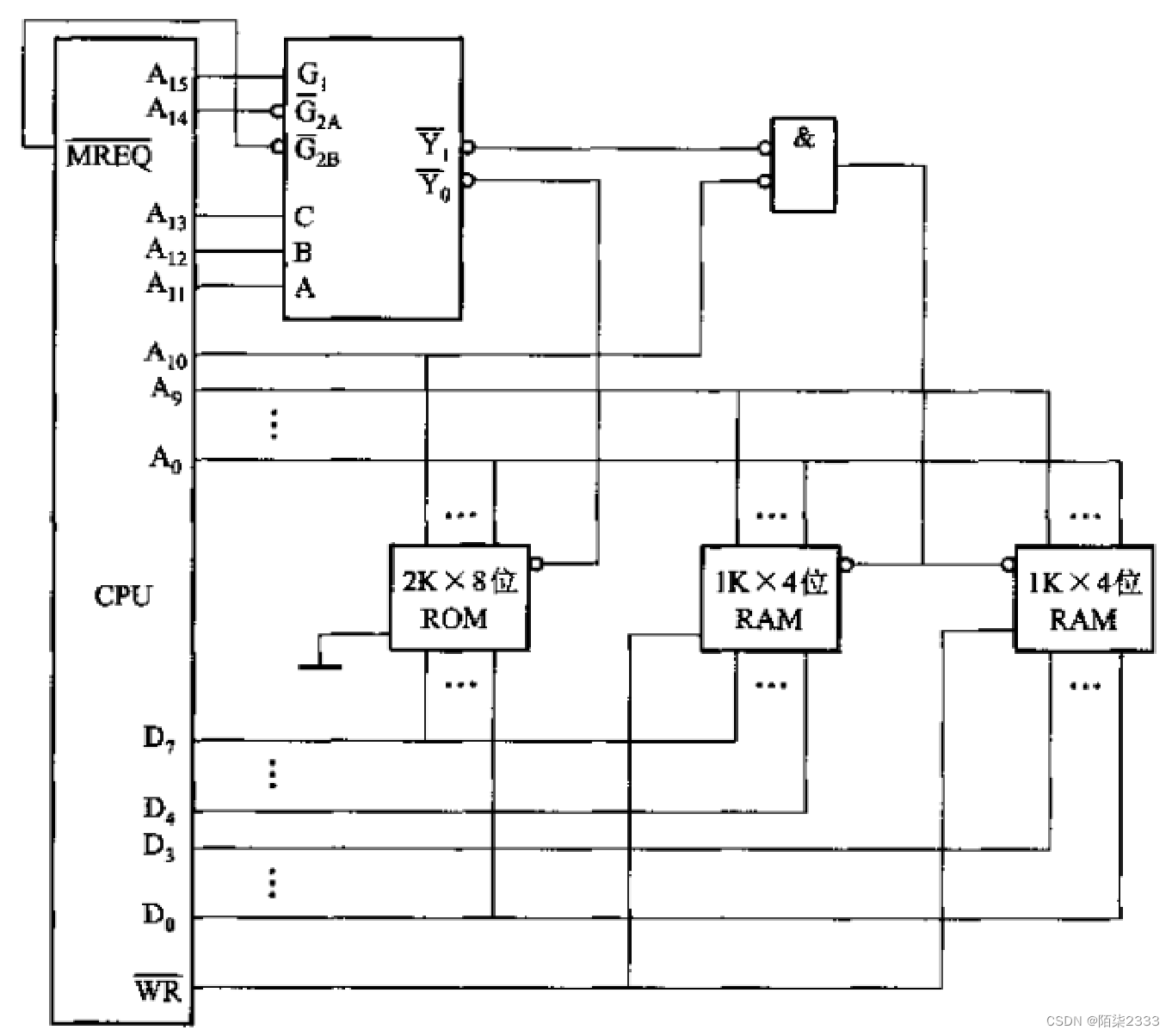

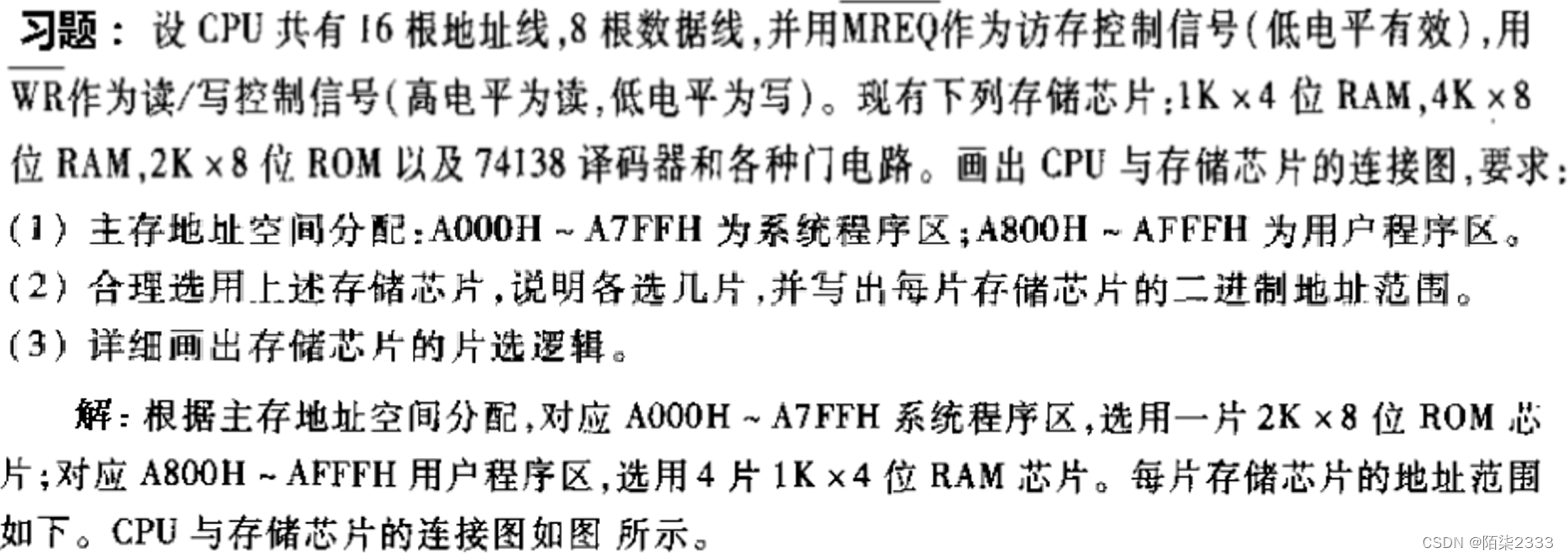

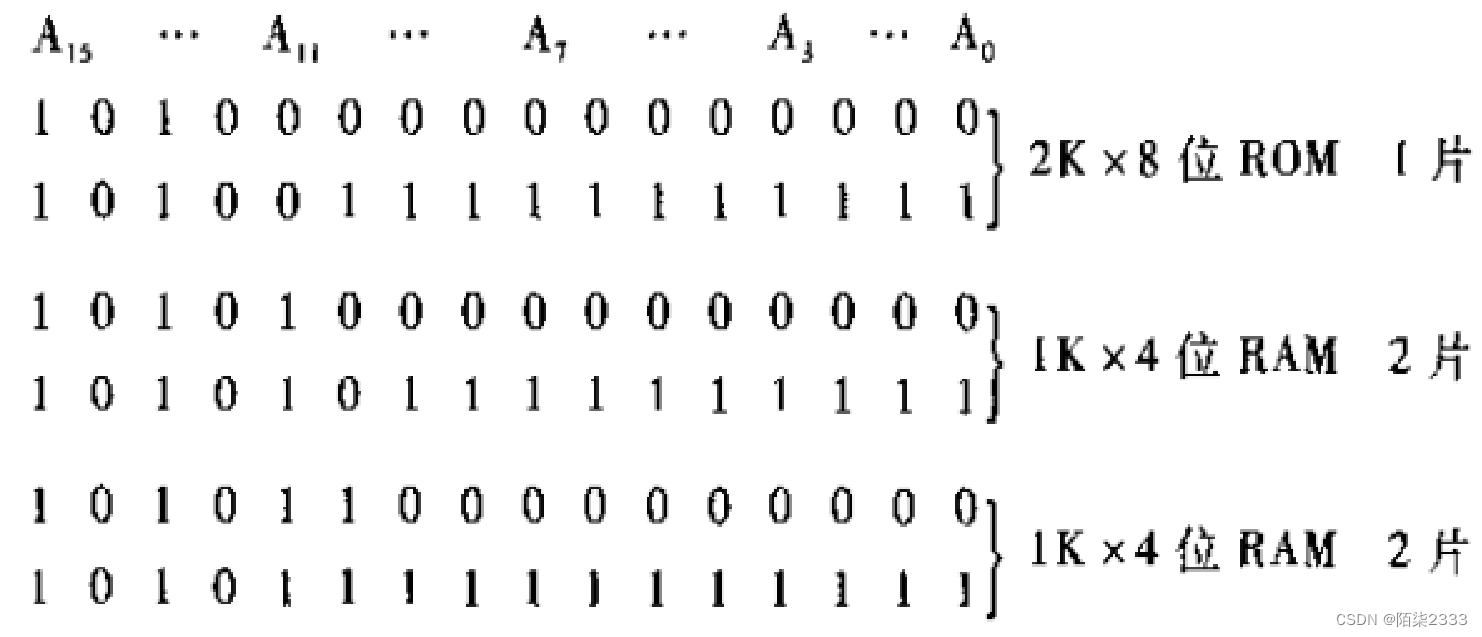

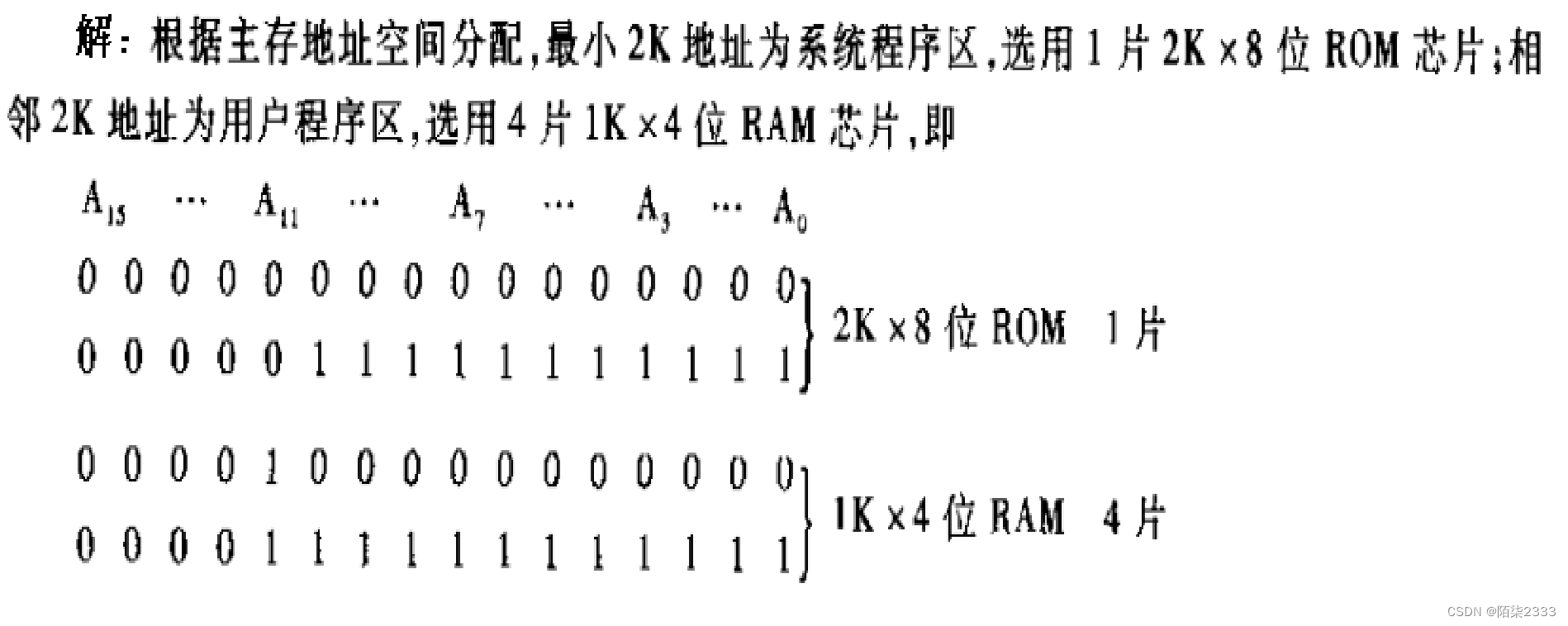

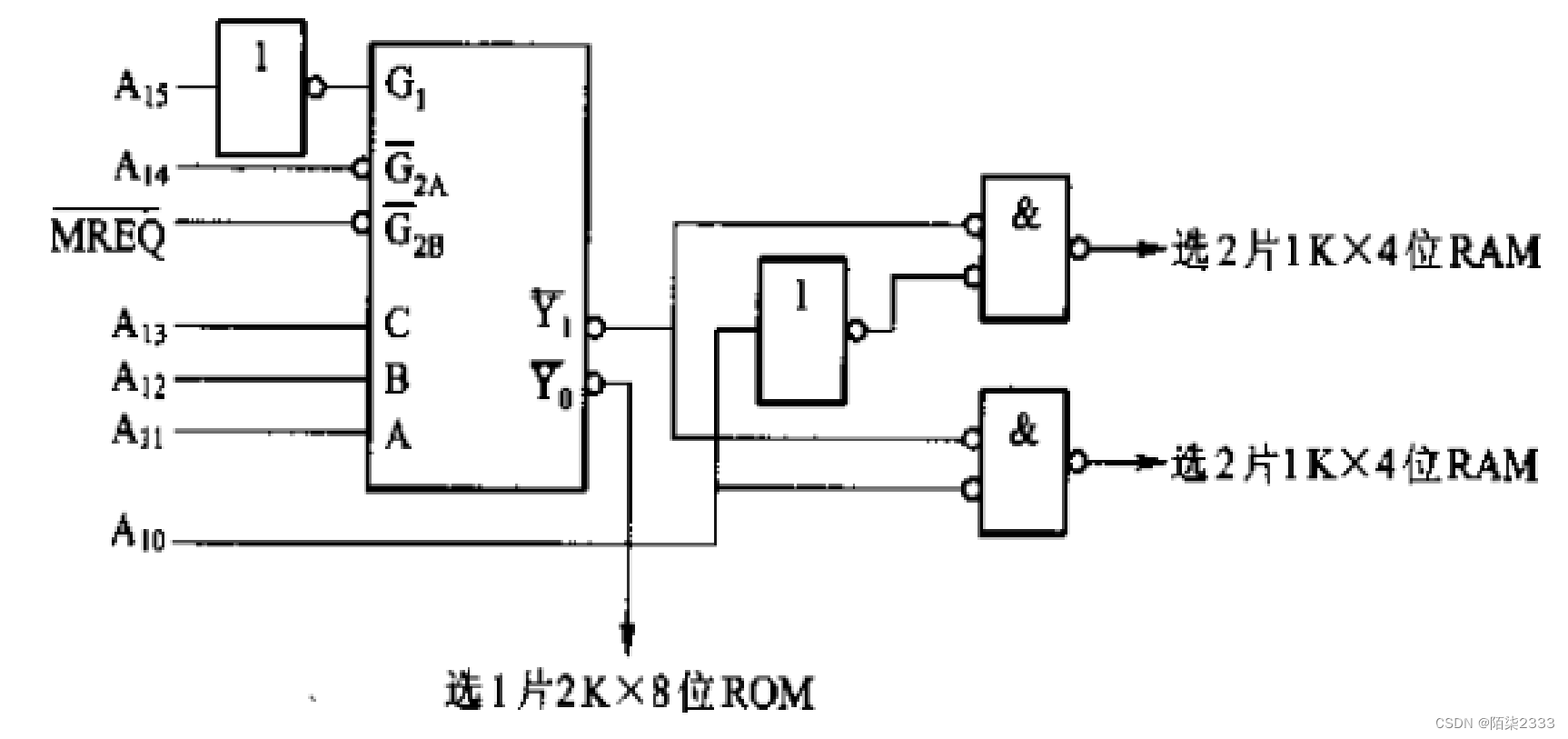

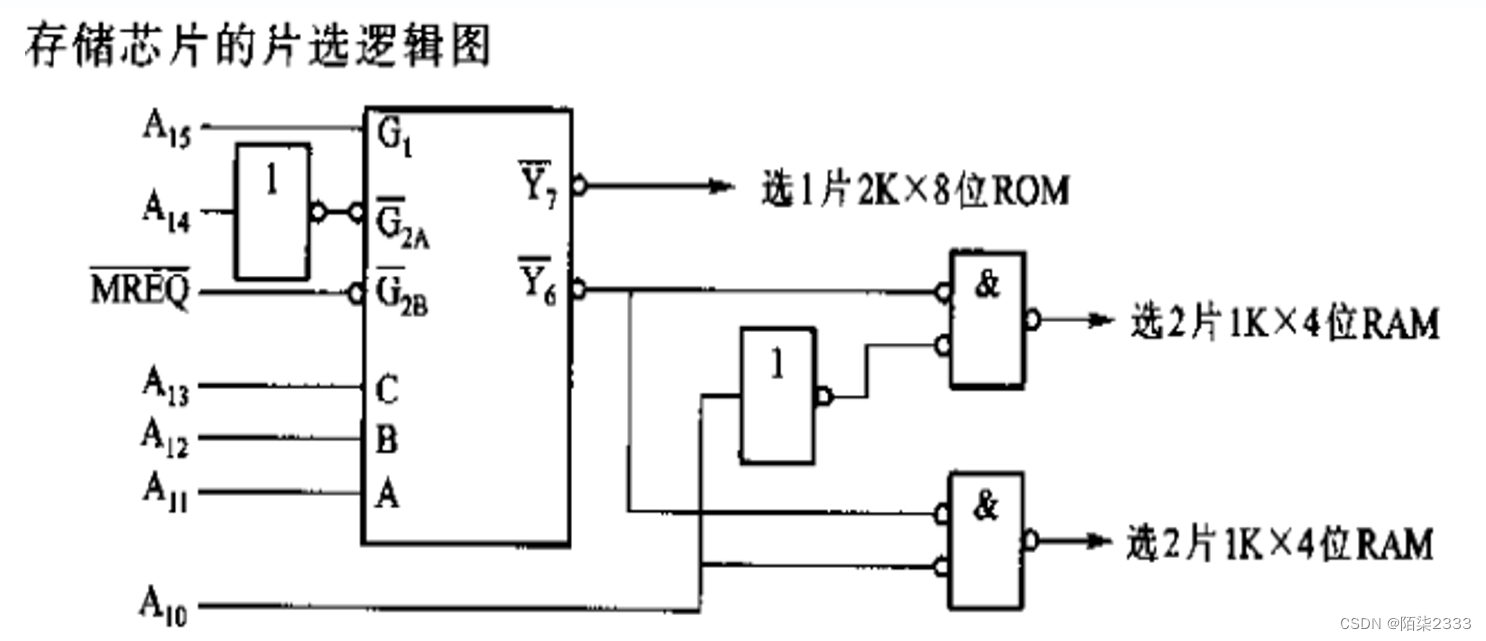

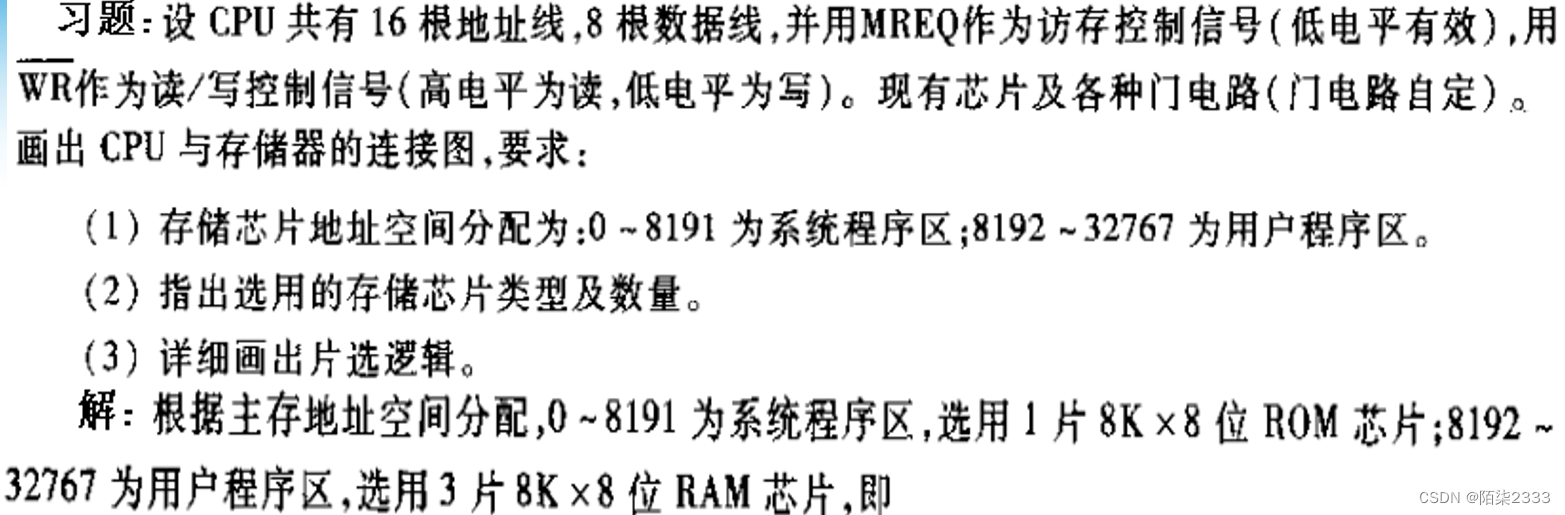

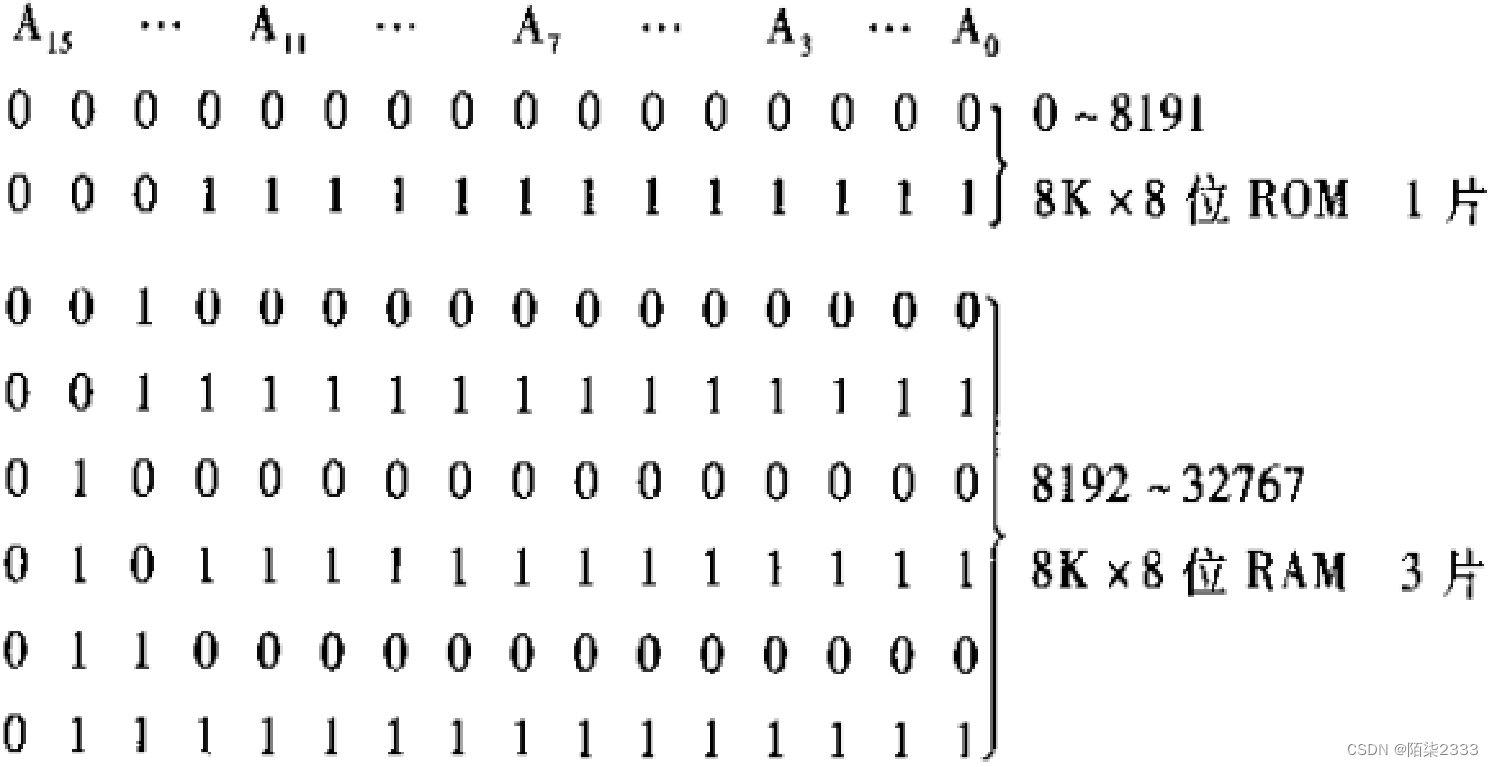

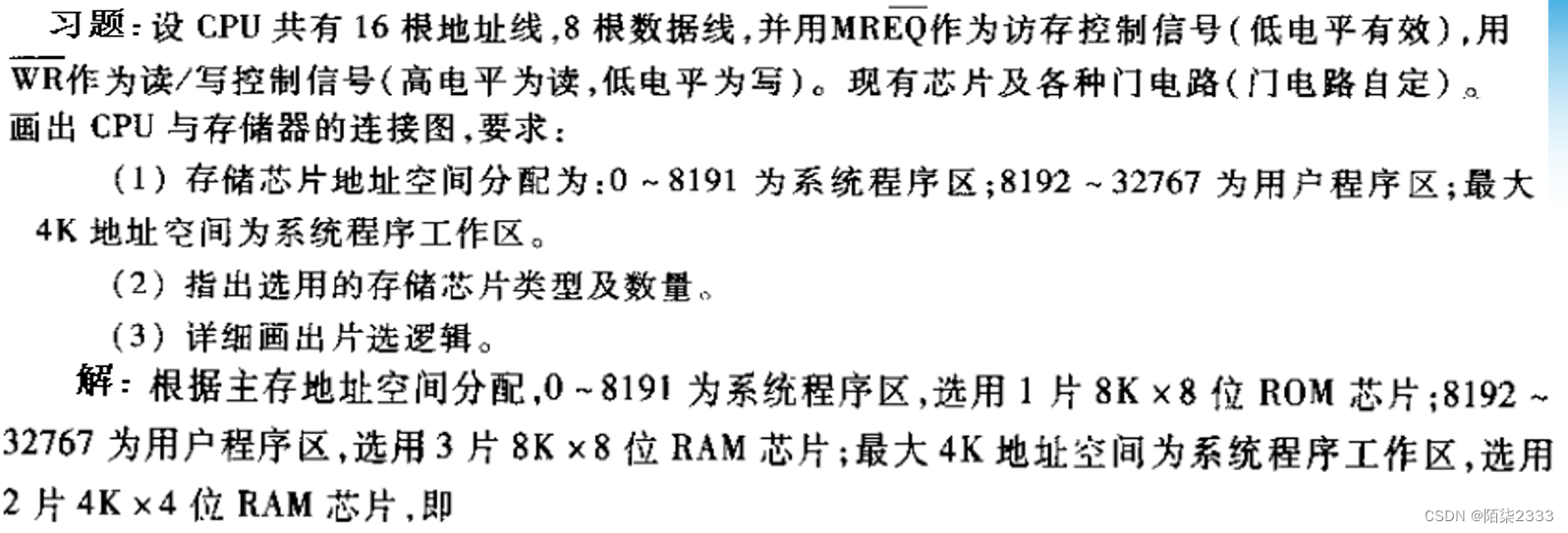

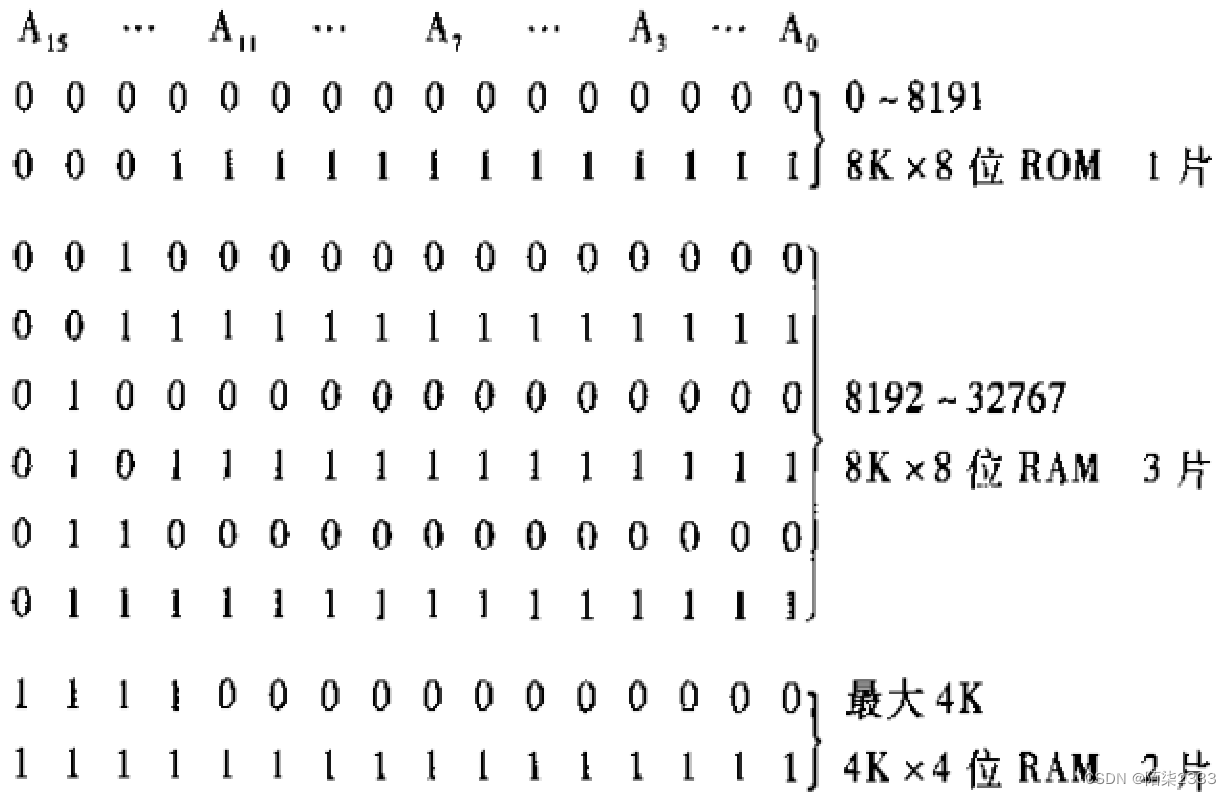

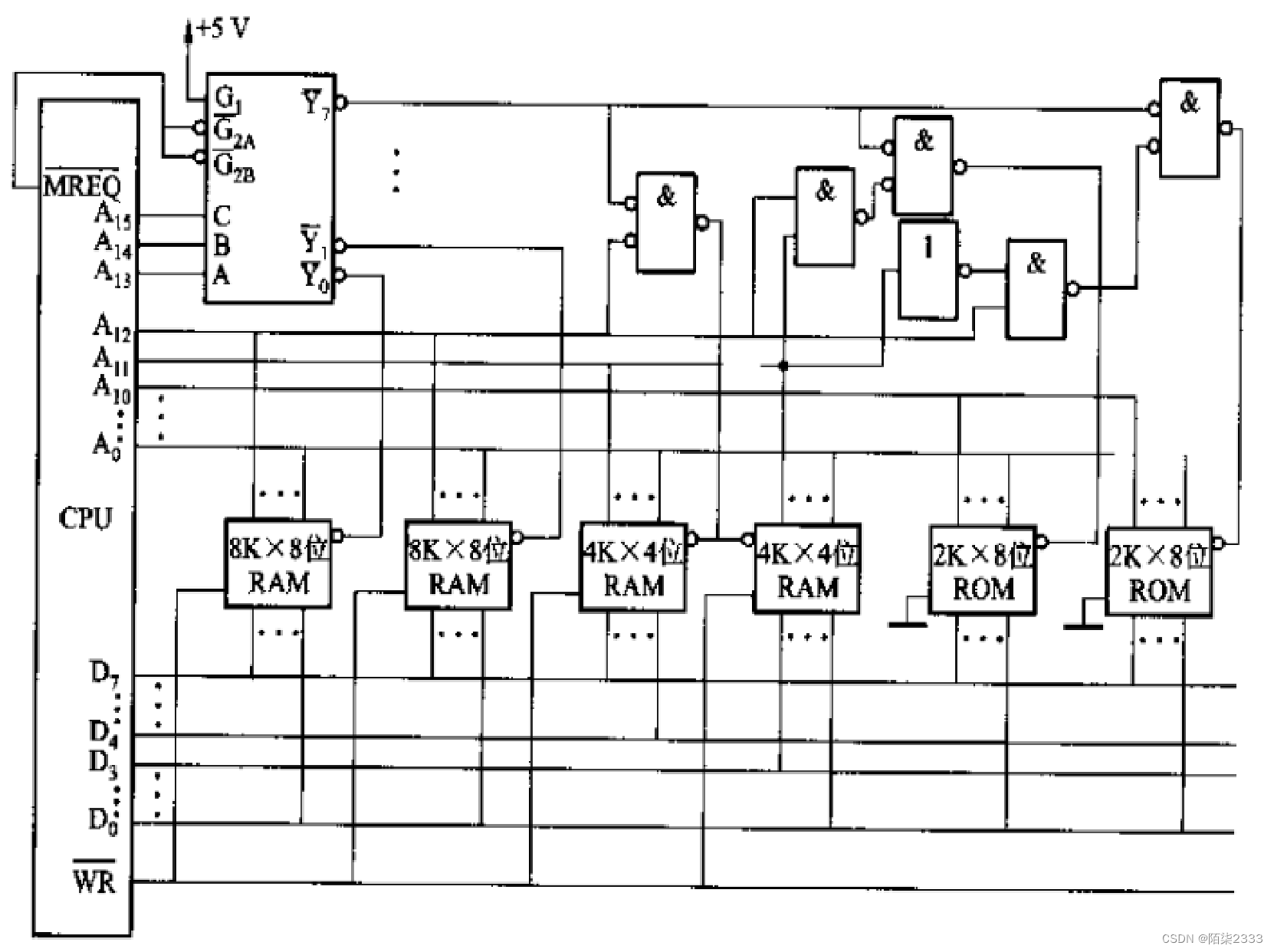

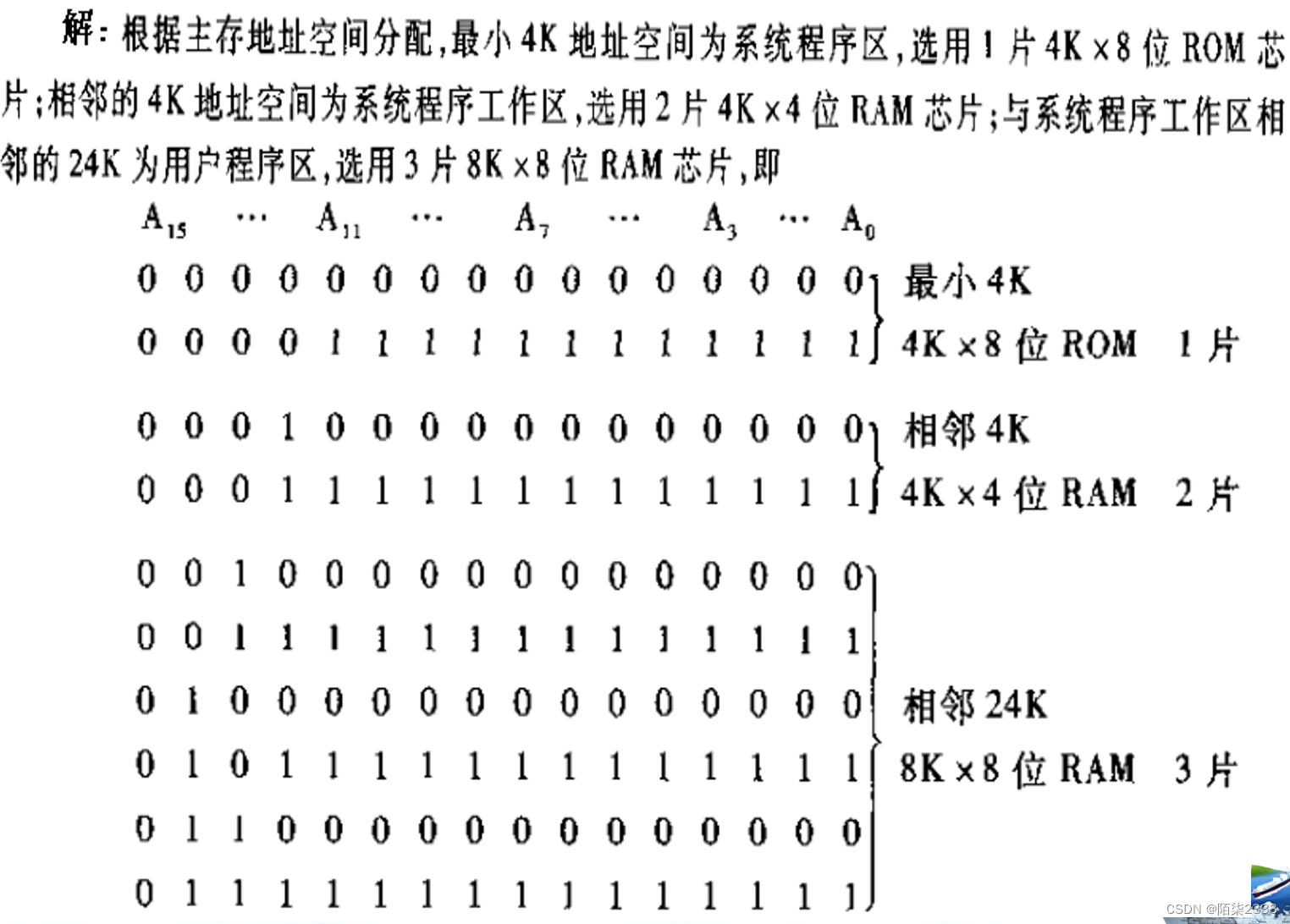

设CPU共有16根地址线,8根数据线,并用MREQ(低电平有效)作访存控制信号,R/W作读/写命令信号(高电平为读,低电平为写)。现有这些存储芯片: ROM(2K×8位,4K×4位,8K×8位),RAM(1K×4位,2K×8位,4K×8位),及74138译码器和其他门电路(门电路自定)。 试从上述规格中选用合适的芯片,画出CPU和存储芯片的连接图。要求如下:(1)最小4K地址为系统程序区,4096~16383地址范围为用户程序区;(2)指出选用的存储芯片类型及数量;(3)详细画出片选逻辑。

解:(1)地址空间分配图如下:

(2)选片:ROM:4K × 4位:2片;RAM:4K × 8位:3片;

(3)CPU和存储器连接逻辑图及片选逻辑:

讨论:

1)选片:当采用字扩展和位扩展所用芯片一样多时,选位扩展。

理由:字扩展需设计片选译码,较麻烦,而位扩展只需将数据线按位引出即可。本题如选用2K×8 ROM,则RAM也应选2K×8的。否则片选要采用二级译码,实现较麻烦。当需要RAM、ROM等多种芯片混用时,应尽量选容量等外特性较为一致的芯片,以便于简化连线。

2)应尽可能的避免使用二级译码,以使设计简练。但要注意在需要二级译码时如果不使用,会使选片产生二意性。

3)片选译码器的各输出所选的存储区域是一样大的,因此所选芯片的字容量应一致,如不一致时就要考虑二级译码。

4)其它常见错误:EPROM的PD端接地;(PD为功率下降控制端,当输入为高时,进入功率下降状态。因此PD端的合理接法是与片选端-CS并联。ROM连读/写控制线-WE;(ROM无读/写控制端)

注:该题缺少“系统程序工作区”条件。

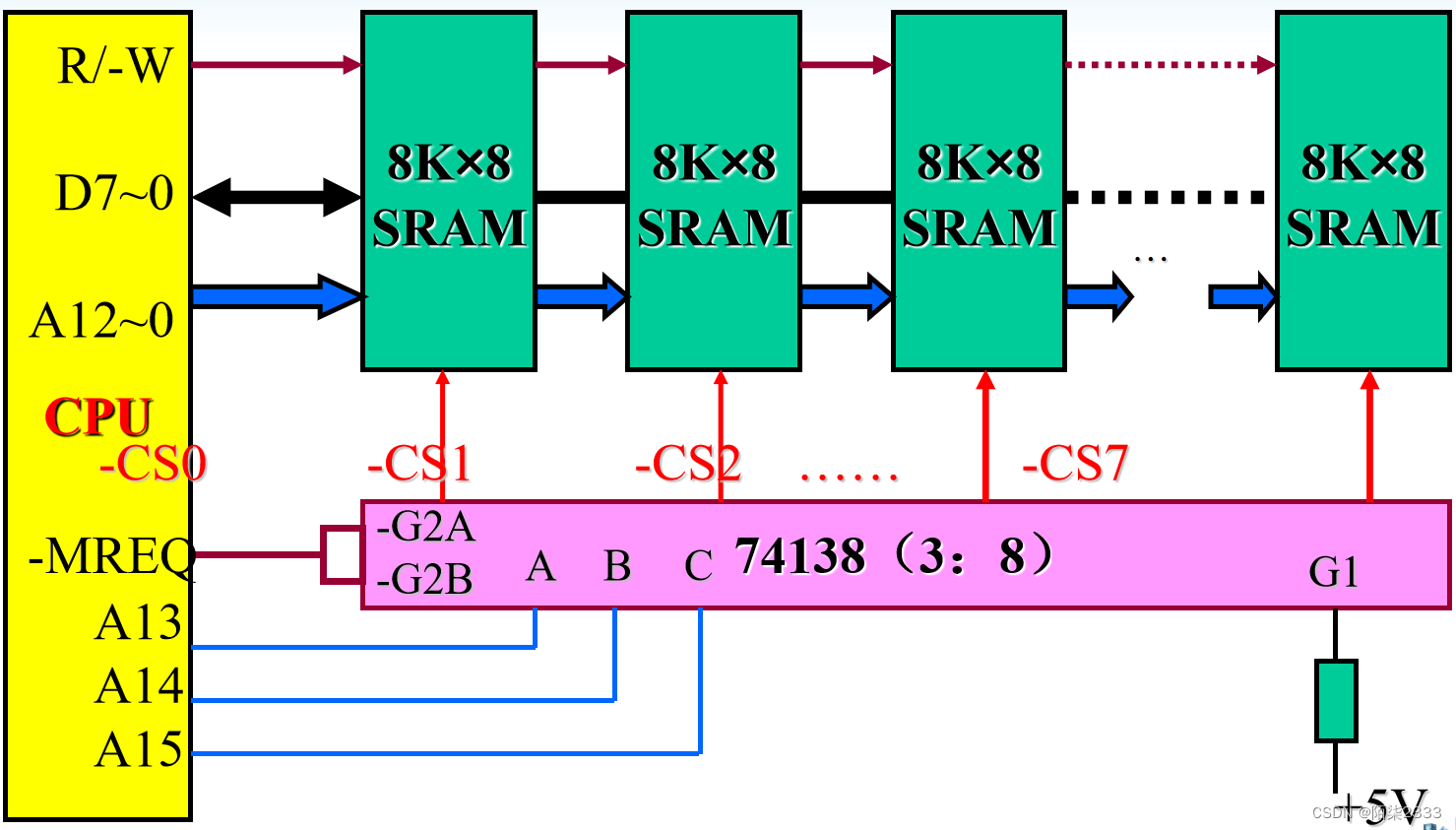

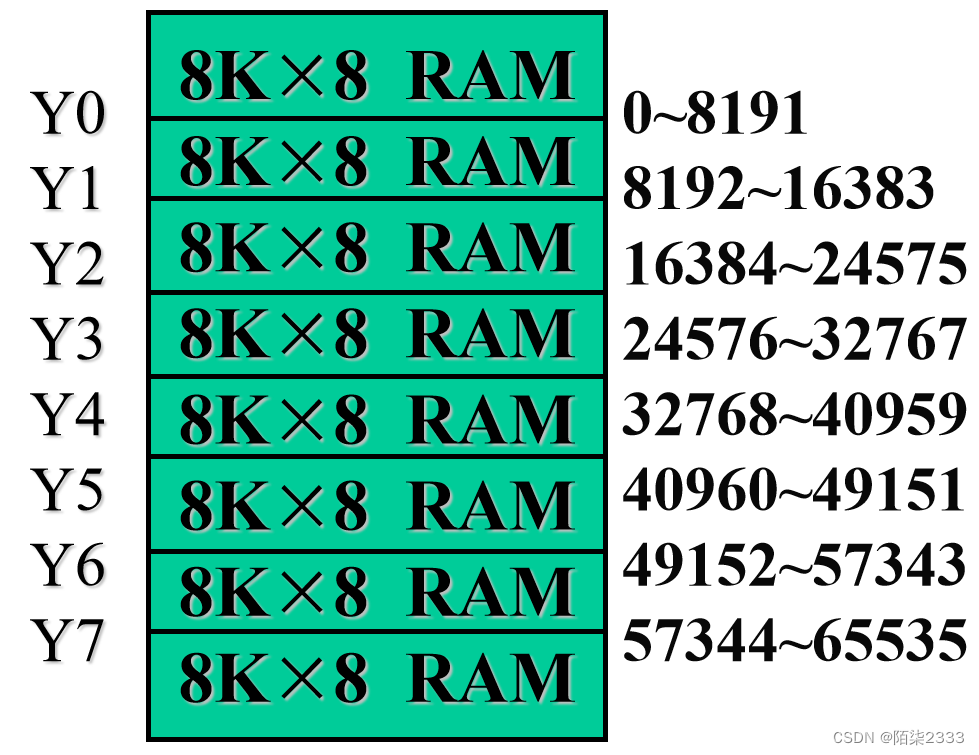

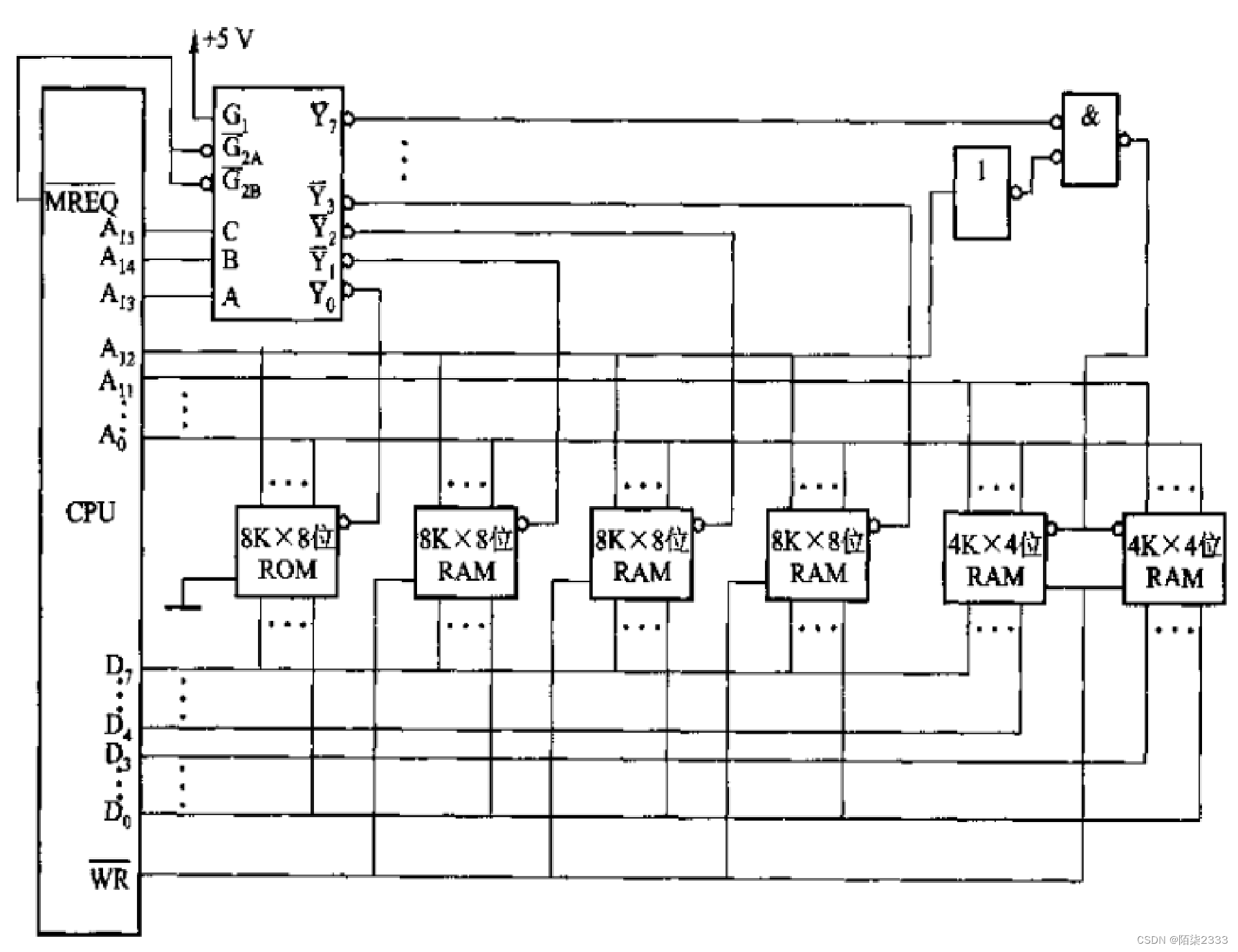

CPU假设同上题,现有8片8K×8位的RAM芯片与CPU相连。

(1)用74138译码器画出CPU与存储芯片的连接图;

(2)写出每片RAM的地址范围;

解:

(1)CPU与存储器芯片连接逻辑图:

(2)地址空间分配图:

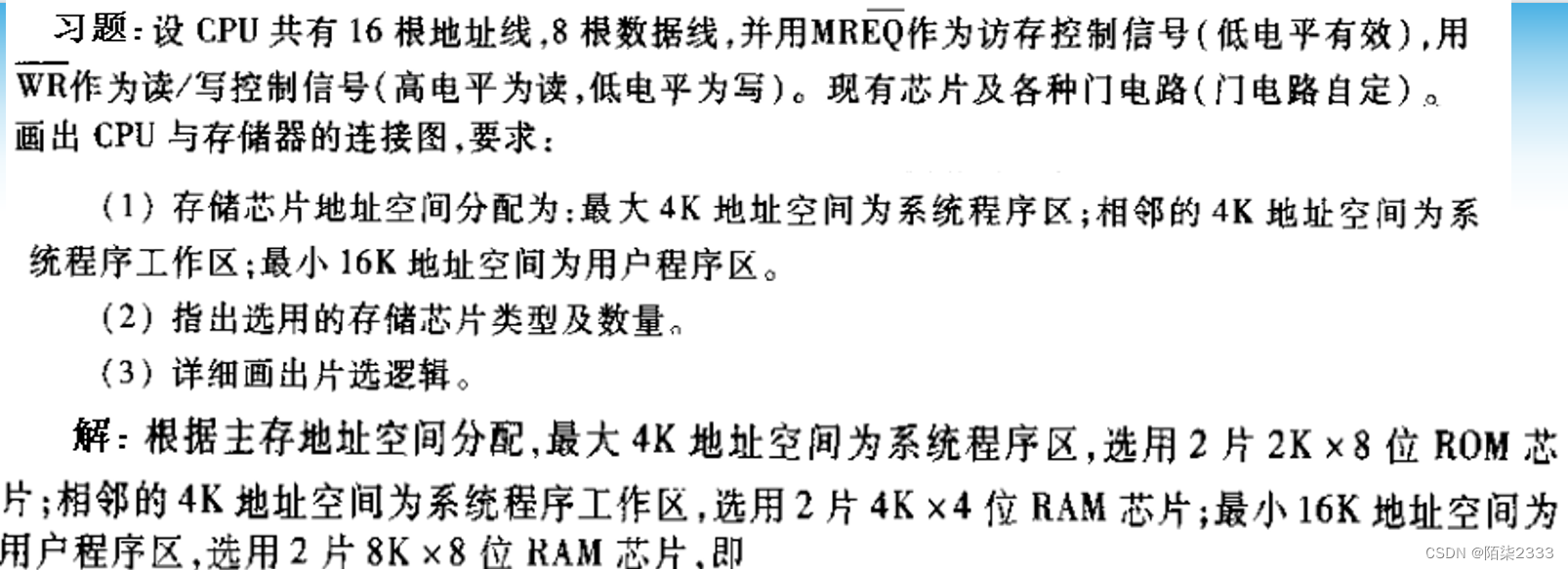

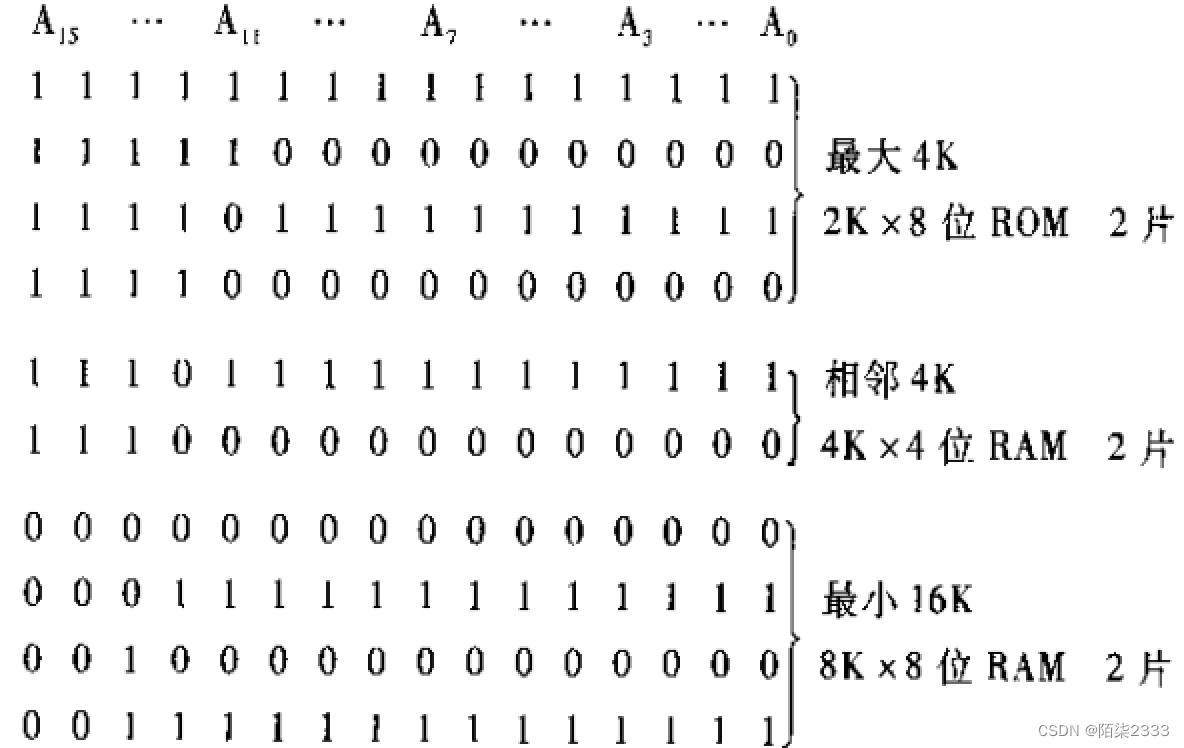

3.练习:

这篇关于计算机组成原理(超详解!!) 第五节 只读存储器和闪速存储器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!