本文主要是介绍文献阅读(156)异构集成,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- introduction

- 1 introduction

- 题目:A 256Gb/s/mm-shoreline AIB-Compatible 16nm FinFET CMOS Chiplet for 2.5D Integration with Stratix 10 FPGA on EMIB and Tiling on Silicon Interposer

- 时间:2021

- 会议:CICC

- 研究机构:密西根大学

introduction

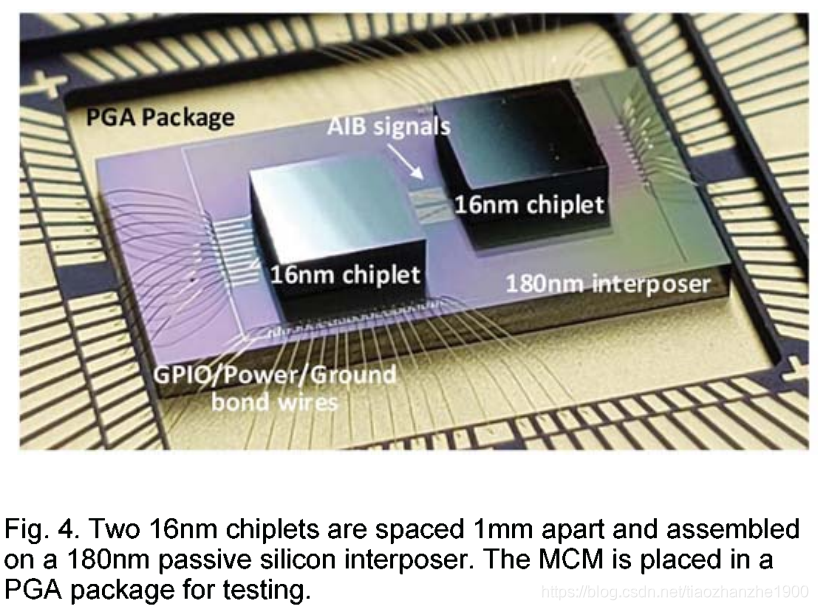

这篇论文有两个Multi-chip modules(MCM),一个是MCM用180nm被动硅基板集成的两个16nm chiplet,一个是Stratix10 FPGA芯片和16nm chiplet通过EMIB总线互联。

This work presents an Advanced Interface Bus (AIB) - compatible microcontroller unit (MCU) chiplet in 16nm FinFET CMOS.

Two multi-chip modules (MCM) were constructed, one made of two MCU chiplets integrated on a 180nm passive silicon interposer, and the other made by pairing an MCU chiplet with a Stratix 10 FPGA over an Embedded Multi-die Interconnect Bridge (EMIB)

- 题目:PETRA: A 22nm 6.97TFLOPS/W AIB-Enabled Configurable Matrix and Convolution Accelerator Integrated with an Intel Stratix 10 FPGA

- 时间:2021

- 会议:VLSI

- 研究机构:UM

1 introduction

本篇论文的主要贡献:

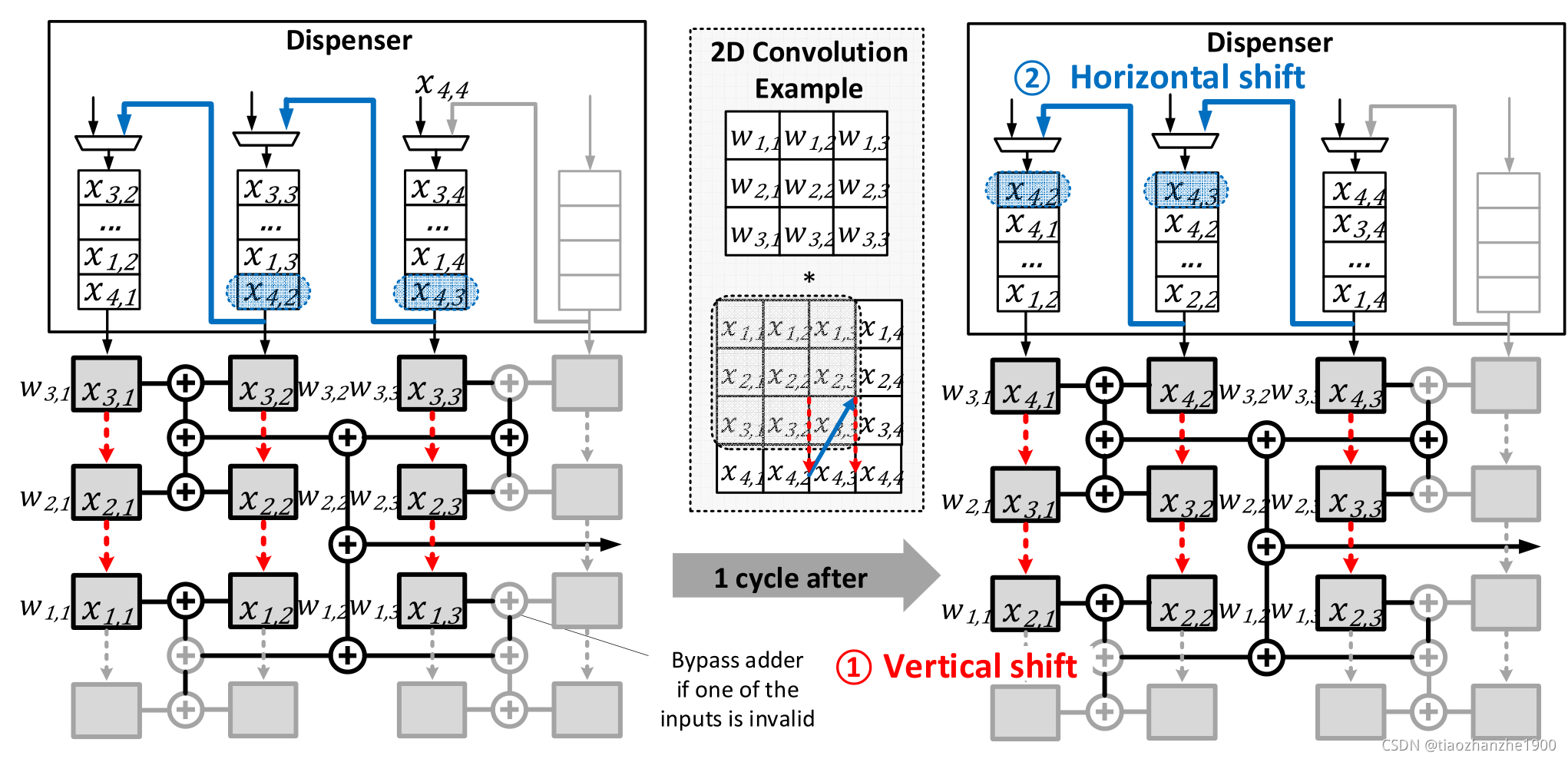

- 16x16脉动阵列实现矩阵乘与卷积运算,通过可配置的H树提高硬件利用率

- 通过自定义与AXI兼容的接口UMAI,实现Stratix 10 FPGA与卷积加速器的异构chiplet集成

为什么要提出类似AXI接口的AIB接口?

Abstracts the die-to-die interface to an SoC-like bus, and hence simplifies a chiplet integration to an IP integration

这篇关于文献阅读(156)异构集成的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!