本文主要是介绍GT收发器第一篇_总体结构介绍,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 前言

- GT收发器介绍

前言

之前写过一篇简单介绍GT的文章https://blog.csdn.net/m0_56222647/article/details/136730026,可以先通过这篇文章对整体进行简单了解一下。

GT收发器介绍

参考xilinx手册ug476

对于7系列的FPGA,共有3个系列,每个系列都有各自的高速收发器,称为吉比特收发器,即Gigabit Transceiver,简称为GT。

每个系列的GT叫法略有不同,分别为:A7 的GTP,V7的GTH,K7的GTX,少量V7的GTZ。它们之间的区别在于最高线速率不同,GTZ>GTH>GTX>GTP。结构大致相同。

以K7为例:

可见,一个K7的FPGA的Transceiver总体架构是由4个GTX QUAD,每个GTX QUAD包含4个GTX Channel,故该FPGA包含16个GTX Channel,也就说我们常说的,有16个GTX Transceiver。

一个GT QUAD组成如下:

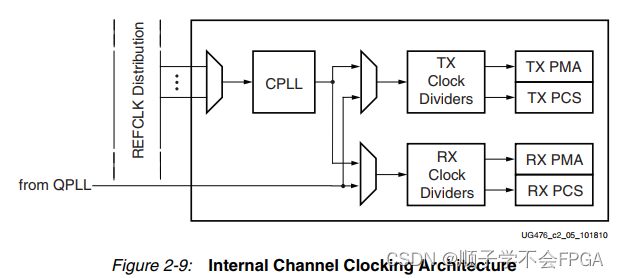

一个QUAD由4个GTXE2_CHANNEL源语和一个GTXE2_COMMON原语构成。其GTXE2_COMMON原语包含一个QPLL,之所以叫做QPLL,其中的Q含义就是QUAD,即一个GTX QUAD公用的PLL。每一个GTXE2_CHANNEL原语由:1个Channel PLL,即CPLL,1个Transmitter,1个Receiver组成。之所叫叫CPLL,即Channel PLL,含义是每一个Channel单独拥有的PLL。

图中上半部分为Transmitter的结构,可见其由:PCS、PMA组成。Receiver也是由:PCS、PMA构成。Transmitter的数据流大致为:FPGA用户逻辑的数据,进入FPGA TX接口,进入PCS,再经过PMA,转换为高速串行数据输出。Receiver的数据流大致为:数据由PMA部分结构,转换为并行数据进入PCS,再经过RX接口输出给FPGA用户逻辑处理。

PMA(Physical Media Attachment, 物理媒介适配层) 的功能为:串并转换(图中的SIPO-串入并出和PISO-并入串出)和模拟部分;

PCS(Physical Coding Sublayer, 物理编码子层) 中的功能, 都是并行的数字电路处理。理论上说GTX的最小必要单元就是PMA, 其主要原因就是核心的模拟部分。 而PCS理论上可以全部由FPGA普通逻辑来实现。 当然作为硬核提供的PCS功能更多、 性能更好、 使用更方便。

PCS以及PMA使用的时钟来源于CPLL或者QPLL,经过分频提供给PCS以及PMA,如下图:

这篇关于GT收发器第一篇_总体结构介绍的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!