本文主要是介绍数字下变频(DDC)基础知识,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

数字下变频(DDC)基础知识

偶然间读到的国外技术博客,写的不错,翻译后供大家参考。不知道如何征求原博主同意,如果此翻译涉及侵权的话,请及时联系我删除。

本文讨论了数字下变频(DDC),一种广泛应用于数字无线电接收机的技术。 将DDC与传统的双下变频接收机进行了比较,说明了使用DDC的优点。 本文还举例说明了DDC的工作原理以及它如何消除模拟元件的一些缺点。

文章目录

- 数字下变频(DDC)基础知识

- 基本双下变频接收机

- 传统无线电接收机的缺陷及解决方法

- 数字下变频

- 结语

数字下变频是数字无线电接收机中广泛应用的一种数字信号处理技术。

数字下变频是广泛用于数字无线电接收机中的数字信号处理技术。 本文将回顾数字下变频器(DDC)的基础知识。 我们首先来看看使用DDC而非模拟DDC的优势。 然后,我们将讨论一个示例,探索DDC的基本操作。

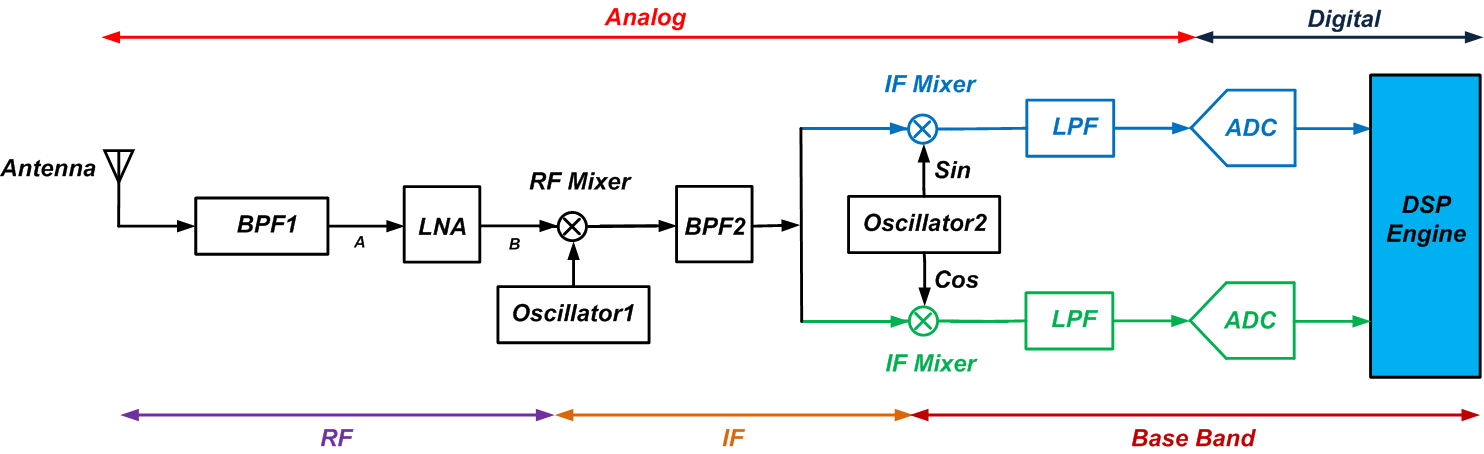

为了了解使用DDC的优势,我们首先回顾一下传统的双通道下变频接收机并分析其缺点。 基本的双通道下变频接收机如图1所示。 如您所见,信号在被模数转换器(ADC)数字化之前,有几个模拟模块。

图1

以下部分回顾了上述接收器中使用的每个模块的基本功能。 如果您熟悉RF工程的基础知识,您可以通过下一节来更新您的知识;否则,您可能需要先阅读AAC的RF教科书。

基本双下变频接收机

在图1的接收机中,第一带通滤波器BPF 1对图中标记为“RF混频器”的第一混频器执行镜像抑制。 它还部分抑制了天线拾取的干扰。 这放宽了低噪声放大器(LNA)的线性度要求。

带通滤波器的输出由LNA放大。 这种放大使得由后续级贡献的噪声与期望信号相比相对较小。 以此方式,接收器变得对LNA之后的级的噪声较不敏感。

然后,RF混频器将节点B处的放大信号下变频到中频 f I F f_{IF} fIF。

既然所需信号已下变频至较低频率,我们就可以更轻松地构建一个Q值相对较高的滤波器BPF2,并部分执行通道选择。 注意,由于接收机的双下变频结构,第一混频器的中频 f I F f_{IF} fIF可以相对较高。 这放宽了BPF1的要求。

接下来,信号通过振荡器2驱动的正交混频器(见图1)。 振荡器2的频率等于 f I F f_{IF} fIF,使得期望频带的中心频率将被转换为DC。 这意味着IF混频器不需要镜像抑制滤波器。

接下来,我们通过基带低通滤波器(LPF)执行通道选择,最后,ADC将对所需信号进行数字化,结果将由数字信号处理器(DSP)进一步处理。 DSP引擎将执行诸如均衡、解调和信道解码之类的操作。

传统无线电接收机的缺陷及解决方法

我们可以考虑图1所示双通道下变频接收机的三个主要局限性:

- 两条基带路径必须高度匹配。 蓝色路径中的IF混频器、LPF和ADC必须与绿色路径中的相应元件匹配。

- 模拟滤波器会引入相位失真。

- ADC会注入一个直流项,该直流项不易从所需信息中去除。 请注意,图1中的IF混频器将所需通道的中心频率转换为DC,ADC可能会注入误差项。 此ADC失调可能由其构建模块(如放大器和比较器)的失调产生。 失调项导致非零数字码,即使向ADC施加零信号也是如此。 这在以非常低的频率传送信息的系统中可能非常重要。

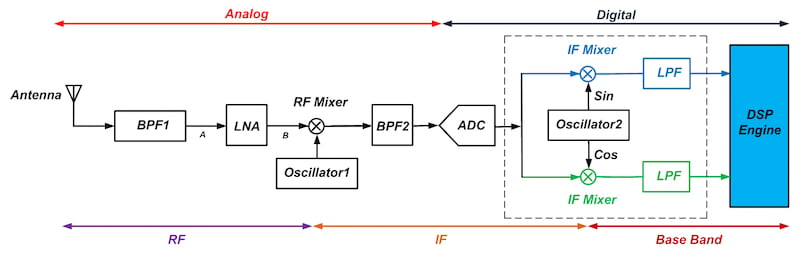

我们可以在接收机的DSP部分中弥补这些缺陷;然而,更好的解决方案是将A/D转换器置于接收机链中的正交混频器之前。 如图2所示。

图2

如图所示,现在模数转换在中频而不是基带进行。 这意味着ADC必须以更高的采样速率工作。 如图所示,ADC之后的模块均在数字域工作。 例如,图2中振荡器2的输出实际上是正弦和余弦信号对应的数字值。 为了实现振荡器2,我们通常使用直接数字频率合成器(DDS)。 第二次下变频使用两个数字乘法器执行,LPF为数字滤波器。

如上所述,采用图2的结构时,ADC必须以更高的采样速率工作。 这可能被认为是一个缺点,但DDC方法也提供了显著的优势:

- 现在,IF混频器和LPF都是数字电路。 因此,由模拟元件之间的失配引起的不平衡相关失真已被消除。

- 与模拟域不同,我们可以轻松设计线性相位数字滤波器。

- 信号通过IF混频器之前,ADC注入的直流项可以通过数字滤波器轻松消除(示例参见《Digital Front-End in Wireless Communications and Broadcasting》第12章)。

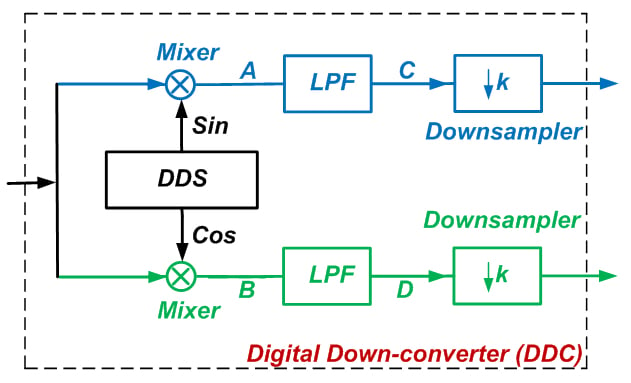

注意,虽然图2中的正交混频器和LPF位于接收机DSP引擎之外,但我们当然可以在系统DSP平台内实现这些模块。 此外,在基带LPF之后,我们可以显著降低采样速率,而不会丢失所需信息(更多信息请参阅我的文章“多速率DSP及其在模数转换中的应用”)。 因此,我们可以重新绘制图2虚线框内的电路,如图3所示。 此模块称为数字下变频器或DDC。

图3

数字下变频

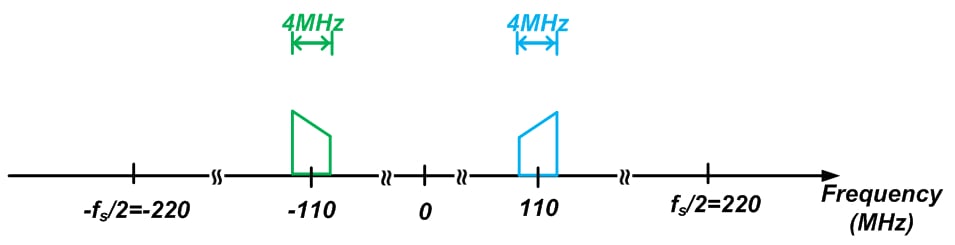

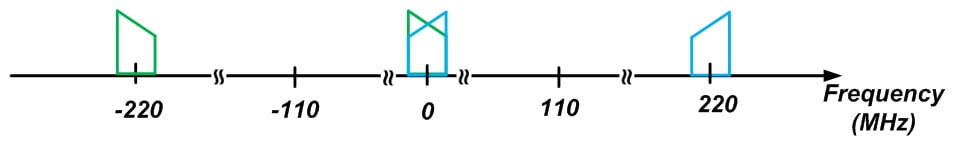

假设经过模数转换后,所需信号的频谱如图4所示。

图4

所需信号的中心频率为110 MHz,带宽为4 MHz(图中显示了正频率和负频率)。 此外,我们假设ADC以440 MSPS(每秒百万样本数)的速率产生样本。 DDC将如何处理此输入?

DDC采用的DDS将产生 110 M H z 110 MHz 110MHz正弦和余弦信号。 这些正弦和余弦函数中的每一个都将产生 ± 110 M H z ±110 MHz ±110MHz的脉冲。 由于时域中的乘法对应于频域中的卷积,因此我们将得到图3中节点A和B的频谱,如图5所示。

图5

如您所见,± 110 MHz的频移将图4中的蓝色频谱转换为220 MHz和DC。 类似地,绿色光谱被移动到DC和-220MHz。 我们能够对节点A和B使用一个图,因为这两个节点具有相同的振幅特性,并且图5仅传达振幅谱。 节点A的相位谱将不同于节点B的相位谱。

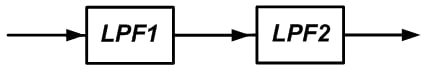

请注意,在图5中,信号边带在下变频后在直流周围重叠。 考虑到这种重叠,我们能否仅使用以DC为中心的频谱部分恢复所需信息? 是的,我们可以;我们使用正交混频,它产生两个相同的幅度谱,但也产生两个不同的相位谱,重叠区域的相位谱允许我们恢复原始信息。 由于这种重叠不是问题,2 MHz以上的频率分量不提供任何必要的信息,因此我们可以在数字混频器之后放置一个LPF,以仅保留2 MHz以下的频率分量。 这种低通滤波在图3中被描绘为单级滤波器,通常被实现为两级滤波器,如图6所示。

图6

第一级LPF 1可用于消除以220 MHz为中心的高频成分。 为此,我们需要一个通带扩展至约2 MHz、阻带从约218 MHz开始的LPF。 这种滤波操作有时称为对DDS产生的镜像信号进行滤波。

第二级LPF 2消除2 MHz至218 MHz之间的任何无用频率成分。 在LPF 2之后,信号不包含超出预期信息带宽的频率分量(即, 2 MHz),但我们仍使用440 MSPS来表示此信号。 因此,我们可以应用下采样概念来降低采样率。

一种更有效的实现方式是将LPF 2分解为级联级,并在这些级中的每一级之后执行整体下采样的一部分。

结语

在本文中,我们分析了使用DDC的好处。 我们看到,DDC可以改善基本双通道下变频接收机的性能:它可以消除模拟IF混频器产生的不平衡相关失真,并避免模拟滤波器的相位失真。 DDC之后,采样速率显著降低,我们可以更高效地实现进一步处理数据的DSP例程。

原文连接:Basics of Digital Down-Conversion in DSP - Technical Articles (allaboutcircuits.com)

这篇关于数字下变频(DDC)基础知识的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!