本文主要是介绍第1章:处理器与MIPS,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.1 计算机的简单模型

1.1.1 计算机的简单组成模型

- 3大部分:处理器(cpu),输入输出(IO),存储器(memory)

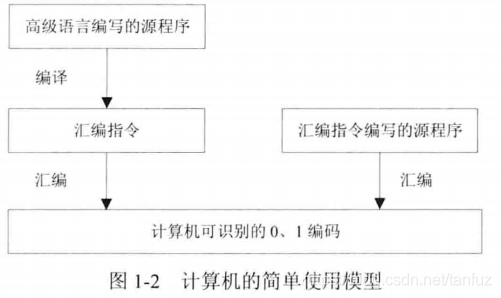

1.1.2 计算机的简单使用模型

1.2 架构与指令集

- IBM引入指令集架构(ISA)的概念,解决不同处理器之间软件代码不兼容的问题,将不同处理器的硬件信息从硬件系统中抽象出来,软件人员面向ISA编程

- 微架构的概念:微架构是ISA的一个实现,比如x86(intel)

- 同样的ISA,不同的微架构,会带来不同的性能

1.2.1 CISC与RISC

- 根据ISA不同将计算机分为两类:复杂指令集计算机(CISC)和精简指令集计算机(RISC),前者每条指令对应的0、1编码长度不一,后长度固定

- 计算机发展早期,采用CISC,其采用变长编码(存储资源昂贵,速度慢),强大灵活指令可以一次性完成很多功能(减少内存访问),但只有20%指令会反复使用

- 后期产生了RISC,使处理器不需要浪费太多晶体管做那些复杂又很少使用的指令,指令种类少,寻址种类少,大量使用寄存器,处理器频率得以提升

1.2.2 主要的集中ISA

- x86:CISC,1978年8086中首次出现,个人计算机标准平台,最成功的指令集架构,目前绝大多数个人计算机处理器都兼容x86指令集架构

- ARM:RISC,低功耗,低成本,主要面向嵌入式应用,智能手机,平板等移动设备

- SPARC:RISC,应用于高性能工作站和服务器

- POWER:RISC,应用于IBM生产的很多服务器,大型机,小型机与工作站

- MIPS:RISC,简单指令+优秀编译器+流水结构,更少晶元面积生产更快处理器,应用于工作站,服务器,十分成功,RISC经典之作,且专利已过期

1.3 MIPS指令集架构的演变

- MIPS I : 8MHz,32位,提供加载/存储,计算,跳转,分支,协处理及其他特殊指令

- MIPS II: 增加了自陷指令,链接加载指令,条件存储指令,同步指令,,可能分支指令,平方根指令

- MIPS III:32位,同时支持64位,主频100MHz,首次加入浮点处理器单元

- MIPS IV:增加条件移动指令,预取指令及浮点指令

- MIPS V:增加了提高代码生产效率和数据转移效率的指令

- MIPS32/64:1998年,第一次包含了被称为协处理器0的cpu控制功能

- microMIPS32/64:集成了高性能代码压缩技术

1.4 MIPS32指令集架构简介

1.4.1 数据类型

指令的任务就是对操作数进行运算,操作数有不同的类型和长度

- 位(b)、字节、半字(16bit)、字、双字(64bit)

1.4.2 寄存器

- RISC大量使用寄存器,其可在一个时钟周期内完成存取操作,同时简化了寻址方式

- MIPS32的指令中除了加载/存储指令外,都是使用寄存器或立即数作为操作数

- MIPS中的寄存器分为两类:通用寄存器(GPR),特殊寄存器

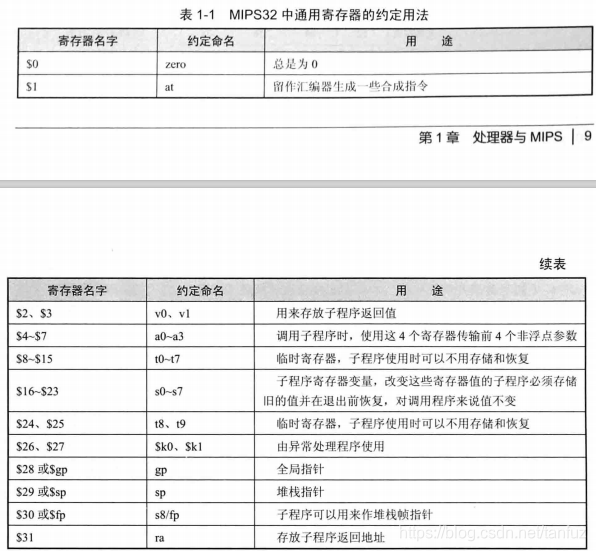

- 通用寄存器:

MIPS32架构定义了32个通用寄存器,各个寄存器使用都遵循一定的约定用法

- 特殊寄存器:

- MIPS32中定义了三个特殊寄存器:PC(程序计数器),HI,LO(乘除结果高位寄存器和低位寄存器)

1.4.3 字节次序

大端模式(MSB)和小端模式(LSB)

1.4.4 指令格式

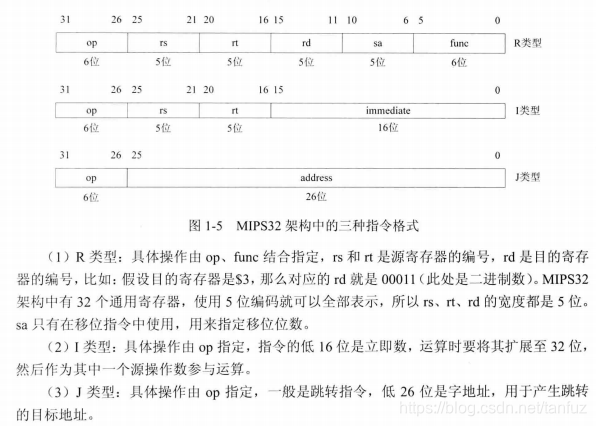

3种格式:

1.4.5 指令集

上述指令直接采用0、1编码,但是不方便,易出错,于是使用汇编程序。

- 逻辑操作指令:8条,与,或,非,异或等

- 移位操作指令:6条,逻辑左移、右移 ;算术右移等

- 移动操作指令:movn,movz等,用于通用寄存器之间的数据移动

- 算术操作指令:21条,加减乘除,乘累加,比较等

- 转移指令:14条,条件转移和无条件转移

- 加载存储指令:14条,L开头表示加载指令,S开头的表示存储指令

- 协处理器访问指令:2条,用于读取协处理器中的某个寄存器的值或者将数据保存到协处理器中某个寄存器

- 异常相关指令:14条,12条自陷指令,和系统调用指令,异常返回指令

- 其余指令:nop,ssnop,sync,pref

1.4.6 寻址方式

- 寄存器寻址、立即数寻址、寄存器相对寻址、PC相对寻址

1.4.7 协处理器CP0

MIPS32架构提供最多4个协处理器,分别是CP0(用于系统控制,包括配置CPU工作状态,高速缓存控制,异常控制,存储单元控制等),CP1、CP3(用于浮点处理单元),CP2保留用于特定实现

1.4.8 异常

- 有些事件会打断处理器运行过程中的取指令、执行指令等正常程序执行流程,如中断、陷阱、系统调用等,统称异常。

- 异常发生后,处理器会转移到一个事先定义好的地址,在那个地址有异常处理例程在其中进行异常处理,改地址称为异常处理例程的入口地址。

这篇关于第1章:处理器与MIPS的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!