本文主要是介绍计算机组成原理-第五章 中央处理器【期末复习|考研复习】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前言

总结整理不易,希望大家点赞收藏。

给大家整理了一下计算机组成原理中的重点概念,以供大家期末复习和考研复习的时候使用。

参考资料是王道的计算机组成原理和西电的计算机组成原理。

文章目录

- 前言

- 第5章 中央处理器及指令

- 5.1 CPU的功能和基本结构

- 5.1.1 CPU功能

- 5.2 指令执行过程

- 5.2.1 取指周期

- 5.2.2 间址周期

- 5.2.3 执行周期

- 5.2.4 中断周期

- 5.3 指令执行方案

- 5.4 数据通路

- 5.4.1 数据通路基本结构

- 5.5 控制器

- 5.5.1 CPU控制方式和功能

- 5.5.2 硬布线控制器

- 5.5.3 微程序控制器

- 5.5.4 微指令的编码方式

- 5.5.5 微指令的格式

- 5.5.6 取指操作不同控制器流程

- 5.5.7 微程序控制器和硬布线控制器

- 5.6 指令流水线

- 5.6.1 流水线

- 5.6.2 影响流水线的因素

- 6 练手题

- 6.1

- 6.2

- 6.3

- 6.4

- 6.5

- 总结

第5章 中央处理器及指令

5.1 CPU的功能和基本结构

5.1.1 CPU功能

CPU由运算器和控制器组成。

运算器由ACC累加器,MQ乘商寄存器,X通用寄存器,ALU算术逻辑单元构成。

控制器由PC程序计数器,IR指令寄存器,CU控制单元构成

5.2 指令执行过程

CPU从主存中取出并执行一条指令所需的全部时间称为指令周期 ,也就是CPU完成一条指令的时间。

一个指令周期通常包含若干机器周期,一个机器周期又包含若干时钟周期。一个完整的指令周期应包括取指、间址、执行和中断四个机器周期。

中断周期中进栈操作是将SP减1,和传统意义上的进栈操作相反,因为计算机的堆栈中都是向低地址增加,所以进栈操作是减1,不是加1。

5.2.1 取指周期

是根据PC中的内容从主存中取出指令代码并存放在指令寄存器IR中,取指令的同时,PC加1。

数据流向:

1、PC->MAR->地址总线->主存。

2、CU发出控制信号->控制总线->主存。

3、主存->数据总线->MDR->IR(存放指令)。

4、CU发出读命令->PC+1

5.2.2 间址周期

在有些需要间接寻址的情况下,取操作数有效地址。

数据流向:

1、Ad(IR)->MAR->地址总线->主存。

2、CU发出读命令->控制总线->主存。

3、主存->数据总线->MDR(存放有效地址)。

5.2.3 执行周期

是根据IR中的指令字的操作码和操作数通过ALU操作产生执行结果。

5.2.4 中断周期

在有处理中断请求的时候,假设程序断点存入堆栈中,并用SP表示栈顶地址,而且进栈操作是先修改栈顶指针,后存入数据。

数据流向:

1、CU发送控制信号->SP-1->SP->MAR->地址总线->主存。

2、CU发送读命令->控制总线->主存。

3、PC->MDR->数据总线->主存(程序断点存入主存)。

4、CU发送读命令(中断服务程序的入口地址)->PC

5.3 指令执行方案

1、单指令周期 :对所有指令都选用相同的时间来完成,指令之间串行执行,指令周期取决于执行时间最长的指令的执行时间。

2、多指令周期 :指令之间串行执行,不再要求所有指令占用相同的执行时间。

3、流水线方案 :指令之间并行执行,尽量让多条指令同时执行,但各自处在不同的执行步骤中。

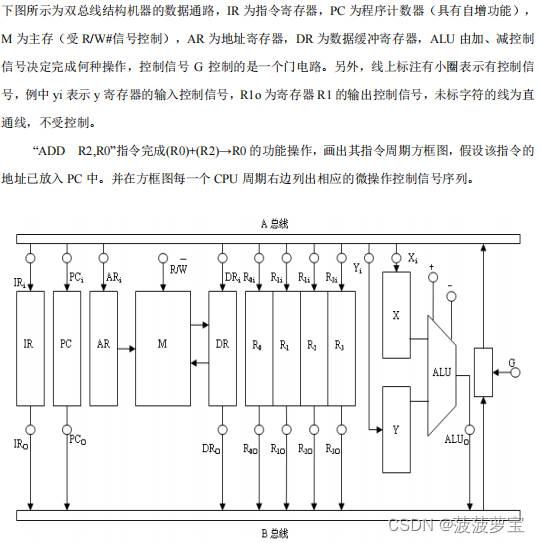

5.4 数据通路

数据在功能部件之间传送的路径称为 数据通路 ,其功能是 实现CPU内部的运算器和寄存器以及寄存器之间的数据交换 。

寄存器之间:PC->Bus->MAR

主存与CPU之间:

1、PC->Bus->MAR

2、CU发出读命令 1->R

3、MEM(MAR)->MDR

4、MDR->Bus->IR

执行算术或逻辑运算:(ALU必须在两个输入端同时有效的情况下才可以工作):

1、Ad(IR)->Bus->MAR

2、1->R

3、MEM(MAR)->数据线->MDR

4 、MDR->Bus->Y

5、(ACC)+(Y)->Z

6、Z->ACC

5.4.1 数据通路基本结构

1) CPU内部单总线方式:所有寄存器的输入端和输出端都连接到一条公共的通路上。结构简单,但数据传输中存在较多冲突现象,性能较低。

2)CPU内部三总线方式:所有寄存器的输入端和输出端都连接到多条公共的通路上。效率CPU内部单总线方式相对有所提高。

3)专用数据通路方式:根据指令执行过程中的数据和地址的流动方向安排连接线路,避免使用共享的总线。性能较高,但硬件量大。前两者为内部总线,第三个为专用数据总线

5.5 控制器

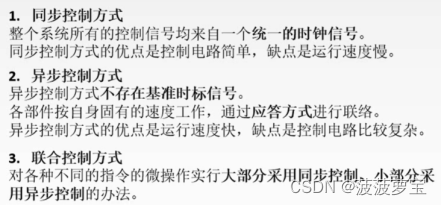

5.5.1 CPU控制方式和功能

CPU的控制方式

控制器的主要功能有:

1)从主存中取出一条指令,并指出下一条指令在主存中的位置。

2)对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作。

3)指挥并控制CPU、主存、输入和输出设备之间的数据流动方向。

5.5.2 硬布线控制器

硬布线控制器由复杂的组合逻辑门电路和一些触发器构成,因此又称为组合逻辑控制器。

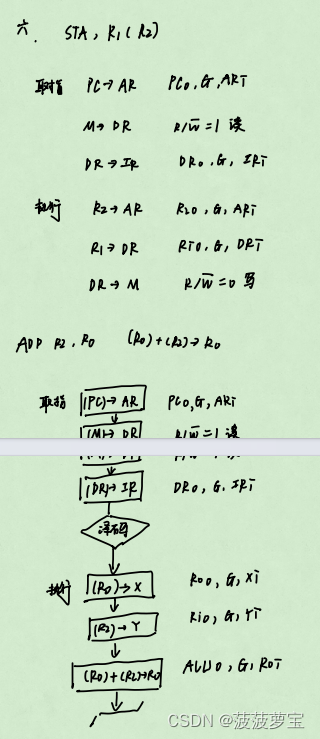

5.5.3 微程序控制器

微程序控制器采用存储逻辑实现 ,也就是把微操作信号代码化,使每条机器指令转化成为一段微程序并存入一个专门的存储器(控制存储器)中, 微操作控制信号由微指令产生。微指令是若干微命令的集合,存放微指令的控制存储器的单元地址称为微地址。若指令系统中具有n种机器指令,则控制存储器中的微程序数至少是n+1个(1为公共的取指微程序)。微命令(控制序列的最小单位),微操作(最小操作,微命令和微操作一一对应),微指令(若干微命令的集合),微周期(读取并执行微指令的时间),微程序(微指令的有序集合)

5.5.4 微指令的编码方式

微指令的编码方式又称为微指令的控制方式 ,指如何对微指令的控制字段进行编码,以形成控制信号。目标是在保证速度的情况下,尽量缩短微指令字长。

1)直接编码(直接控制)方式。

2)字段直接编码方式:将微指令的微命令字段分成若干个小字段,把互斥性微命令组合在同一字段中,把相容性微命令组合在不同的字段中。

3)字段间接编码方式,又称隐式编码。

5.5.5 微指令的格式

1)水平型微指令:指令字中的一位对应一个控制信号,有输出时为1,否则为0。一条水平型微指令定义并执行几种并行的基本操作。优点是微程序短,执行速度快;缺点是微指令长,编写微程序较麻烦。

2)垂直型微指令:类似机器指令操作码的方式,设置微操作码字段,由微操作码规定微指令的功能。一条垂直型微指令只能定义并执行一种基本操作。优点是微指令短、简单、规整,便于编写微程序;缺点是微程序长,执行速度慢,工作效率低。

3)混合型微指令

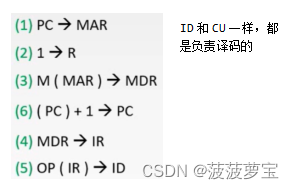

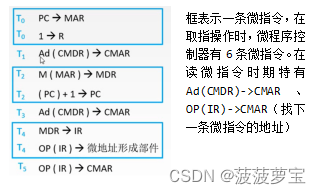

5.5.6 取指操作不同控制器流程

硬布线控制器:

微程序控制器:

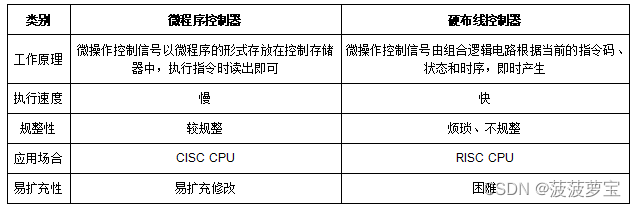

5.5.7 微程序控制器和硬布线控制器

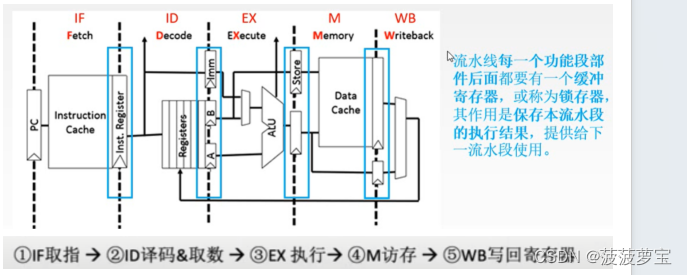

5.6 指令流水线

一条指令的执行过程:

1、取指 :根据PC内容访问主存储器,取出一条指令送到IR中。

2、分析 :对指令操作码进行译码,按照给定的寻址方式和地址字段中的内容形成操作数的有效地址EA,并从有效地址EA中取出操作数。

3、执行 :根据操作码字段,完成指令规定的功能,即把运算结果写到通用寄存器或主存中。

指令处理方式:

1、顺序执行方式:前一条指令执行完后,才启动下一条指令,T=3nt。

2、流水线执行方式:把取第k+1条指令提前到分析第k条指令的期间完成,而将分析第k+1条指令与执行第k条指令同时进行,T=(2+n)t

5.6.1 流水线

5.6.2 影响流水线的因素

1)结构相关(资源冲突):由于多条指令在同一时刻争用同一资源而形成的冲突

解决办法:

a. 前一指令访存时,使后一条相关指令(以及其后续指令)暂停一个时钟周期。

b. 单独设置数据存储器和指令存储器,使两项操作各自在不同的存储器中进行,这属于资源重复配置。

2)数据相关(数据冲突,数据冒险):必须等前一条指令执行完才能执行后一条指令的情况---->主要情况

a. 把遇到数据相关的指令及其后续指令都暂停一至几个时钟周期,可分为硬件阻塞(stall)和软件插入"NOP"指令两种方法。

b. 设置相关专用通路,即不等前一条指令把计算结果返回寄存器组,下一条指令也不再读寄存器组,而是直接把前一条指令的ALU的计算结果作为自己的输入数据开始计算过程,使本来需要暂停的操作可以继续执行,称为数据旁路技术。

c. 通过编译器对数据相关的指令编译优化的方法,调整指令顺序来解决数据相关。

3)控制相关(控制冲突,控制冒险):遇到转移指令和其他改变PC值得指令而造成断流

a. 对转移指令进行分支预测,分为简单(静态)预测和动态预测,静态预测总是预测条件不满足,即继续执行后续指令;动态预测根据程序执行的历史情况,进行动态预测调整。

b. 预取转移成功和不成功两个控制流方向上的目标指令。

c. 加快和提前形成条件码。

d. 提高转移方向的猜准率。

6 练手题

去年并没有相关的考点,但是大家学过计组,都知道这里算是非常重要的,我也不敢轻易断言今年不考,我就找几个期末试题里的大家练练手。

难度是不是一下就上来了,加油!

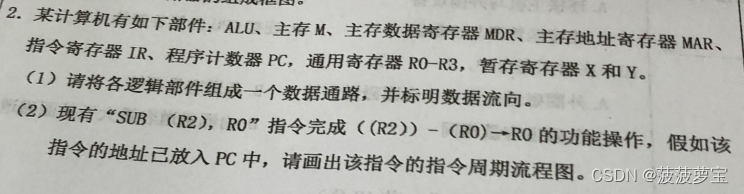

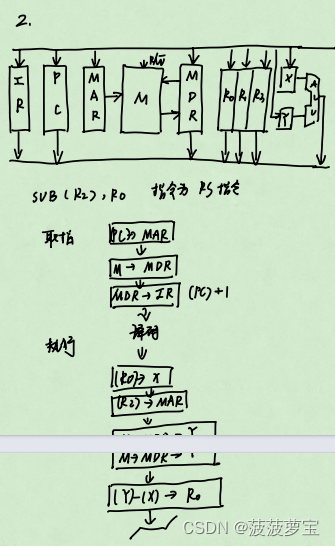

6.1

6.2

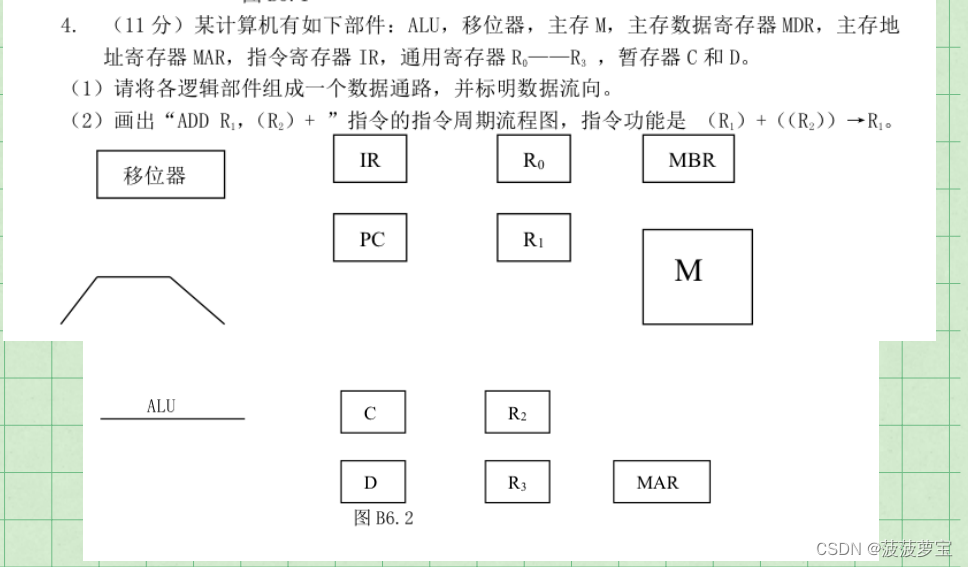

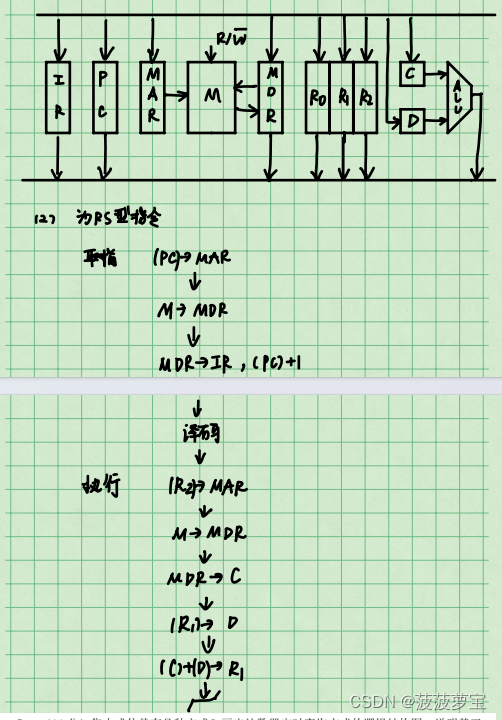

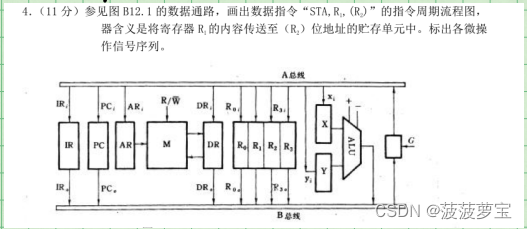

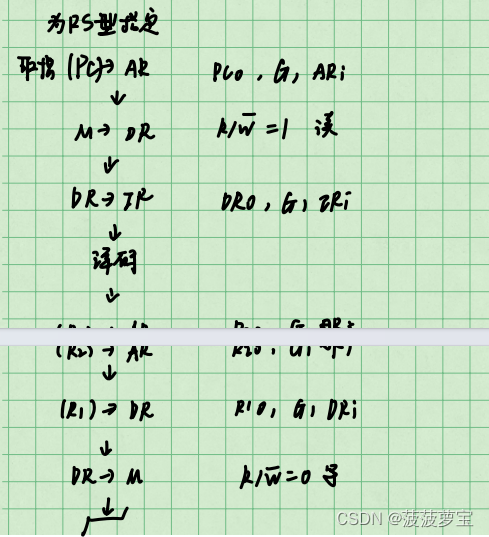

6.3

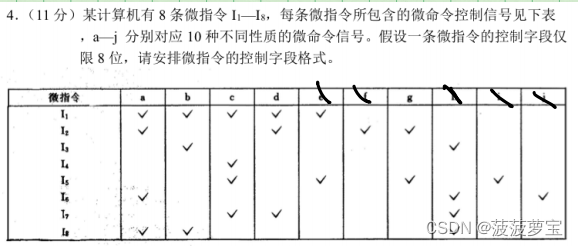

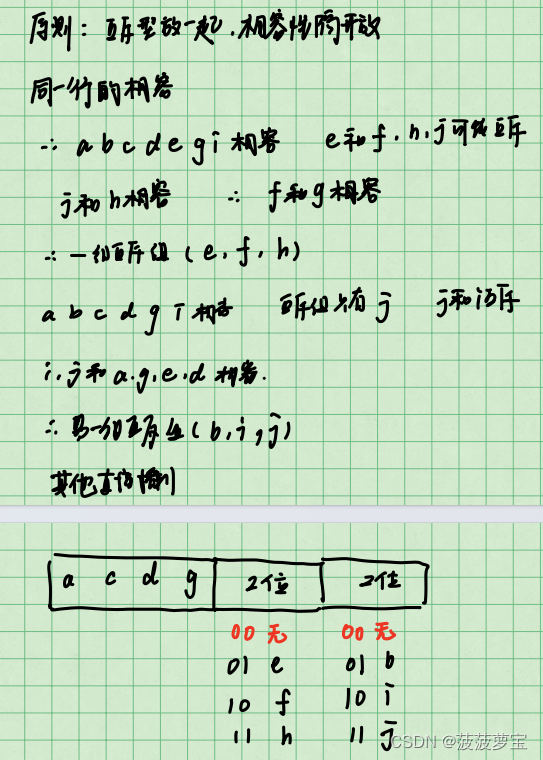

6.4

微指令也来上几道练练手感

6.5

总结

相信这一章干货也是满满,有问题打在评论区哦

这篇关于计算机组成原理-第五章 中央处理器【期末复习|考研复习】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!