本文主要是介绍《低功耗方法学》翻译——第十三章:保留寄存器设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

第十三章:保留寄存器设计

对于那些需要在唤醒后快速恢复工作的设计,必须在进入休眠模式之前保存设计的当前状态,并在唤醒时恢复该状态。在本章中,我们描述了片上保留方法,包括保留寄存器和内存保留技术。

13.1保留寄存器

有许多不同的保持寄存器设计。我们在这里讨论的是标准扫描可测试D型触发器的所有变体。我们描述三种保持寄存器:

- 单引脚 Live Slave - 使用单个保存/恢复控制引脚,对触发器本身进行最小的改变。

- 单引脚 Balloon - 使用单个保存/恢复控制引脚,但增加了第二个从锁存以进行保留。

- 双引脚 Balloon - 使用单独的保存和恢复控制引脚和第二个从锁存来保持。

13.1.1 单引脚“Live Slave”保留寄存器

最简单形式的保持寄存器是其中底层主从锁存器结构适于提供低泄漏模式以维持从锁存器的状态。

图13-1显示了上升沿时钟扫描寄存器设计的概念示意图。

寄存器的前端是一个多路复用器。当扫描使能控制“SE”被取消断言时,它选择功能数据“D”输入;当SE被断言时,它选择扫描链串行输入“SI”。为了提供最佳建立时序行为,该多路复用器和大部分数据路径使用低V晶体管--如图中逻辑门上的粗条所示。

当内部时钟“CK”为低而反相的“CKN”为高时,“主”锁存器对输入值进行采样。主锁存器使用低VT晶体管来改善建立和保持特性。

从锁存器在内部时钟的交替相位上对主锁存器的输出进行采样,然后是反相缓冲级。最后一个反相器用不同的晶体管尺寸来实现,以提供库中不同驱动强度版本的寄存器。

通过引入以下特征来增加保留功能:

- 在时钟电路中插入与门,以允许保持信号(NRE-TAIN)在电源门控期间强制时钟关闭。

- 从锁存器由始always-on电源供电,而寄存器的其余部分由虚拟导轨供电,并且可以关断电源。

- 高VT晶体管用于从锁存器、时钟缓冲器以及将主锁存器连接到从锁存器的反相器中。

必须仔细控制低电平有效的“NRETAIN”控制信号,使其仅在时钟处于非有效状态(在这种情况下为低)时才会改变。此外,它还必须由always-on的缓冲器网络驱动。

在系统使用中,时钟被停止:然后NRETAIN信号被断言为低;最后电源被关闭。当电源被关闭时,NRETAIN被保持为低电平。

在重新施加门控电源之后,在时钟重新启动之前,NRETAIN信号随后被解除断言(高)。

当NRETAIN被断言时,三态反相器(标记为T1)关断,从而将从锁存器与主锁存器隔离。

对于具有异步置位或复位的寄存器,保留控制还需要将寄存器与也可能破坏从属锁存信号的电源门控置位或复位网络隔离。

“Live Slave”保留寄存器设计的优点包括:

- 对底层主从锁存器设计的面积影响最小。

- 一个单一的信号就能控制保留功能。

“Live Slave”保留寄存器设计的缺点包括:

- 对寄存器性能的影响。在高VT模式下实现从锁存以最小化保持模式下的泄漏。然而,这影响了CLK到Q的时序路径,并且必须牺牲最佳泄漏的晶体管大小来平衡性能上的折衷。

- 时钟的高VT门控增加了输入数据的保持时间要求。即使这样,我们也不能使用最小的漏电晶体管尺寸,因为内部低VT时钟节点的数量必须以良好的平衡上升和下降时间来驱动。

- 只有当时钟在恢复状态之前被强制为低时才是合适的--时钟门控电路中的任何“未知”都需要显式覆盖。

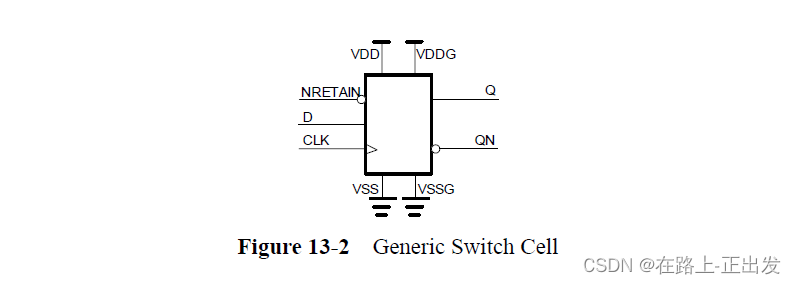

作为一个库组件,这样的寄存器看起来就像一个组件,带有始终上电和电源选通的电源导轨,以及额外的保持控制信号。可与header或footer开关电源门控一起使用的通用组件如图13-2所示:

“全局电源”VDDG/VSSG提供高VT内部时钟门和缓冲以及从锁存器。其余寄存器电路通过VDD/VSS轨道进行电源选通。

功能控制波形如图13-3所示。必须停止时钟,并使用逻辑0值使其处于非活动状态。在关闭门控电源之前,必须断言RETAIN信号(本例中为NRETAIN 拉低)。RETAIN信号必须在电源恢复后才能解除断言,而后时钟才能重新启动。电源选通信号(PG_ENABLE)关闭门控电源,包括时钟树缓冲,如时钟波形所示。

13.1.2 双控制信号”Balloon“保留寄存器

保持底层寄存器速度和时钟端到输出端性能的另一种保持设计是balloon保持寄存器。它在标准D型触发器上增加了一个弱的高VT锁存器。第三个锁存器(有时称为影子锁存器或“balloon”锁存器)连接到一个始终开启的电源,在漏电的主从寄存器锁存器断电时保持寄存器状态。

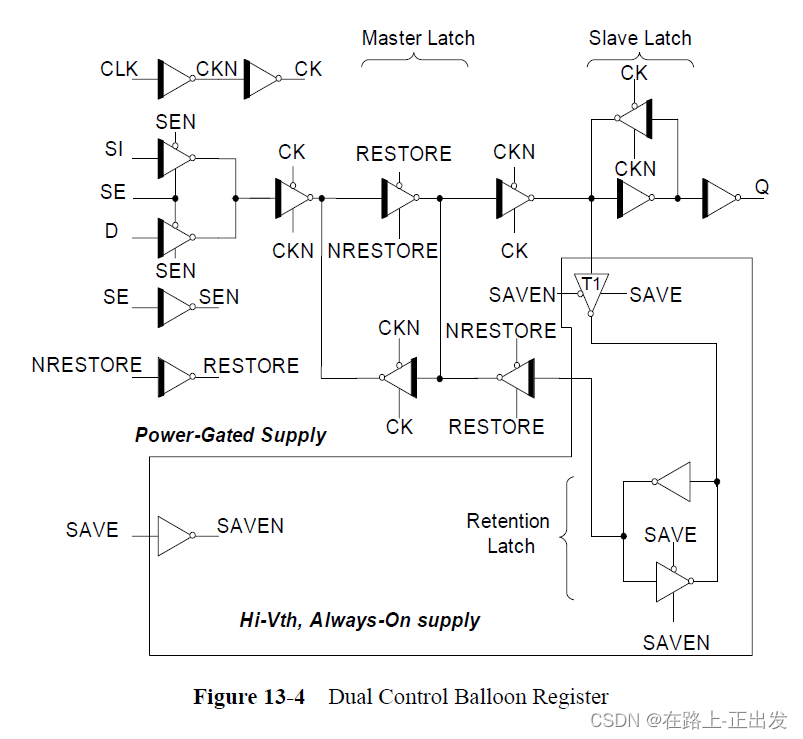

如图13-4所示,基本寄存器设计是在低VT晶体管中实现的。在always-on电源电压区域增加了一个低泄漏、高VT保持锁存器。

寄存器中增加了两个控制信号。一个始终上电信号“SAVE”被用来控制对进入保持锁存器的数据的采样。当SAVE被断言时,从锁存器的状态被复制到保持锁存器中。然后,每当SAVE信号被解除断言时,该数据就被保持。在系统使用中,在电源门控之前,时钟应该停止并且SAVE信号发出脉冲控制信号,以保持寄存器的状态。

作为低电平有效的恢复信号,NRESTORE提供控制以强制寄存器的状态为保留锁存值的状态。在系统使用中,在脉冲(低)NRESTORE信号以将寄存器的状态设置回保留值之前,必须恢复门控功率并安全地稳定。

图中显示了寄存器恢复路径的一个相当复杂的示例设计。这种设计允许保留寄存器恢复保留值,而不管时钟的状态如何。如果时钟为低并且主锁存器打开并且对输入数据进行采样,则保留的值被强制进入从锁存器。为了防止恢复时的争用,如果时钟为高,则保持锁存器值被强制进入主锁存器,然后在时钟变低时传播到从锁存器。

这种保存/恢复控制风格的保留寄存器设计的优点。

- 最小漏电功率。保持锁存和控制信号可以是最小的晶体管尺寸。

- 与“Live-Slave”设计相比,对性能的影响最小,尽管在添加了保存/恢复控制晶体管的主锁存器的输出和从锁存器的输入上有一些微小的内部负载。

- 可以构建为独立于恢复时的时钟相位,这在具有复杂时钟门控的设计中可能很有价值。

这种保存/恢复控制型保留寄存器设计的缺点。

- 增加第三个锁存器,即使只添加了一个小晶体管结构,也会对底层主从锁存器设计产生面积影响。

- 使用两个控制信号(SAVE和NRESTORE)需要两个缓冲网络,其中只有一个(NRESTORE)可以进行电源选通--这增加了一些面积影响。

- 双控制信令增加了系统设计的复杂性和一些缓冲树区域。

图13-5显示了这种保持寄存器的库组件图,该寄存器带有两个独立的、异步的脉冲式信号来控制保存和恢复功能。“全局功率”VDDG/VSSG提供高VT保存控制缓冲器和保持锁存器。其余寄存器电路由(切换的)VDD/VSS轨道供电。

功能控制波形如图13-6所示。时钟可以在任一阶段停止。在关闭门控电源之前,状态保存信号必须脉冲激活(在这种情况下为save高)。状态恢复信号必须仅在电源恢复后脉冲激活,然后可以重新启动时钟。功率门控可以关闭时钟树缓冲和恢复控制缓冲网络,如波形中的未知逻辑电平所示。

保留、异步复位和预设的优先级。

为了最大限度地减少泄漏,我们希望关闭高扇出复位的电源,并将网络设置为系统电源门控的一部分。一旦关机,这些网络可以浮动,因此在电源门控进入和退出期间,保留触发器上的这些端口可能会浮动到非逻辑电平。

通过确保balloon锁存器仅由状态保存控制网络控制,任何异步设置和重置仅在主/从锁存器上操作。然后,系统级时序要求仅在重置和预置已被加电并置于适当状态之后才断言恢复控制。

13.1.3 单控制信号“Balloon”保留寄存器

对上述保留寄存器的保存/恢复类型的增强是将单个控制信号用于保存和恢复两者,即,状态被保存在控制信号的一个边沿,而在另一个边沿被恢复。

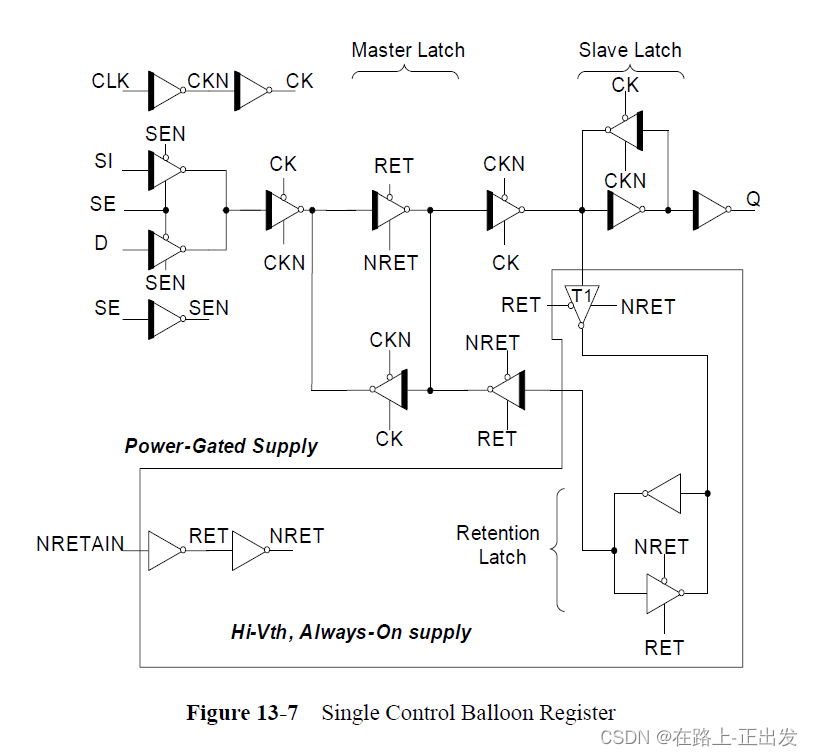

图13-7显示了balloon式保留寄存器的概念示意图,该寄存器具有单状态保留控制-在本例中为有效-低NRETAIN信号。

NRETAIN信号必须由始终上电的控制网络驱动,并在高VT中实现,以最大限度地减少电源门控期间的泄漏。结构非常类似于上述双控制信号寄存器类型,但在这种情况下,每当NRETAIN信号被解除断言为高时,保留锁存器就对从属数据进行采样,而每当NRETAIN信号被断言为低时,保持锁存器就保持该状态。

这种设计具有略高的动态功率,因为每当从锁存器改变状态时,保持锁存器的额外电容节点必须被驱动。由于保持锁存器被设计为使用小的弱晶体管来最小化泄漏功率,所以这只是主从式寄存器动态功率的一小部分。然而,这种设计不需要两个控制网络。

与前面的双控制寄存器类似,图中显示了一个相当复杂的寄存器恢复路径设计示例,允许该保留寄存器恢复保留值,而不考虑时钟的状态。如果时钟为低电平且主锁存器打开并且采样输入数据,则将保留值强制进入从属锁存器。如果时钟为高电平,则保留锁存值被强制进入主锁存器,然后当时钟变低时,主锁存器传播到从属锁存器。

这种保存/恢复控制类型的保持寄存器设计的优点包括:

- 最小的漏电功率。保持锁存和控制信号可以是最小的晶体管尺寸。

- 与“Live-Slave”设计相比,对性能的影响最小,尽管在添加了保存/恢复控制晶体管的主锁存器的输出和从锁存器的输入上有一些微小的内部负载。

- 可以构建为独立于恢复时的时钟相位,这在具有复杂时钟门控的设计中可能很有价值。

- 单控制网络相较于双控制方式的保留寄存器。这节省了系统级的动态功耗,因为只需要一组而不是两组缓冲区来分配保留控制。

这种保存/恢复控制型保留寄存器设计的缺点。

- 与“Live-Slave”设计相比,由于增加了第三个锁存器,虽然只增加了微弱的小晶体管结构,但面积影响很大。

- 与双控制气球设计相比,动态功率略高,因为每次从锁存值改变时,保留锁存器都会转换。

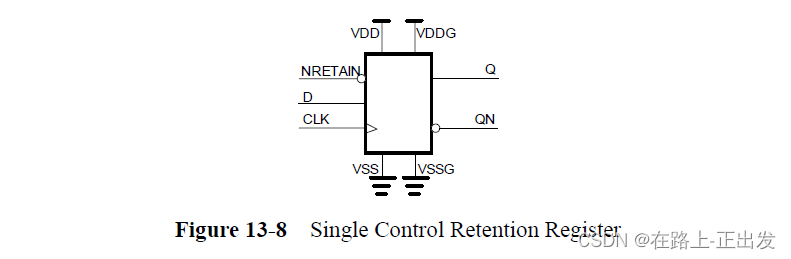

图13-8显示了带有单个异步保持控制信号的库组件视图,该信号用于提供状态保存和恢复功能。“全局电源”VDDG/VSSG提供高VT缓冲器和保持锁存,其余更高性能的寄存器电路可以从VDD/VSS导轨进行电源门控。

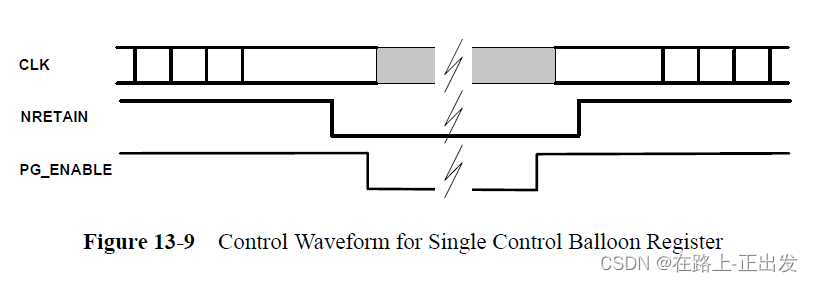

功能控制波形如图13-9所示。时钟可以在任一阶段停止。在门控电源关闭之前,必须断言保持信号(在这种情况下为低电平),并且只有在电源安全恢复后,时钟才可以重新启动。电源门控可能会关闭时钟树缓冲区的电源,如波形中的未知逻辑电平所示。

13.1.4 保留寄存器:相关布局

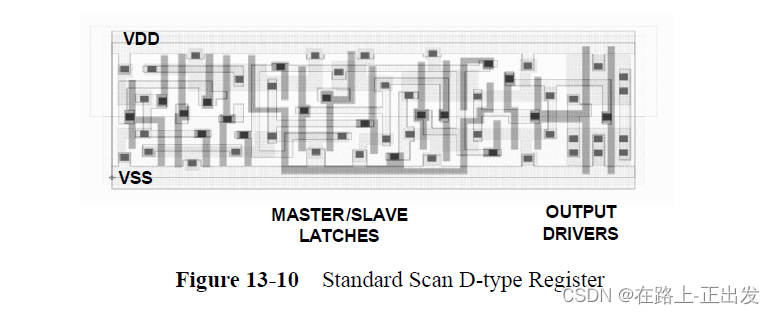

图13-10显示了一个标准的可扫描测试的D型寄存器的例子。该寄存器的“Live-Slave”版本会稍大一些,以包括时钟门控和高VT内部时钟相位缓冲以及高VT植入区。

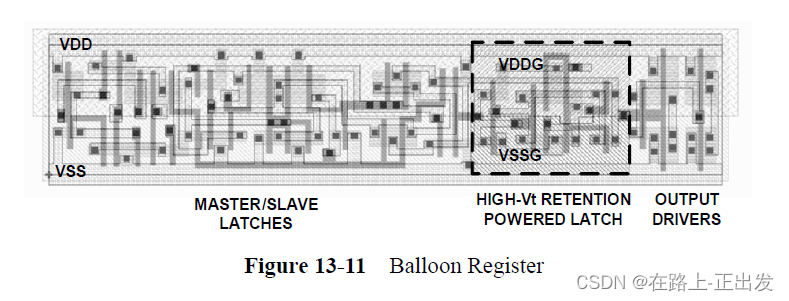

图13-11显示了一个“balloon”保持式可扫描测试的D型寄存器的例子。用于保持锁存和控制缓冲的高VT植入区清晰可见,作为单元实现的额外区域。对于驱动强度更高的调节器版本,保持区在总寄存器单元面积中的比例变得更小。

如图所示,为低驱动强度的基本寄存器增加保持的面积开销约为30-40%。

13.2 存储器保留方法

在功率门控设计中,FIFO通常在进入休眠之前被刷新,而高速缓存在唤醒之后被初始化,在这些情况下,我们可以关闭存储器以节省静态功耗,并容忍存储器数据的丢失。

然而,对于要求唤醒延迟最小的高性能设计,片上存储器的内容需要在电源门控期间被保留,各种存储器保留方法已经被开发出来,这些方法的原理是在不破坏SRAM中的数据的情况下尽可能地减少电源门控期间的泄漏。

在SRAM单元中引入如上所述的保持电路是不现实的。任何这样的电路都将导致不可接受的面积增加。VDD保持和源极偏置保持方法是在功率门控设计中经常使用的方法之一。

13.2.1 VDD保留法

在该方法中,向存储器提供单独的VDD电源;在正常工作时,VDD被提供在正常的电源电压下;在睡眠模式下,VDD被降低到0.5-0.6V,以在保持存储器内容的同时降低存储器功耗。该方法实现简单,不需要改变存储器电路,但需要为存储器提供专用、可切换的电源。

13.2.2 源极-二极管偏置方法

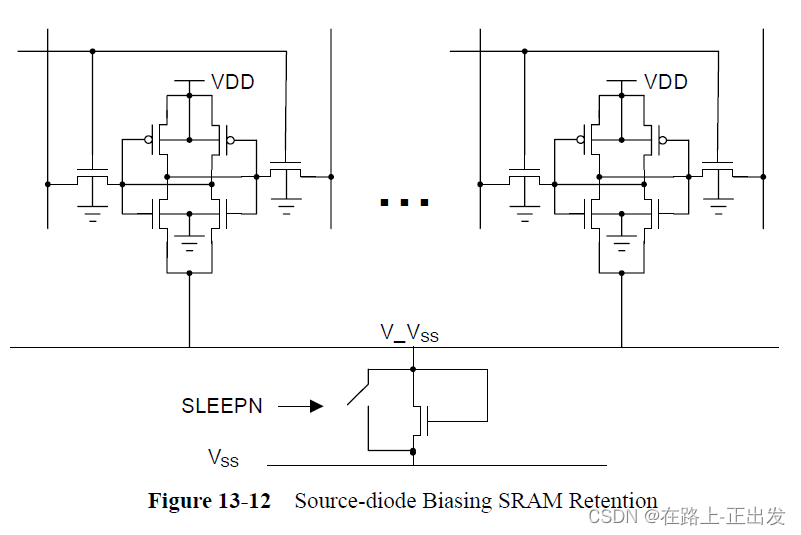

源极偏置SRAM保持法的原理是在降低SRAM操作电压后施加反向体偏压以进一步减少漏电。源极-二极管偏置方法是源极偏置方法最简单的实现。在这种方法中,二极管被插入到SRAM单元阵列的源极电源中,并由开关控制,如图13-12所示。

在正常工作时,控制信号SLEEPN被解除断言,从而使开关闭合,绕过二极管。在这种情况下,V_VSS=VSS。

在休眠模式下,SLEEPN被断言,从而打开开关。SRAM单元阵列的电源现在通过二极管。二极管的内置阈值(VT)将V_VSS的电压提高到VSS(地)以上。与VDD保持方法一样,VR降低了SRAM操作电压,从而减少了泄漏。

注意,SRAM阵列中的NMOS晶体管的衬底连接到地(Vss),Vss现在低于V_VSS下的源极偏置。因此,V_Vss中的电压上升也对NMOS晶体管单元施加逆向偏置。逆向偏置进一步降低睡眠模式下SRAM阵列单元中的亚阈值泄漏电流。

同样的原理也适用于SRAM阵列单元中的PMOS晶体管,其中二极管可以被插入到VDD电源中。但是,这不适用于VDD被缩放到低于1.2V的90 nm以下的SRAM设计,因为2x VT(在两个二极管上)电压降低导致SRAM操作电压太低而不能保持数据。

因此,PMOS或NMOS偏置都可以用于90 nm以下的设计。由于SRAM单元中的PMOS晶体管比NMOS的漏电更小,因此在这些设计中通常使用NMOS源极偏置。

偏置控制开关通常由高VT的NMOS睡眠开关实现,二极管由栅极和漏极连接的NMOS晶体管构成。

源极-二极管偏置方法的优点是实现简单,不需要偏置电源。

然而,要在保留数据的同时获得最大限度地减少泄漏的最佳逆向偏置是困难的,逆向偏置由二极管的VT决定,因此对于给定的工艺是固定的。

13.2.3 源极偏置法

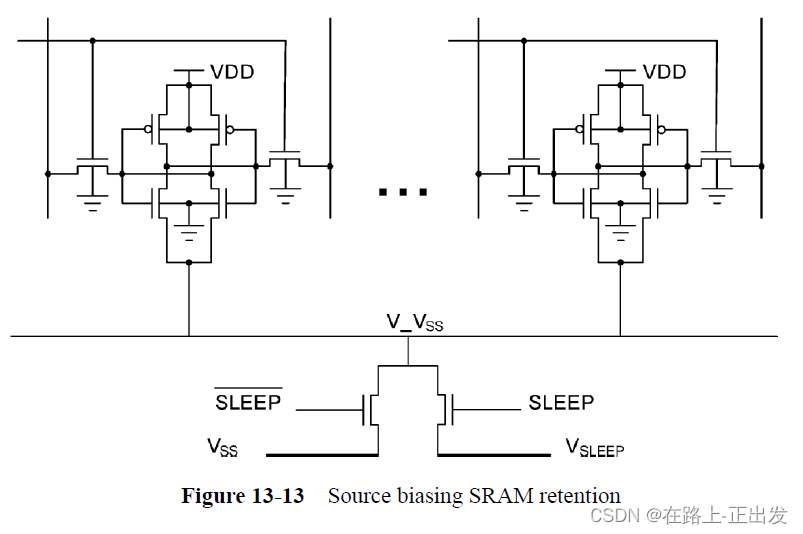

SRAM单元中的噪声容限随着VDD比例的增大而缩小。这要求在低于1V的设计中具有最佳的SRAM工作电压和源极偏置。一种解决方案是为SRAM单元提供专用的源极偏置电源来取代二极管。图13-13所示。

这种方法的缺点是需要单独的偏置电源。由于SRAM在保持模式下只消耗漏电流,并且偏置在电源范围内,因此可以通过简单的设计(例如分压器)来产生片上偏置电源。

13.2.4 减少保留延迟的方法

对于那些存储器不经常被访问但访问延迟需要较短的应用,可以将上面讨论的存储器保留方法与保留延迟减少技术相结合。

基于块的保留和唤醒

在该方法中,将存储器划分为若干个小块或块,每个块可以单独控制为保持模式或功能模式,所有存储块通常处于低泄漏保持模式,当请求存储器读或写操作时,地址译码选择访问块,然后将其从保持模式切换到功能模式,准备进行数据访问。

在数据访问之后,块立即返回到保持模式以进行省电。保持延迟,即将块唤醒到完全功能状态所需的时间,通过减小块的虚拟VSS网络的大小来缩短。块越小,块的虚拟VSS越快放电,从而唤醒延迟越短。然而,如果块变得太小,那么列感应放大器中的面积和功率开销可能会盖过保持中的漏电节省的好处。

我们建议根据设计特定的存储器、访问频率和保留延迟要求来探索各种内存分块策略。

基于行的保留和唤醒

基于行的保留方法解决了基于块的保留方法中显著的列感应放大开销的问题,在基于行的方法中,存储块的大小是由存储功耗和访问时间的综合考虑来决定的,这通常会产生中等大小的存储块。

与基于块的保留方法不同,基于行的方法中的V_VSS网是按行分布的,每一行都由其V_VSS网以保留或功能模式单独控制。利用存储器地址先于数据放在总线上的存储器访问控制序列的优点,该方法使用SRAM字地址来仅激活当前存储器访问所需的行。其他行中的其余SRAM阵列单元保持保持模式。基于行的保持方法降低了延迟,因为行的小尺寸允许快速供电和掉电。因此,我们不需要将存储器分割成许多任意的小块,这将在列电路中引起显著的面积和功率损失。

为了降低控制电路的复杂性和开销,可以将基于行的保持和唤醒控制扩展为基于行组的方法,其中在保持和唤醒期间控制一组行,而不是单行。

这篇关于《低功耗方法学》翻译——第十三章:保留寄存器设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!