本文主要是介绍芯片设计(一):CRG(ResetClock中的ICG),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

原文链接:

1、https://zhuanlan.zhihu.com/p/378708372

2、https://zhuanlan.zhihu.com/p/379372643

感谢前辈的优秀文章,学习学习!!!

这篇文章讲讲芯片里非常重要的两个小东西:时钟和复位。

虽然小,但是非常容易出错, 时钟在数字电路里类似于芯片的供血系统。你可以理解为供血系统出点BUG,芯片就非常容易处于一种自求多福的状态。。。

1-Reset

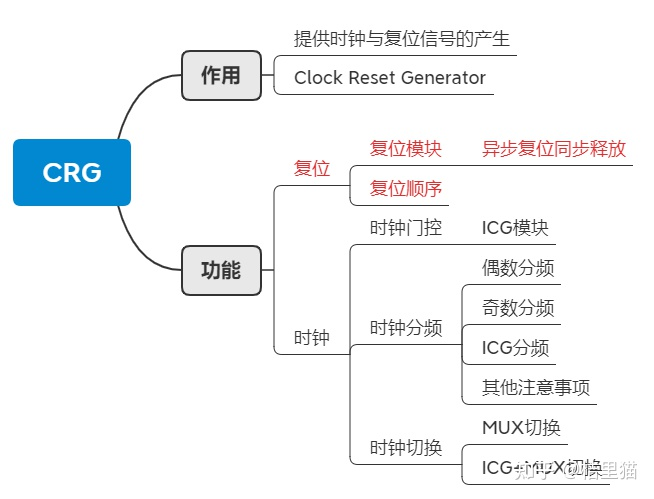

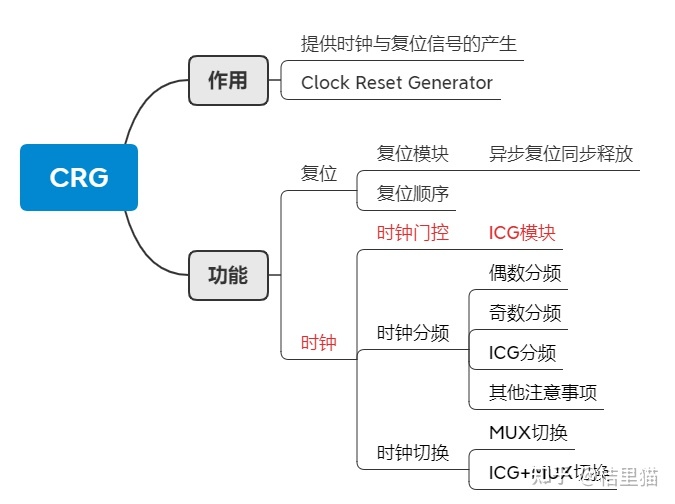

时钟与复位统称CRG,Clock and Reset Generator。

CRG中主要包含这些东西。

我们先讲复位,需要说明的是此处主要讲异步复位,软复位完全是同步的,其实和其他信号没有区别。

1. 复位方式:异步复位,同步释放

为什么需要异步复位,同步释放?

原因主要是:

- 如果同步复位,同步释放,需要对复位信号进行同步,对于外部复位来讲容易形成锁死的问题。这是个鸡生蛋蛋生鸡的问题。复位信号用寄存器同步,然后用同步后的信号复位寄存器,我复位我自己?所以同步复位同步释放多用于软复位。

- 如果异步复位,异步释放,异步的释放操作非常容易导致亚稳态。相当于没有复位。

- 如果同步复位,异步释放,emmm 感觉上一般没有人这么折腾自己。

所以就剩下了一种办法,异步复位,同步释放。这个较为简单和典型。记住即可。硬复位信号都应该这么产生。

2. 异步复位的实现

敲黑板,面试会考的。这个不会基本上容易翻车。

always @ (posedge clk, negedge rst_async_n)

if (!rst_async_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

assign rst_sync_n = rst_s2;

endmodule

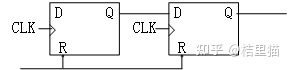

比较简洁。主要原理是用两个寄存器实现的。

3. 异步复位同步释放的波形显示

这个简单的电路就是这么一个原理~

4. 子模块的复位顺序

复位顺序需要具体问题具体对待,但总体的原则是

先复位外设,再复位核心。因为核心复位后有可能访问外设。

可以看看这篇,有个案例。桔里猫:RISCV AI SOC实战(四,复位管理)

https://zhuanlan.zhihu.com/p/161891614

5. 总结

复位大致上就这些东西。主要就是明白这个典型的电路以及复位顺序,后续讲时钟。

2-Clock中的ICG

1绪论

本篇文章讲CRG的第二部分, 时钟

时钟在数字电路中占据至关重要的地位。是整个数字芯片的节拍器。

2 ICG模块概述与原理

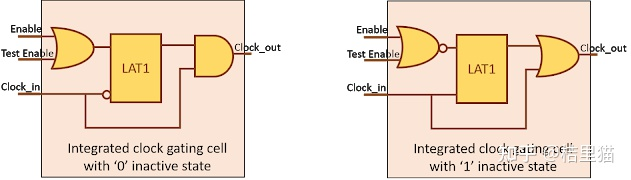

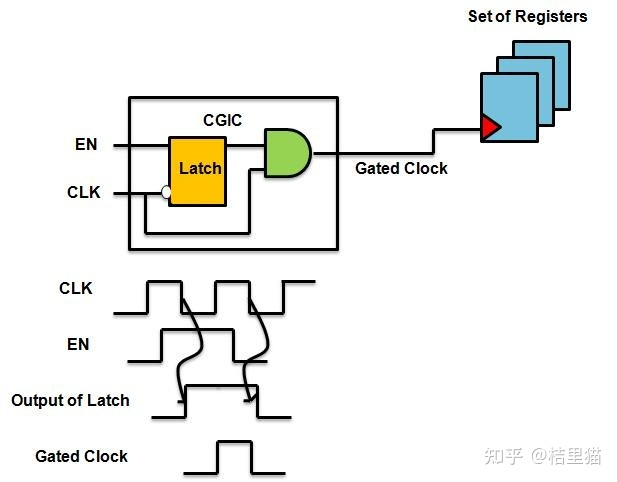

ICG模块的缩写是integrated Clock Gating的意思, 有些地方把这个东西叫isolate clock gating,应该是不对的。在较为先进的工艺库中一般会直接提供这个模块,不需要自己手动的搭建。但是需要知道其原理。(注:图不想自己画了,所以来自网络)

ICG模块一共有着两种形式,或形式或者与形式。其内部逻辑是用一个寄存器和两个与门组成的。

我们拿与门作为例子来讲。对于与门的ICG**,只有clk为低电平也时EN信号才会通过ICG**。保证了输出的第一个波形是上升沿。对于或类型的整好相反。可以类似分析。

ICG在数字电路中有三个用途

- 用于关断时钟,降低功耗

- 用于动态切换时钟时防止产生毛刺

- 用于时钟分频,后续讲

3.先回答三个问题

【类型如何选:使用Or还是And ICG,可以自己手动搭建ICG么】

这个比较简单,如果电路是上升沿触发的那么选and ICG,否则选Or ICG。原因是AND ICG第一个好的时钟是时钟上升沿。Or ICG相反。

工艺库都提供,不建议手动搭建。主要原因是分立的搭建需要专门检查STA, 而ICG在库中写好了时序约束,避免很多错误。

【En信号有什么要求】

En不可以异步,En信号一定要同步。否则如果EN和时钟沿离得太近容易亚稳态。

En一定不能是门控后的信号产生的,否则就死循环了。

【ICG是手动加的还是自动加的】

模块级的ICG手动加,寄存器级别的ICG综合工具自动加。后续会讲自动时钟门控。

4.自动门控时钟

ICG模块有时是根据设计手动加入到电路里的,但对于寄存器级别的控制,其实综合工具可以直接帮忙加入。

如下图所示,只要代码风格写的好,综合工具就能自动帮你门控。

如果不看低功耗的综合,综合出的电路是这样的

如果开了低功耗的综合,综合出来就是这样的

那么实际情况下怎么插入的?这个需要看综合策略。如果Q就1两个bit,那其实使用mux更省一些。如果Q比较宽,例如Q为32bit的话插入ICG就收益非常明显。

既节省了功耗,1个ICG肯定是小于32个mux。

总结

本章主要讲了ICG模块。在时钟控制里非常重要。后续讲时钟分频和切换。

这篇关于芯片设计(一):CRG(ResetClock中的ICG)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!