本文主要是介绍STM32CbueMX之NVIC中断,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

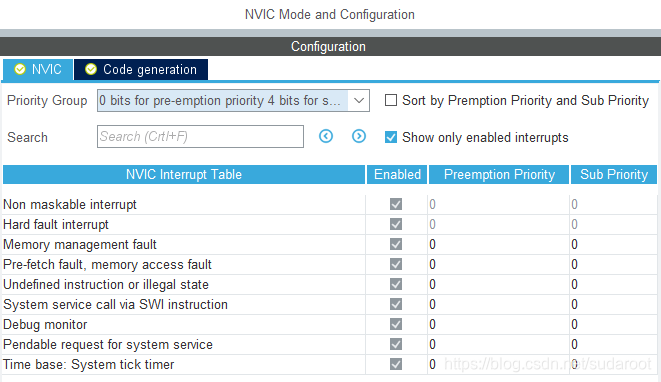

NVIC中断分组,内核中断,抢占中断,响应中断

上图内容来源《STM32F3 and STM32F4 Series Cortex®-M4 programming manual》的4.4.5 Application interrupt and reset control register (AIRCR) . . . . . . . . . . . 212

从上图可以知道中断分组是由寄存器AIRCR的Bits 10:8 PRIGROUP控制。至于PRI_N就是各个中断根据分组的单独的组优先级和响应级字段。

中断分组可以分成5组

第0组: 0 bits for pre-emption priority 4 bits for subpriority 0个抢占中断 16个响应中断

第1组: 1 bits for pre-emption priority 3 bits for subpriority 2个抢占中断 8个响应中断

第2组: 2 bits for pre-emption priority 2 bits for subpriority 4个抢占中断 4个响应中断

第3组: 3 bits for pre-emption priority 1 bits for subpriority 8个抢占中断 2个响应中断

第4组: 4 bits for pre-emption priority 0 bits for subpriority 16个抢占中断 0个响应中断

内核中断:什么是内核中断?灰色√的就是了。一共10个内核中断,其实有些是保留的内核中断。

启动文件也有写出来

《STM32F中文参考手册》向量表

抢占中断和响应中断:(数字越小,级别越高。最高级别是0,最低级别是15)

抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

抢占的意思是 在别的中断在执行的时候,能打断别人的中断执行,然后执行自己的中断。

1、高级别抢占中断可以 抢占低级别抢占中断级和任何级别响应中断。

2、抢占优先级相同的中断,高响应优先级不可以打断低响应优先级的中断。(摘录某原子)

3、抢占优先级相同的中断,当两个中断同时发生的情况下,哪个响应优先级高,哪个先执行。(摘录某原子)

4、两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行。(摘录某原子)

一般用STM32CubeMX软件生成的代码,设置NVIC中断组的函数HAL_NVIC_SetPriorityGrouping();

代码生成后,在HAL_StatusTypeDef HAL_Init(void)函数设置HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4)。

全篇完。

本人是一个嵌入式未入门小白,博客仅仅代表我个人主观见解,记录成长笔记。

笔记是以最简单的方式,只展示最核心的原理。

若有与 大神大大 见解有歧义,我绝对坚信 大神大大 见解是对的,我的是错的。

若无积分等无法下载源码,可加入QQ群657407920下载交流经验。感谢~!

这篇关于STM32CbueMX之NVIC中断的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!