本文主要是介绍STM32L4学习,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

STM32L4系列是围绕Cortex-M4构建,具有FPU和DSP指令集,主频高达80MHz。

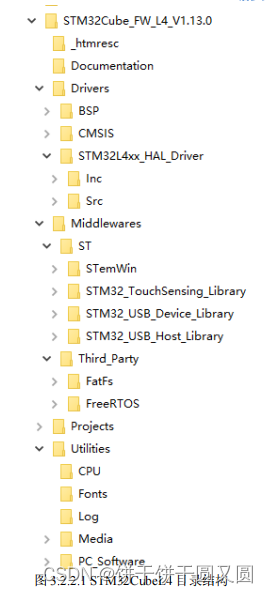

STM32CubeL4简介

STM32Cube 是 ST 提供的一套性能强大的免费开发工具和嵌入式软件模块,能够让开发人员在 STM32 平台上快速、轻松地开发应用。它包含两个关键部分:

- 图形配置工具STM32CubeMX。允许用户通过图形化向导来生成C语言工程。

- 嵌入式软件包(STM32Cube库)。包含完整的HAL库(STM32硬件抽象层API),配套的中间件,以及一系列完整的例程。

库开发与寄存器开发的关系

很多用户都是从学 51 单片机开发转而想进一步学习 STM32 开发,他们习惯了 51 单片机的寄存器开发方式,突然一个 STM32 固件库摆在面前会一头雾水,不知道从何下手。

固件库就是函数的几何,固件库函数的作用是向下负责与寄存器直接打交道,向上提供用户函数调用的接口(API)。

在51的开发中我们常常的做法是直接操作寄存器,比如要控制某些IO口的状态,我们直接操作寄存器:

P0=0x11;

而在STM32的开发中,我们同样可以操作寄存器:

GPIOC->BSRR=0x00000001;

这是针对STM32L4系列

这种方法当然可以,但是这种方法的劣势是要去掌握每个寄存器的用法,才能正确STM32,而对于STM32这种级别的MCU,数百个寄存器记下来又是谈何容易。

于是ST(意法半导体)推出了官方固件库,固件库将这些寄存器底层操作都封装起来,提供一套接口(API)供开发者调用,大多数场合下,不需要去直到操作的是哪个寄存器,只需要知道调用哪些函数即可。

STM32CubeL4固件包介绍

Drivers文件夹

Drivers文件夹包含BSP,CMSIS和STM32L4xx_HAL_Driver三个子文件夹。

- BSP:板级支持包,此支持包提供的是直接与硬件打交道的API,例如触摸屏,LCD,SRAM以及SSPROM等板载硬件资源等驱动。BSP文件夹下有多种ST官方Discovery开发板,Nucleo开发板以及EVAL板的硬件驱动API文件,每一种开发板对应一个文件夹。

- CMSIS:顾名思义就是符合CMSIS标准的软件抽象层组件相关文件。文件夹内部文件比较多。主要包括DSP(DSP_LIB文件夹),Cortex-M内核及其设备文件(include文件夹),微控制器专用头文件/启动代码/专用系统文件等(Device 文件夹)。

- STM32L4xx_HAL_Driver:这个文件夹非常重要,包含了所有的STM32L4xx系列HAL库头文件和源文件,也就是底层硬件抽象层API声明和定义。它的作用是屏蔽了复杂的硬件寄存器操作,统一了外设的接口函数。

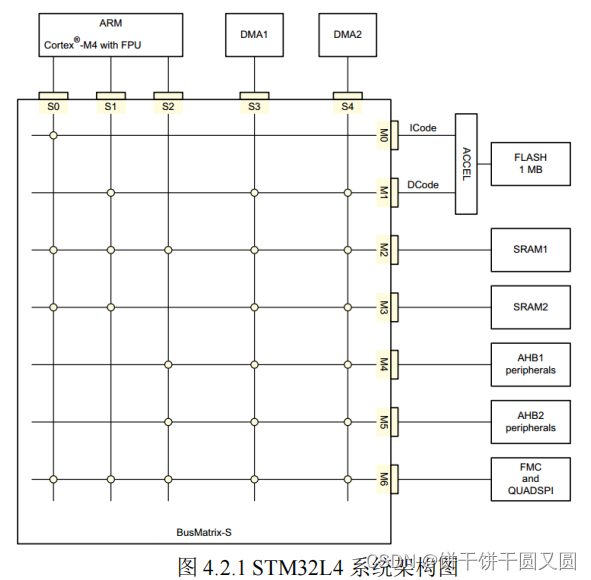

STM32L4总线架构

STM32L4的总线架构比51单片机就要强大很多了。

主系统由32位多层AHB总线矩阵构成,总线矩阵可实现以下部分互连:

五条主控总线:

- Cortex-M4内核I总线,D总线和S总线。

- DMA1存储器总线

- DMA2存储器总线

八条被控总线: - 内部FLASH ICode总线

- 内部FLASH DCode总线

- 内部SRAM1

- 内部SRAM2

- AHB1外设

- AHB2外设

- FMC和QSPI

I总线(S0):此总线用于将Cortex-M4内核的指令总线连接到总线矩阵。内核通过此总线获取指令。此总线访问的对象是包括代码的存储器。

D总线(S1):此总线用于将Cortex-M4数据总线连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。

S总线(S2):此总线用于将Cortex-M4内核的系统总线连接到总线矩阵。此总线用于访问位于外设或SRAM中的数据。

DMA存储器总线(S3,S4):此总线用于将DMA存储器总线主接口连接到总线矩阵。DMA通过此总线来执行存储器数据的传入和传出,以及AHB外设或执行存储器之间的数据传输。

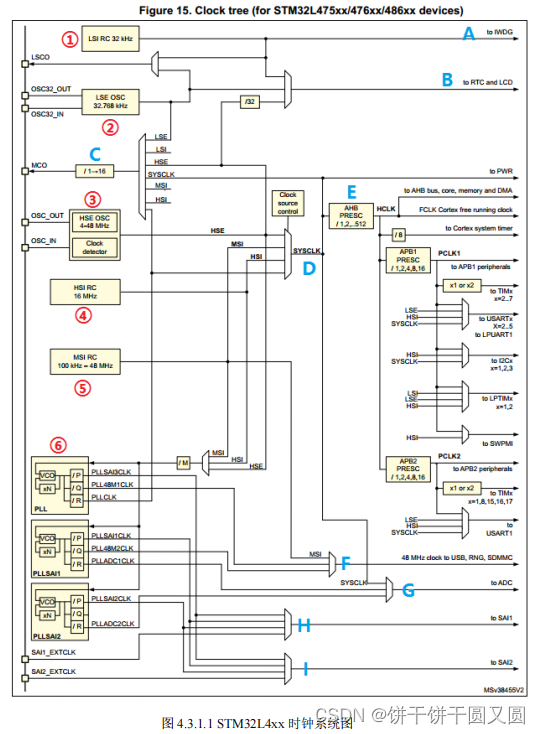

STM32L4时钟树概述

众所周知,时钟系统是CPU的脉搏,就像人的心跳一样。所以时钟系统的重要性就不言而喻了。

STM32L4的时钟系统比较复杂,不像简单的51单片机一个系统时钟就可以解决一切。

于是有人要问,采用一个系统时钟不是很简单吗?为什么STM32要有多个时钟源呢?因为首先STM32本身非常复杂,外设非常的多,但是并不是所有外设都需要系统时钟这么高的频率。比如看门狗以及RTC只需要几十K的时钟即可。同一个电路,时钟越快功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的MCU,一般都是采用多时钟源的方法来解决这些问题。

在STM32L4中,有6个重要的时钟源,为HSI、HSE、LSI、LSE、MSI、PLL。

其中PLL实际是分为三个时钟源,分别为主PLL、PLLISAI1和PLLSAI2。

从时钟频率来分可以分为高速时钟源和低速时钟源,在这6个中,HSI,HSE,MSI以及PLL是高速时钟,LSI和LSE是低速时钟。从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的方式获取时钟源,其中HSE和LSE是外部时钟源,其它的是内部时钟源。

- LSI是低速内部时钟,RC振荡器,频率为32kHz左右。供独立看门狗、RTC和LCD使用。

- LSE是低速外部时钟,频率为32.768kHz的石英晶体。这个主要是RTC的时钟源。

- HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~48MHz。我们的开发板接的是8MHz的晶振。HSE也可以直接做为系统时钟或者PLL输入。

- HSI是高速内部时钟,RC振荡器,频率为16MHz。可以直接作为系统时钟或者用作PLL输入。

- MSI时钟信号由内部RC振荡器产生,其频率范围可通过时钟控制寄存器(RCC_CR)中的MSIRANGE[3:0]位进行调整。

- PLL为锁相环倍频输出。STM32L4有三个PLL:

- 主PLL(PLL)可由HSE、HIS或者MSI提供时钟信号,并具有三个不同的输出时钟。

第一个输出 PLLR,用于生成高速的系统时钟(SYSTEM,最高 80MHz)

第二个输出 PLLQ,可为 USB、RNG 和 SDMMC 提供时钟源

第三个输出 PLLP,可用于 SAI1 和 SAI2 时钟 - PLLSAI1 用于生成精确时钟,同样具有三个不同的输出时钟。

第一个输出 PLLSAI1P,可用于 SAI1 和 SAI2 时钟

第二个输出 PLLSAI1Q,可为 USB、RNG 和 SDMMC 提供时钟源。

第三个输出 PLLSAI1R,可为 ADC 提供时钟 - PLLSAI2 用于生成精确时钟,具有两个不同的输出时钟。

第一个输出 PLLSAI2P,可用于 SAI1 和 SAI2 时钟

第二个输出 PLLSAI2R,可为 ADC 提供时钟

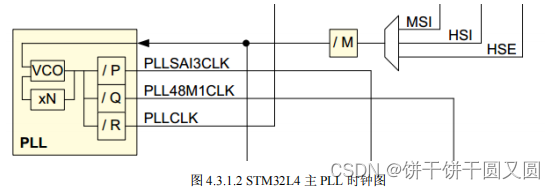

从图中可以看出,主PLL的时钟源要经过一个分频系数为M的分频器,然后经过倍频系数为N的倍频器,出来之后还需要经过分频系数为R(输出PLLR时钟)、或者P(PLLP时钟)、或者Q(输出PLLQ时钟),最后才生成最终的主PLL时钟。

这篇关于STM32L4学习的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!