本文主要是介绍TQ2440开发板学习纪实(6)--- 启用IRQ中断,告别低效的轮询!,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前面的实验中,无论是按键的状态,还是串口的发送接收状态,都是通过轮询的方式进行读取,不仅低效而且严重浪费CPU计算周期,在实际的生产环境下决不能使用!从本文开始,我们进进入一个新的时代,中断处理。

0 中断、异常、软中断,傻傻分不清

在CPU中断处理领域,术语比较混乱。而且有时候同一个术语在不同的语境含义也不相同。这里我们以S3C2440的数据手册为准解释相关概念。

- 异常,英文名Exception。是相对于正常Normal而言的,所有打断正常执行流程的情况都叫做异常。

- 中断,Interrupt。属于异常的一种,指的是CPU执行流程被来自CPU之外的信号打断,更加严格的叫法是外部中断 External Interrupt。

- 软中断,Software Interrupt。实际上它不是中断,只是异常,因为其来源于CPU内部。

在很多文章和书籍中,中断的概念被放大,指的不仅仅是外部中断,而是与这里的异常表示一个含义。比如常见的中断向量,实际上更加严格的名字应该是异常向量。实际使用时,往往对中断和异常不加区分,因为其实际处理流程也是一样的,只是信号来源不同而已。

有些异常和中断还是有区别的,例如未知指令、内存方位失败、软中断的异常是不能够被屏蔽的,CPU必须处理。而外部中断一般都是可以有选择的进行屏蔽和不处理的。

本文也没有区分这两个概念,请读者根据语境自行判断。

1 S3C2440中断原理

S3C2440片内集成了中断控制器,直接读写相关的寄存器,就可以完成中断处理相关的各种设置。中断控制器用来决定哪些中断可以发送至CPU核,而CPU的状态寄存器F、I位则决定是否对来自中断控制器的中断信号进行处理。CPU启动后,中断控制器默认是屏蔽所有中断的,但是CPU的CPSR允许处理中断。

1.1 中断产生流程

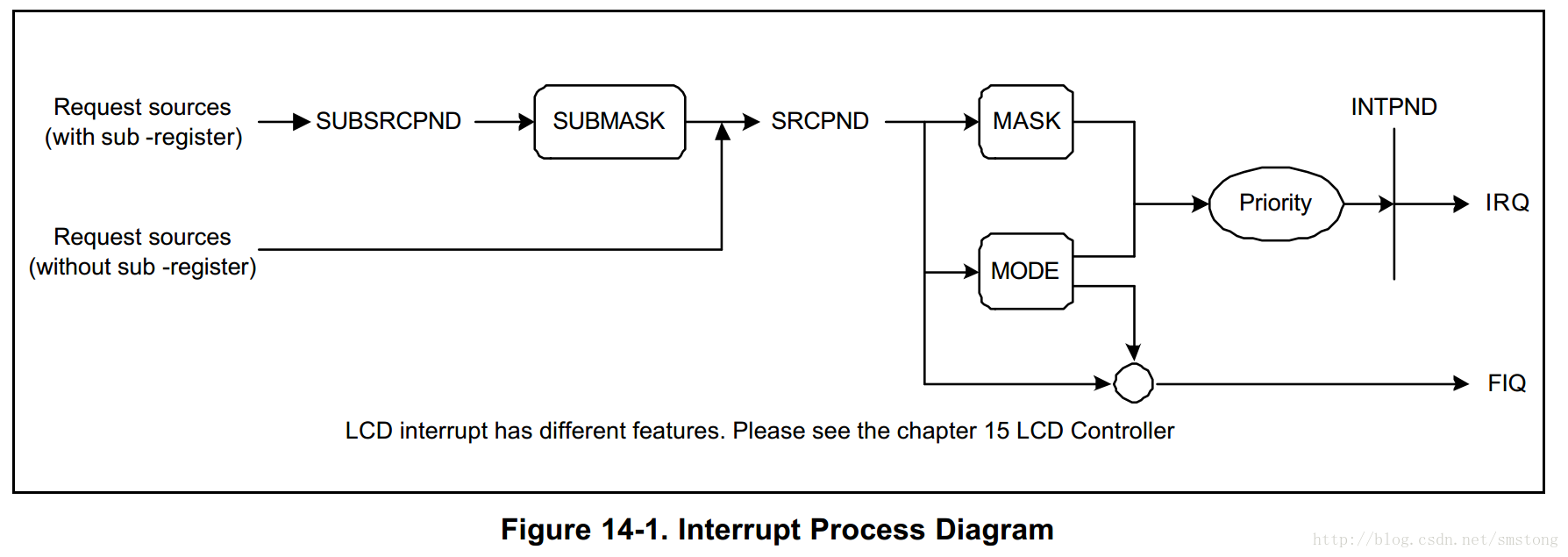

其数据手册上给出了非常清晰中断处理流程,如下图所示。

这里简单说一下几个特点:

(1)有两种中断模式,一般模式(IRQ)和快速模式(FIQ),任何中断源都可以设置为两种模式之一,但是只能有一个中断源被设置FIQ模式。

(2)处理中断时,CPU会自动切换运行模式,并保存当前程序状态寄存器

(3)经过优先级过滤后,最后同一时刻只能有一个中断信号被发送到CPU核。

1.2 中断导致CPU运行模式切换

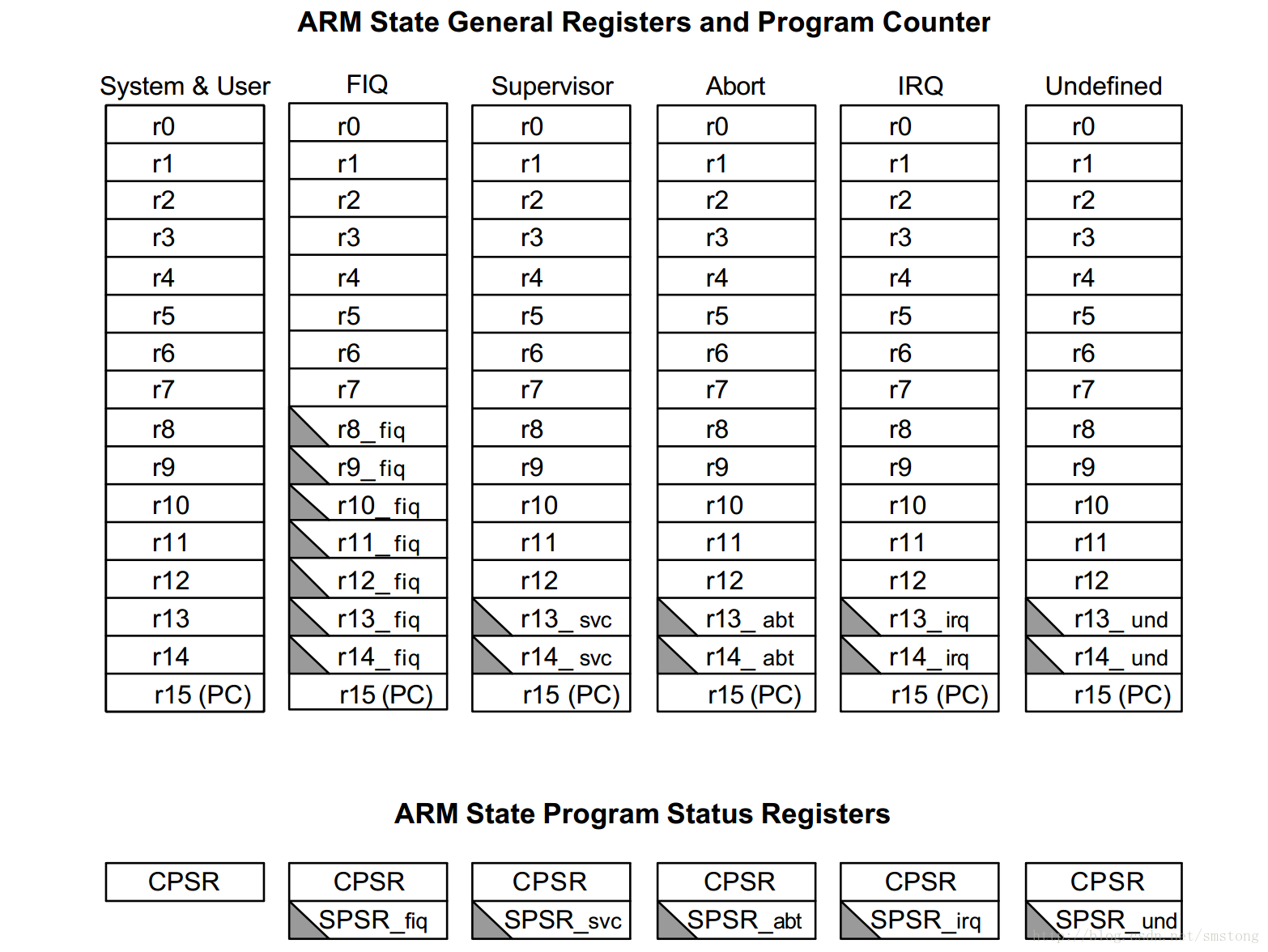

中断处理需要CPU进入中断前保存现场,并且在返回被中断程序时恢复现场,这涉及到大量的操作。为加速这一过程,ARM引出了CPU运行模式,每种模式都有自己独占的一组寄存器供其使用,这样就能够减少现场保存与恢复的寄存器数量。ARM920T共有7种运行模式:

切换模式有两种方式,一是软件设置CPSR寄存器中的模式位;二是当发生异常时,CPU自动切换到特定的模式运行。每种模式看到的寄存器是不完全相同的,尤其是SP寄存器为各模式各有自己的实体,所以需要各个模式分别设置自己的堆栈指针。

1.3 中断向量

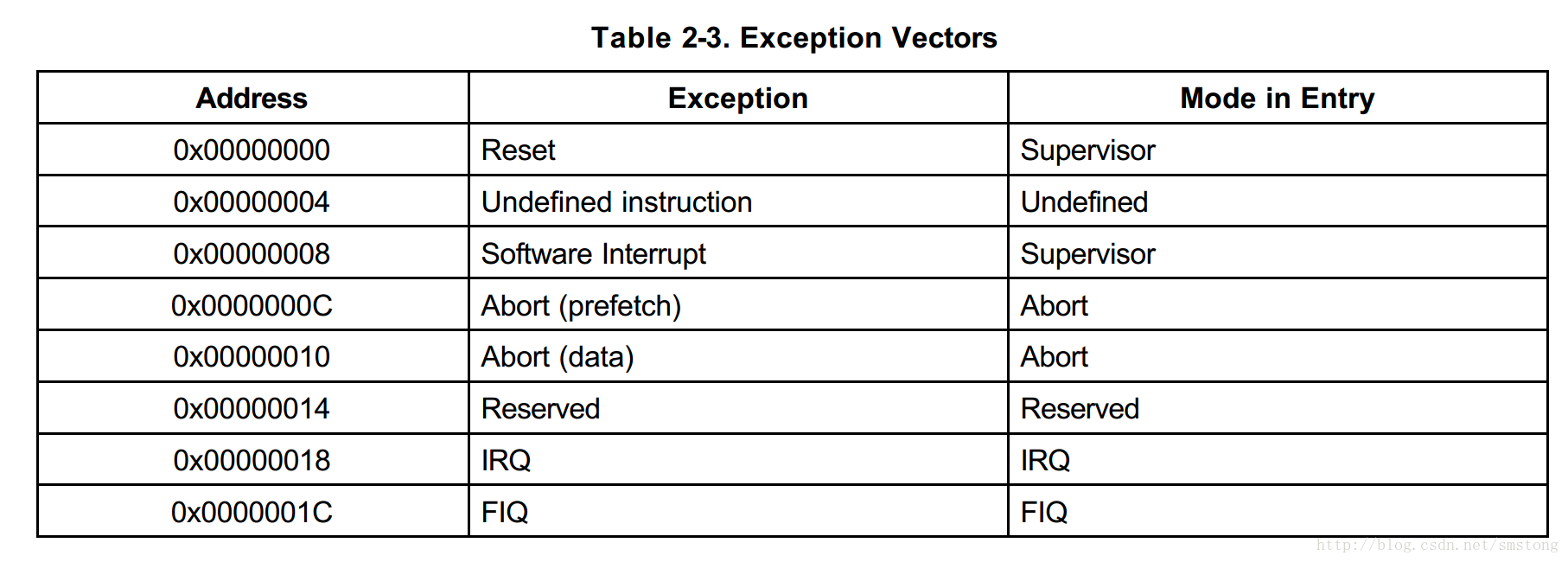

处理中断时,CPU在保存现场后,自动跳转到中断源对应的中断向量地址。对于ARM920T,中断过向量表定义如下:

例如,当处理IRQ类型中断时, CPU自动跳转到0x00000018处执行。由于中断向量只有4个字节大小,所以一般都是只存放一条跳转指令。

2 S3C2440中断控制器配置

S3C2440的中断控制器可以接受来自60个不同的中断源。由于其控制寄存器只有32位,只能直接控制32个中断源,所以引入了分组的概念。把一些相关的中断源分成一组,然后再通过另一个寄存器来甄别一组中的具体的中断源。

2.1 中断屏蔽寄存器

通过INTMSK和SUBINTMSK这两个寄存器来控制60个中断源的使能与屏蔽。本文我们将测试开发板上的4个按键,它们分别对应EINT1, EINT4, EINT2, EINT0四个中断源。其中EINT0,EINT1,EINT2,EINT3是直接对应到INTMSK的第0、1、2、3位,而EINT4-EINT7则共享(或运算)INTMSK的第4位,具体屏蔽哪一个还需要继续设置EINTMASK寄存器的4-7位。

2.2 中断源状态寄存器<

这篇关于TQ2440开发板学习纪实(6)--- 启用IRQ中断,告别低效的轮询!的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!