本文主要是介绍【TC3xx芯片】TC3xx芯片电源管理系统PMS详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

前言

正文

1.供电模式选择(Supply Mode Selection)

1.1 供电域

1.2 供电模式

1.3 供电阈值

1.4 供电上升和下降行为Supply Ramp-up and Ramp-down Behavior

1.5 EVRC产生供电

2. 电源监控

2.1 电源监控原理

2.2 Primary低电压监控

2.3 Secondary高低电压监控

2.3.1 配置高低电压监控是否激活

2.3.2 配置高低电压的阈值

2.3.3 查看各种配置和事件状态

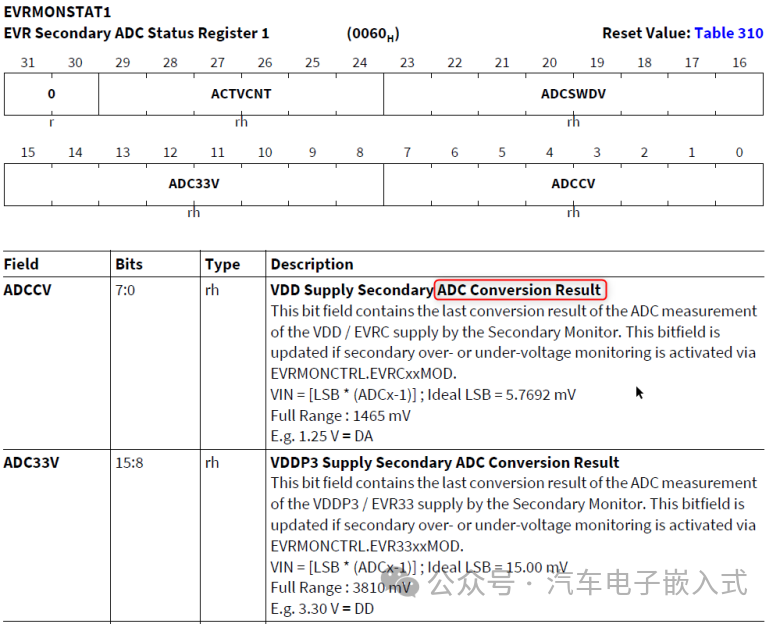

2.3.4 实时查看电压监控值

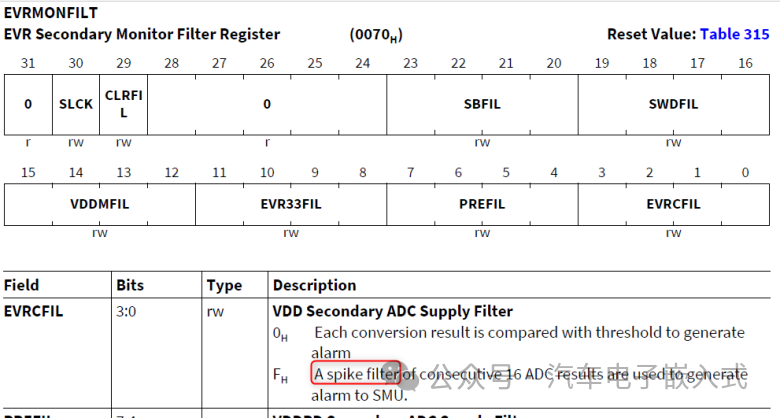

2.3.5 电压监控值是否适用滤波

2.4 电源监控异常中断

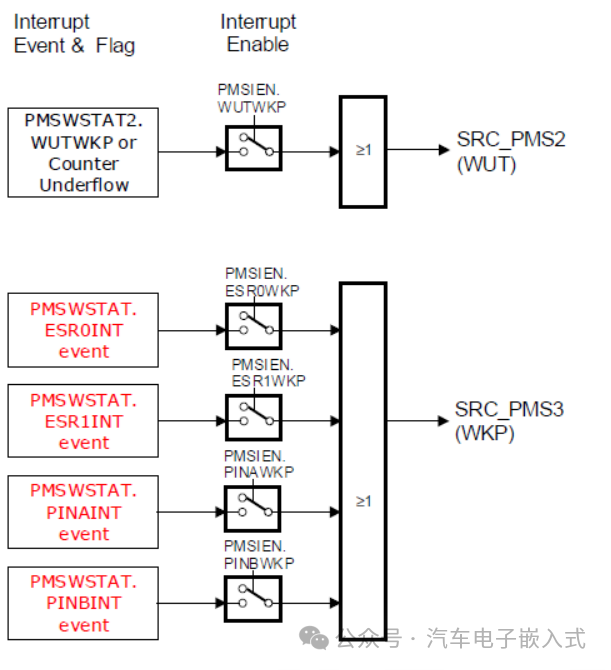

3. 电源管理

3.1 电源管理概述

3.1.1 CPU模式

3.1.2 系统模式

3.2 Standby Mode

3.2.1 VEVRSB单独供电且VEXT断电

3.2.2 Standby RAM

3.3.3 Standby ControllerR(SCR)接口

3.3.4 进入到Standby Mode前应该考虑的问题

前言

电源管理系统(PMS)这一章节很多内容和硬件电路特性相关,很多内容作者也看不懂更不知道怎么去使用,但是,我们本着软件开发的角度去理解TC3xx芯片的电源管理模块,起码要搞明白以下几个问题:

问题1:TC3xx芯片有哪几种电源供电模式,怎么确定系统当前是什么电源模式,各个电源模式的适用场景是?

问题2:如何使能TC3xx芯片PMS模块的电压监控,如何配置电压监控的阈值,如何配置电压异常后的异常中断?

问题3:TC3xx芯片的CPU有几种电源模式,系统上电后的默认模式是什么,各个模式的进入和退出条件是什么?

问题4:如何设计基于TC3xx芯片的ECU低功耗?

带着上述问题,我们来一起学习TC3xx芯片的电源管理系统。

缩略词

| 简写 | 全称 |

| PMS | Power Management System |

| EVRC | Embedded Voltage Regulators |

| LVD | Low Voltage Detection |

| SCR | Standby Controller |

| OCDS | On-Chip Debug Support |

注:本文章引用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

1.供电模式选择(Supply Mode Selection)

1.1 供电域

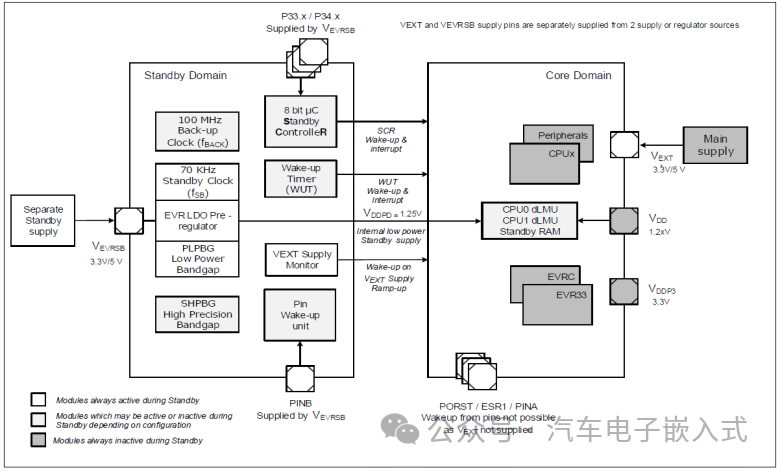

从下图可知,TC3xx芯片不同的功能域需要不同的供电输入,比如:

Standby Domain的供电是VECRSB.

ADC采集模块的供电是VDDM.

CPU的的供电时VDD.

…

这些域的供电,既可以通过外部(externally)电源直接供电,也可以通过外接单电源后通过EVRC转化输出内部供电。这样,就引出了TC3xx芯片的供电模式的概念,请参考下1.2章节。

小问题:为什么要设计为不同的功能域采用不同的供电输入了,而不是统一的一个电源供应?

答:个人理解一个重要原因就是为了做低功耗,不同的功能域是不同的供电输入,也就是意味这在某些场景下,我们不需要用到的一些功能模块可以直接通过配置断电,降低ECU功耗。

1.2 供电模式

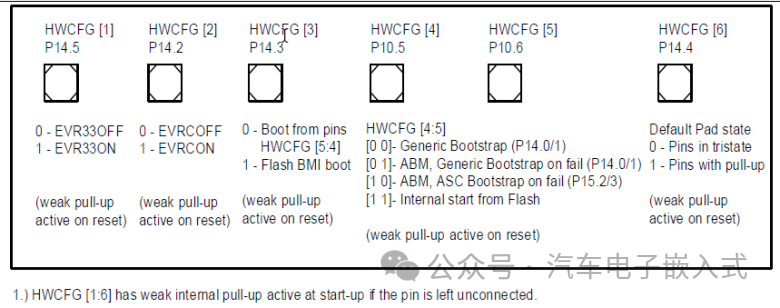

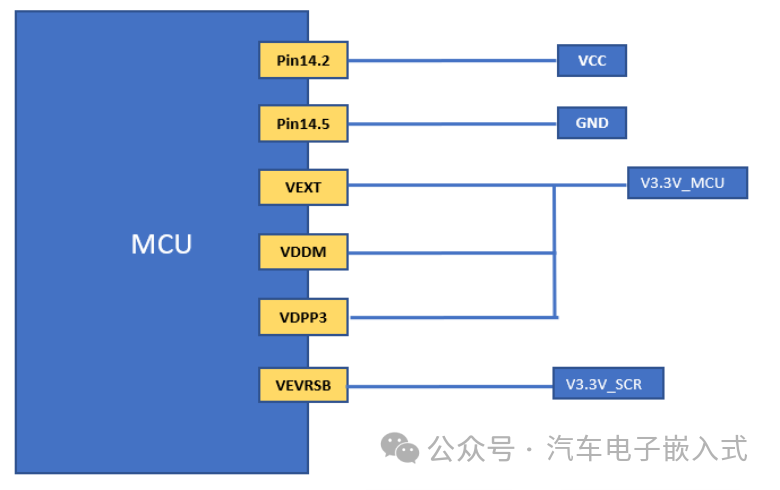

TC3xx的供电模式需要硬件设计来选定,硬件电路对HWCFG [2:1]的配置也就是P14.2和P14.5的电平输入状态决定TC3xx芯片的供电模式。

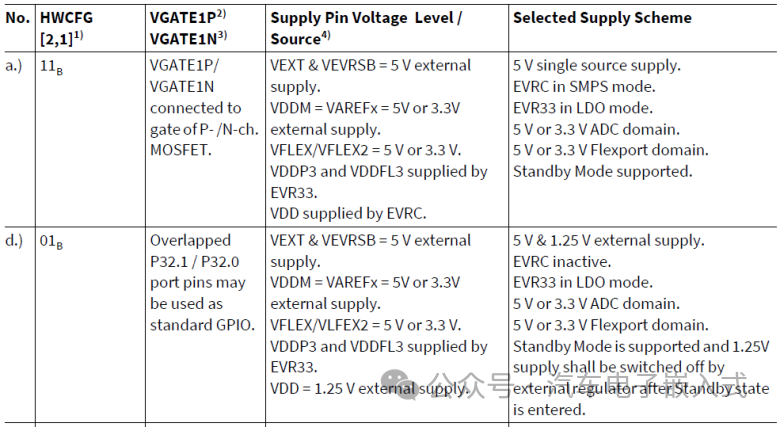

两个Pin脚,也就有4中输入组合,也就对应下表的4中电源供电模式。

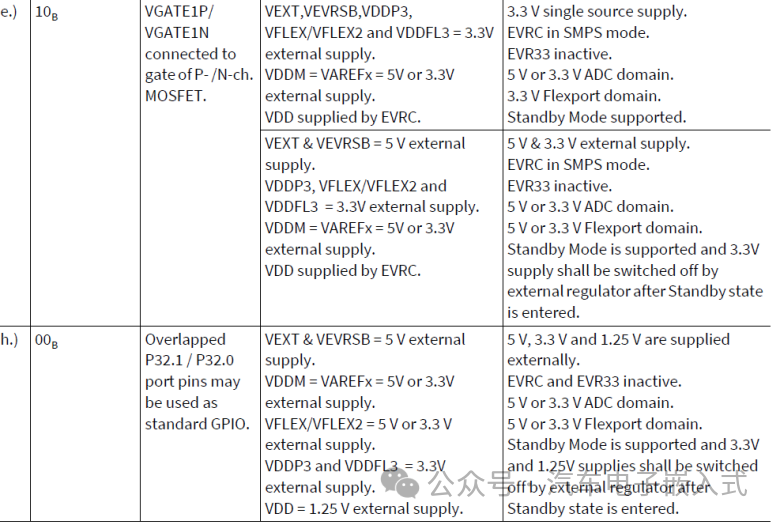

以HWCFG[2:1] = 10B来举例说明:

1.HWCFG [1] = 0,也就是EVR33 OFF。EVR33是PMS内部一个硬件模块,可以生成3.3V的内部供电,EVR33 OFF也就是Disable了EVR33了,不需要这个供电了。

2. HWCFG [2] = 1,也就是EVRC ON。EVRC是PMS内部一个硬件模块,可以生成1.25V的内部供电,EVR33 ON也就是Enable了EVRCC了,内部其他模块可以适用1.25V这个供电。

3.

给所有Pin脚(Pad)供电的VEXT,

给Standby Domain(SCR)供电的VEVRSB,

给Flash供电的VDDP3,以及VFLEX/VFLEX2和VDDFL3都为外部3.3V供电。

给ADC供电的VDDM和VAREFx可选为外部5V或者3.3V供电。

给CPU供电的VDD由EVRC产生。

小问题:HWCFG[2:1] = 10B时为3.3V单电源供电模式(3.3V single source supply),其实ADC模块还是可以选择为外部5V供电的?

答:我们所说的单电源供电主要说的就算VEXT和VDDP3这两个电源。给ADC供电的VDDM是另外独立的概念,也就是说在3.3V单电源供电模式下ADC供电电源VDDM还是可以外接3.3V或者5V电源。

4.外部3.3V单电源供电模式,并不是所有的电源都由同一个外部电源供应。考录到ECU的低功耗设计,起码用于Standby Domain的VEVRSB和VEXT等电源应该独立分开,也就是能保证ECU进入到Standby模式后能把其他电源断开,降低功耗。

5. TC3xx芯片对HWCFG [6:1] 对应的引脚都有一个内部的弱上拉(weak pull-up),如果芯片上电后如果外部没有对应的电路连接到HWCFG [6:1] 也能保证芯片的电源模式是确定的(11B模式)。

小问题:什么是弱上拉?

答:和C语言中的弱函数(weak function)类似,如果我们定义了一个呆weak修饰的函数则这个函数为弱函数,反正为强函数,同时定义一个相同函数签名的弱函数和强函数,编译器只会认强函数,但是没有定义强函数的时候弱函数也是可以编译进可执行文件的。类比到硬件的弱上拉,也就是如果外部没有强上拉或者下拉的时候,弱上拉能保证Pin是处于确定的高电平状态的。

1.3 供电阈值

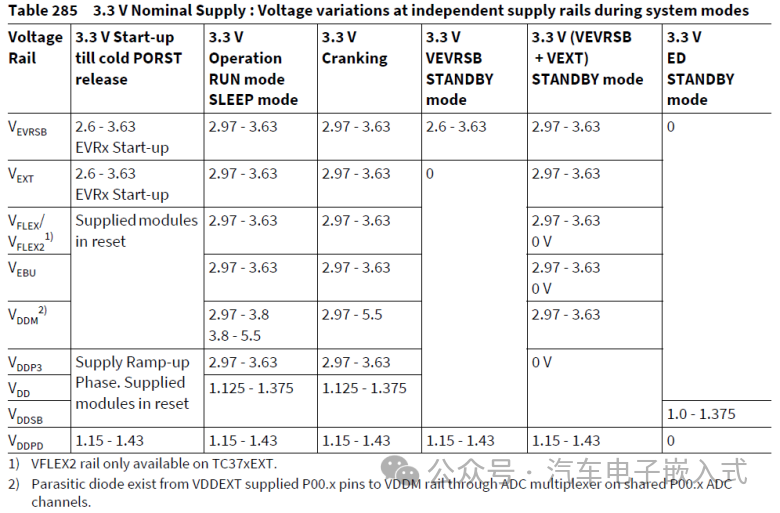

4中供电模式都有对应的供电阈值,这里仅接收3.3V单电源供电模式的阈值。 如下图所示,如果供电电压超过了阈值范围,就可能产生SRC,后文介绍。这里只要了解下3.3V供电时,各个电源的正常电压范围即可,在ECU开发阶段首先得保证ECU的供电是正常的,也就是用万用表测量电源电压后和这个表对比。

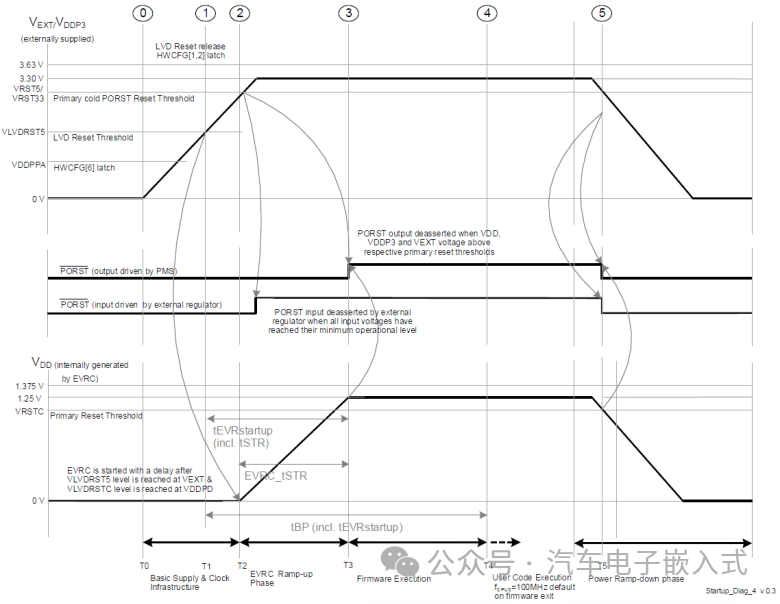

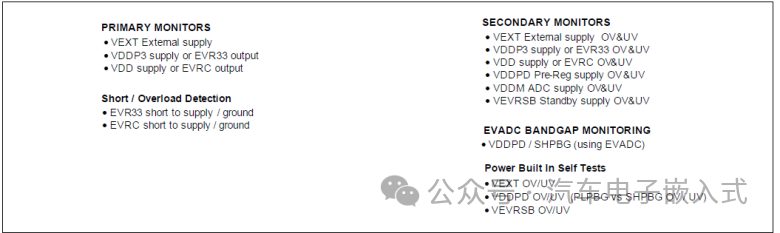

1.4 供电上升和下降行为Supply Ramp-up and Ramp-down Behavior

四种供电模式配置都有对应的上下电行为,这里仅介绍常见的3.3V单电源供电模式。

3.3V单电源供电模式时,VEXT = VDDP3 = 3.3V. VDD由内部的EVRC产生。

. PORST这个引脚既是输入引脚也是输出引脚,当PORST(Input)或者PORST(output)激活的时候(Active, Low level)PORST处于激活状态。

. PORST (input) 激活意味着外部电路/设备通过将 PORST 引脚拉低而保持复位MCU请求。 建议保留所激活的 PORST (input) ,直到外部电源高于相应的复位阈值。

. PORST (output) 激活意味着 μC 在内部Reset并拉低PORST 引脚,这样可以将Reset信号传播到外部设备。 当三个供电 (VDD , VDDP3 或 VEXT) 中至少有一个供电低于主欠压重置阈值时, μC 会拉低(Active) PORST (output)。 当所有电源设备都高于其主重置阈值且基本电源和时钟基础设施可用时。 μC 会拉高 PORST (output)引脚。

注意:对于我们而言,着重理解在上下电过程中PORT引脚是否处于Active状态就行,处于Active状态时,MCU就处于Reset状态。

注意:经常会在Datasheet看到Assert(Asserting、Asserted),De-assert(Deassert、deasserting、deasserted)等词,如下面这句:

PORST is active/asserted when either PORST (input) or PORST (output) is active/asserted.

那这个词是什么意思呢,下面就来解释一下这两个词的意思:

Assert:意思就是把信号变为active(可以理解为有效),根据系统有求不同,该有效电平可以是高电平(即高有效)也可以是低电平(即低有效)。

De-assert:意思就是解除active状态,就是信号变为非active状态,可以是高也可以是低。

英文解释:

Assert:Set a signal to its “active” state;

De-assert: Set a signal to its “inactive” state。

If a signal is active-low, “asserting” that signal means setting it low and deasserting it means setting it high。

1.5 EVRC产生供电

对于EVRC的内部原理都是一些硬件特性的描述,我们着重了解以下几点即可:

单电源3.3V供电时:

1. EVRC产生一个1.25V的VDD电源给CPU供电。

2. 单电源3.3V供电时硬件电路要外接一个N mos管和一个P mos管.

3. EVRC内部可以配置用于内部同步的PWM频率,适用0.8MHz还是1.8MHz会影响ECU的EMI/EMC特性。

至于其内部复杂的原理,可以在需要的时候再去详细了解。

2. 电源监控

2.1 电源监控原理

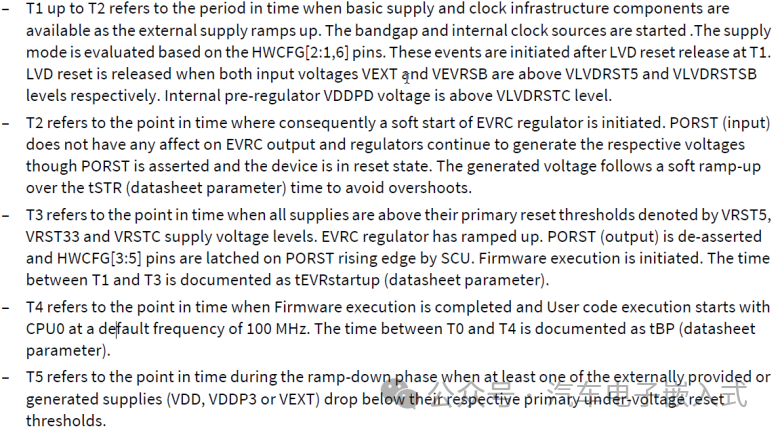

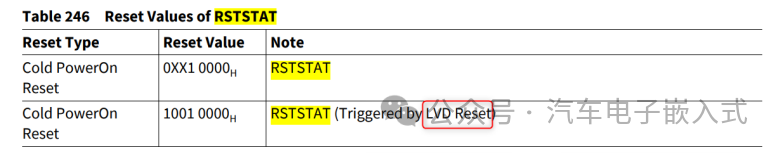

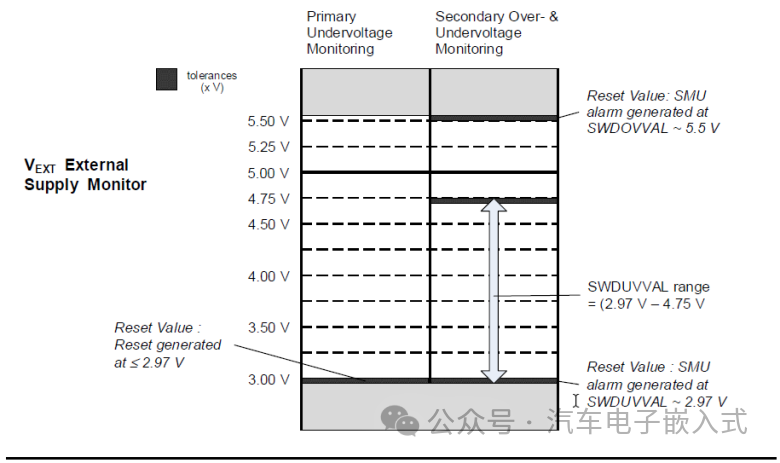

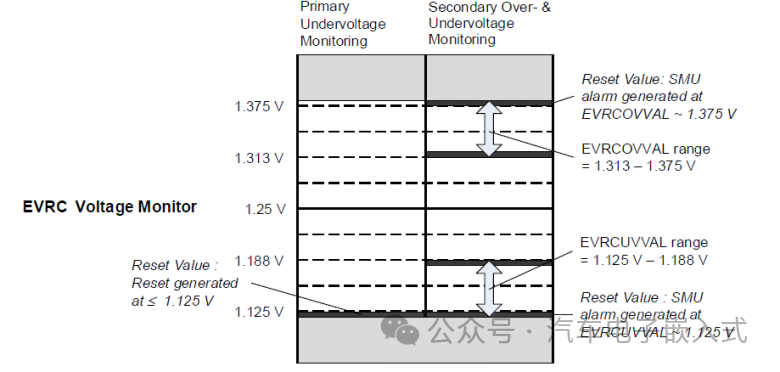

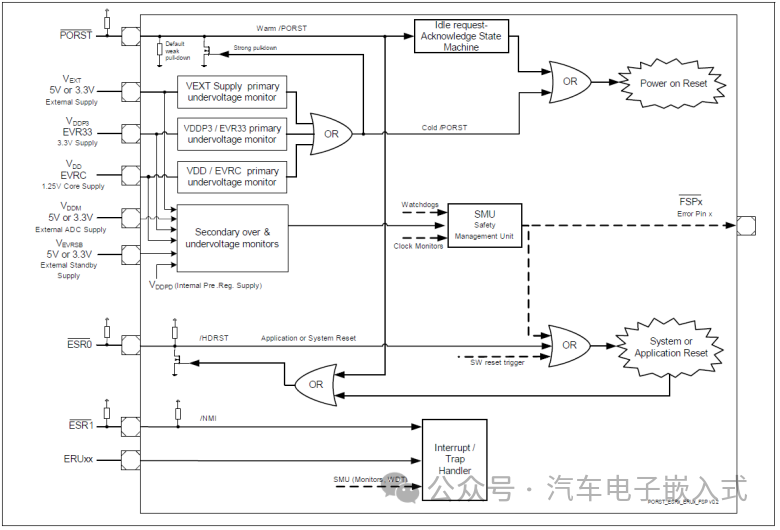

两种电源监控模式,Primary Monitor主要监控VEXT VDDP3 VDD三种电源,三个电源都有一个最小的threshold ,如果监控到小于最小的threshold就会触发LVD Reset。Secondary Monitor除了VEXT VDDP3 VDD外还监控VEVRSB VDDM VDDPD,它监控的电源可以设置一个范围,一旦超过范围就会产生一个Alarm给到SMU。Primary Monitor和Secondary Monitor的VREF都用到SHPBG的一个模块(芯片内部的一个DCDC的模块)。为了功能安全的考虑,PLPBG这个DCDC模块在电源上升/建立过程中会和SHPBG进行相互的检测,保证电源部分的冗余性和多样性。

2.2 Primary低电压监控

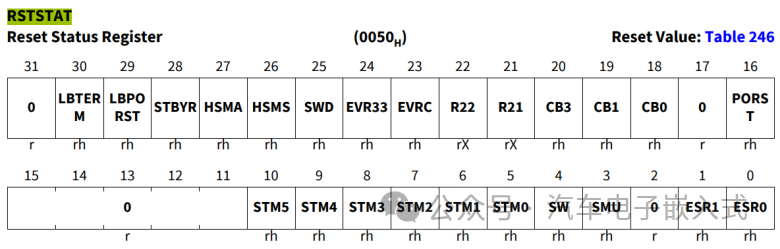

低电压监控一定是Enable的,用户不可屏蔽。低电压检测的阈值因芯片型号的不同而不同。检测到低电压后,芯片持续拉低(Active)PORST,产生Cold Reset.复位后,可通过RSTATAT寄存器来查看是否是低电压复位。

2.3 Secondary高低电压监控

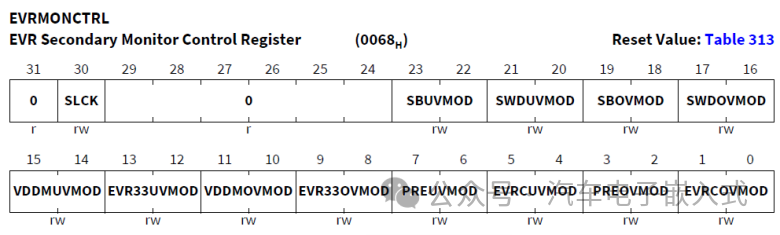

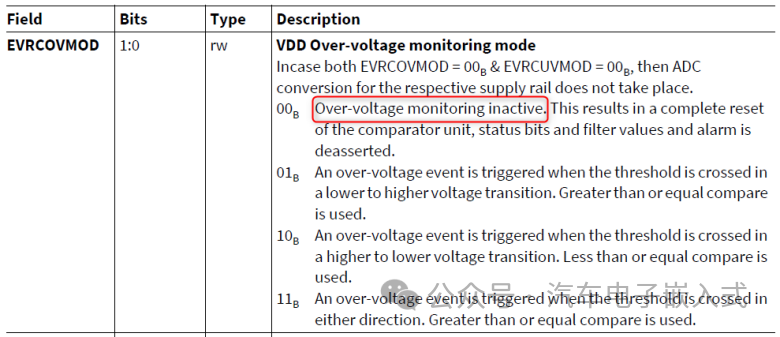

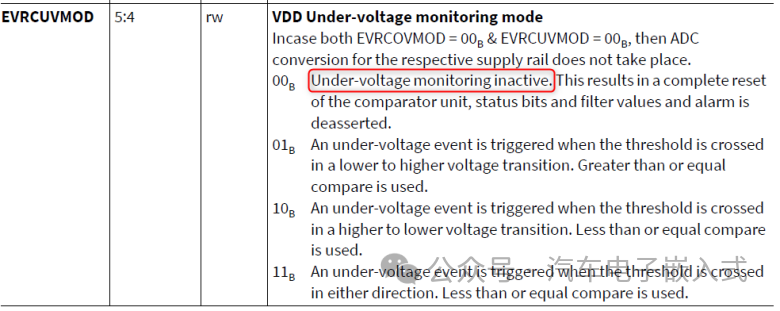

Secondary高低压监控是可配置的,可以配置高低压的阈值以及是否产生Alarm请求到SMU。

2.3.1 配置高低电压监控是否激活

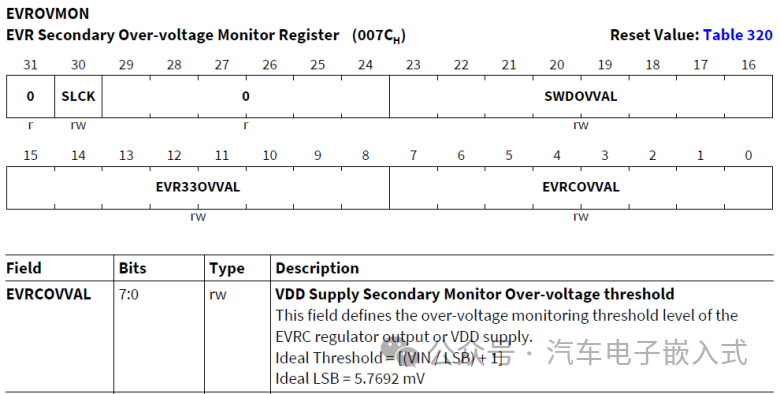

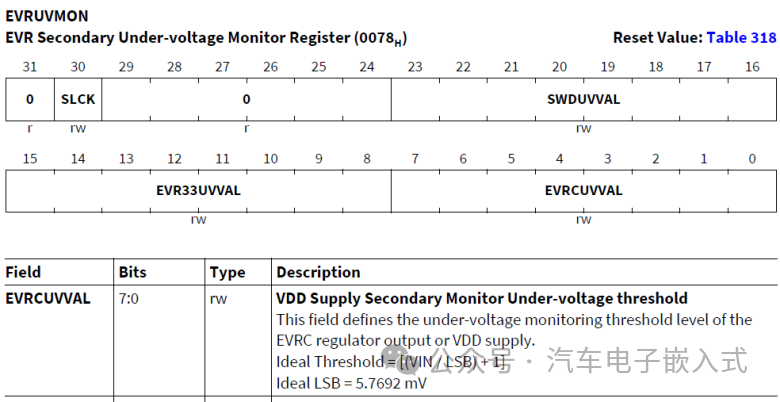

2.3.2 配置高低电压的阈值

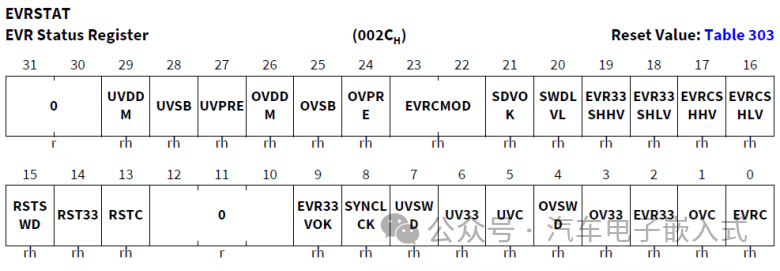

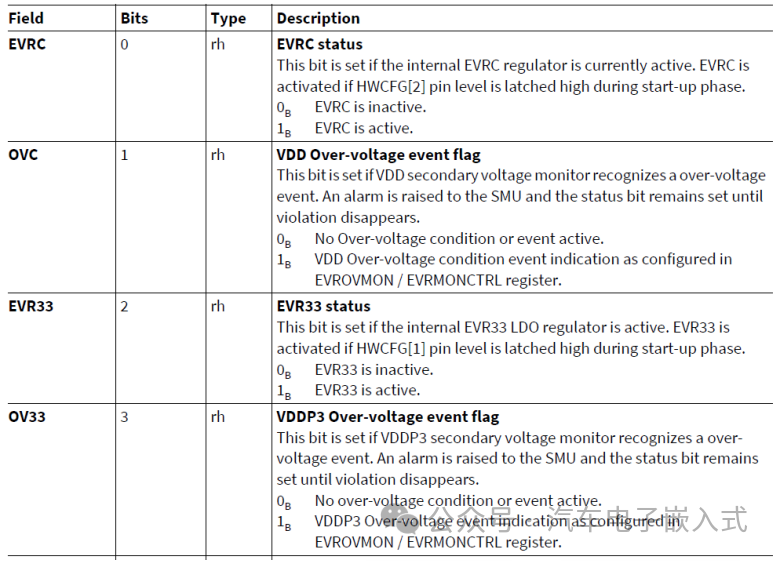

2.3.3 查看各种配置和事件状态

2.3.4 实时查看电压监控值

2.3.5 电压监控值是否适用滤波

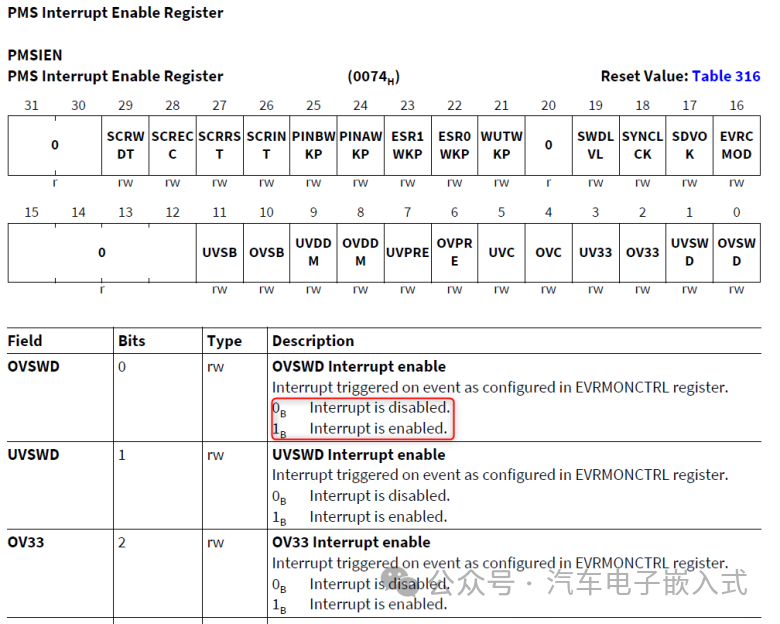

2.4 电源监控异常中断

PMS的Secondary监控到电压异常后能产生SRC请求给到IR(Interrupt Router)模块,IR模块将请求路由到CPU产生中断(注意:SRC可以通过IR模块路由到DMA或者CPU)。

值得注意的是,是否产生SRC请求,需要配置PMSIEN寄存器。

3. 电源管理

3.1 电源管理概述

3.1.1 CPU模式

从单个CPU角度来讲,PM模块能够管理的CPU的两个电源模式:

. CPU Run Mode

. CPU Idle Mode

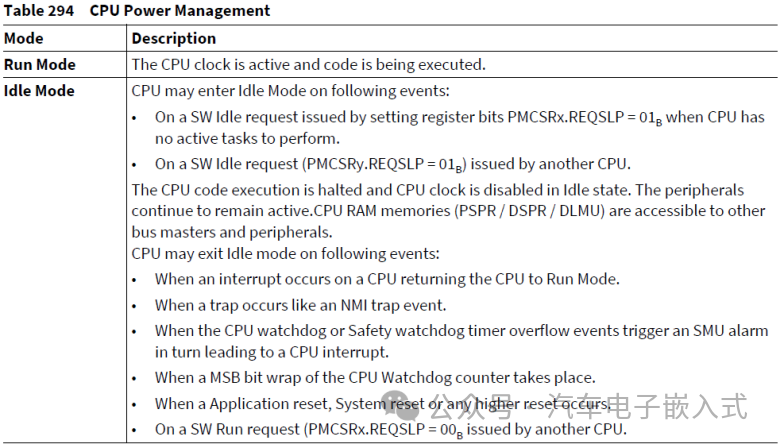

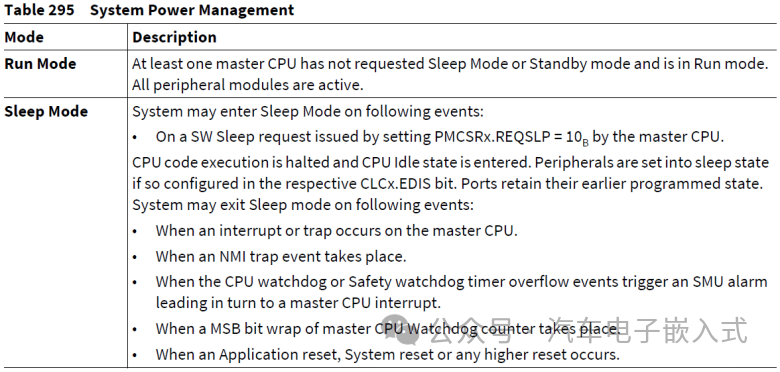

关于PMS模块管理的两个CPU Mode的描述入下表所示:

注意IDLE模式的进入和退出条件,通过寄存器设置进入IDLE模式,中断或者Trap退出IDLE模式。

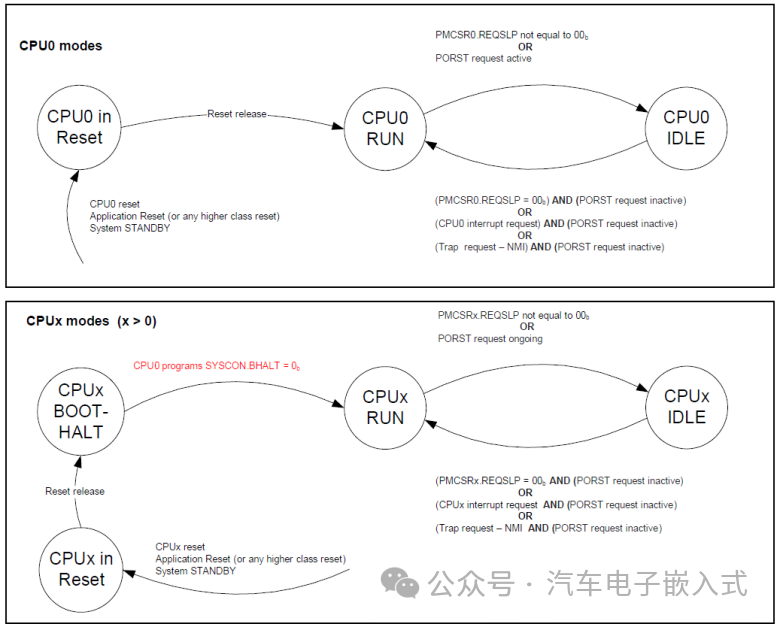

站在整个芯片的角度来看,CPU模式分为Master CPU(CPU0)模式和Slave CPU(CPUx, x=0,1,2,3,4,5…)模式。

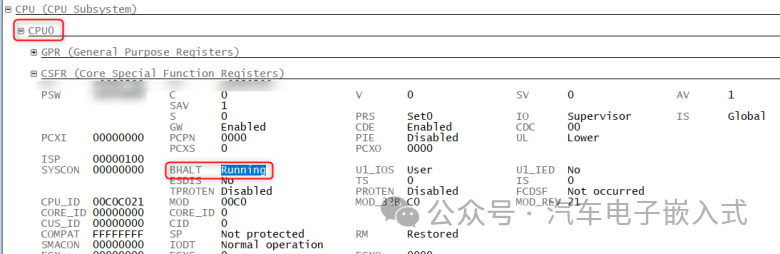

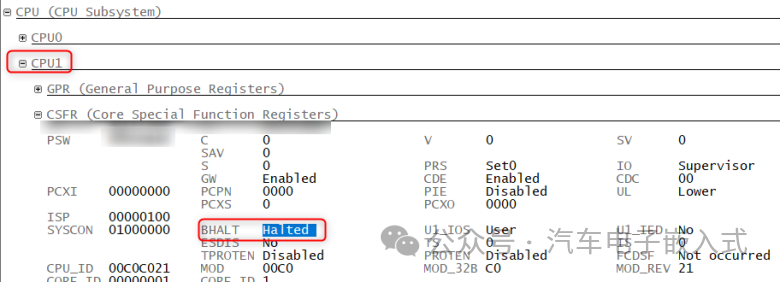

CPU0 modes: CPU0复位后,CPU0自动切换到RUN模式,RUN和IDLE模式之间可以通过PMS模块的PMCSR0寄存器的REQSLP位域控制切换。

CPUx modes: CPUx复位后,CPU自动进入到Halt模式(CPUx是不工作的),从Halt模式单向切换到RUN模式需要控制SYSCON.BHALT = 0,RUN和IDLE模式之间可以通过PMS模块的PMCSR0寄存器的REQSLP位域控制切换。

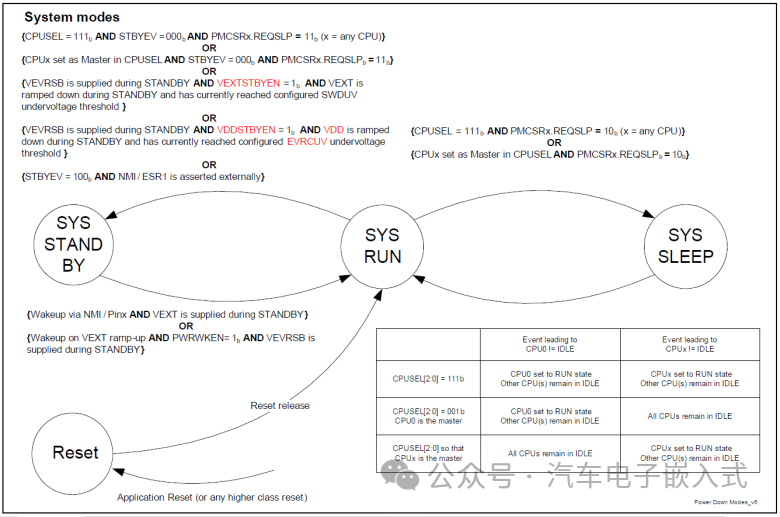

3.1.2 系统模式

从系统(System)角度来讲,PM模块能够管理系统的三个电源模式:

. System Run Mode

. System Sleep Mode

. System Standby Mode

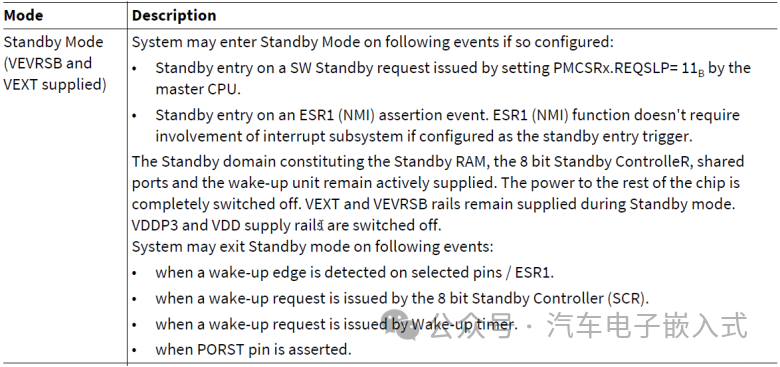

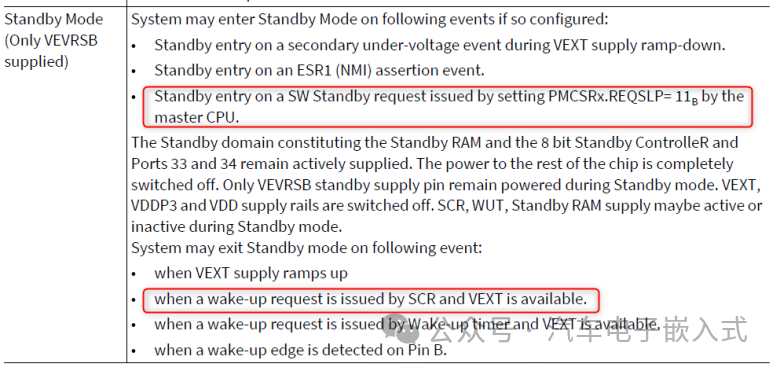

关于PMS模块管理的System Mode的描述入下表所示:

需要注意的是系统Standby Mode会因硬件的设计的不同(供电模式)而不同,VEXT和VERSB如果是同一个外部供电则进入Standby Mode后VEXT和VERSB都还有供电,如果VEXT和VERSB是单独供电,则进入Standby Mode后会切断VEXT的供电只有VERSB供电,这样进入和退出Standby模式的条件所有不同。

3.2 Standby Mode

Idle和Sleep模式一般在ECU设计上不会使用,因为Standby模式才能降到最低的功耗。这里也仅介绍Standby Mode,Idle和Sleep模式想了解的可以去参考芯片手册。

Stand模式又以VEVRSB单独供电的硬件设计方式最为常见,这里也进介绍VEVRSB单独供电的模式。

3.2.1 VEVRSB单独供电且VEXT断电

进入到Standby模式后,图中深灰色的模块一点是Inactive的(不工作),浅灰色的模块可配置为Active或者Inactive,无色部门的模块一定是工作的。

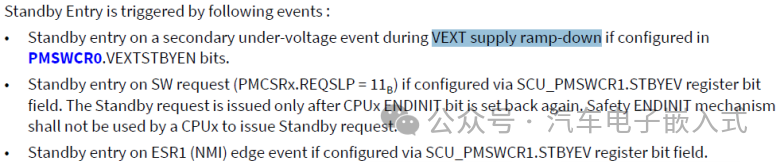

进入Standby模式可以通过配置寄存器的方式,也可以通过VEXT supply ramp-down方式,对于的寄存器或者外部操作如下:

退出Standby模式,每种退出机制都需要配置PMSWCR0寄存器的Enable位且都在VEXT已经供电后进行:

3.2.2 Standby RAM

什么是Standby RAM?

通过配置,进入到Standby Mode后依然能够保持供电也就能保存数据的的RAM。

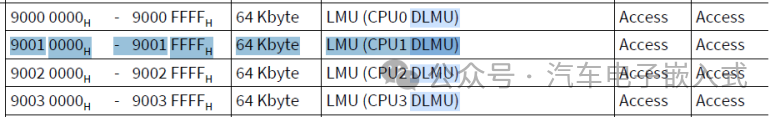

Standby RAM具体是那些RAM?

DLMU0的0x9000 0000 – 0x900 7FFF这前(lower half)32Kbyte是DLMU0的Standby RAM.

DLMU0的0x9001 8000 – 0x9001 FFFF这后(upper half)32Kbyte是DLMU1的Standby RAM.

其他都不是Standby RAM.

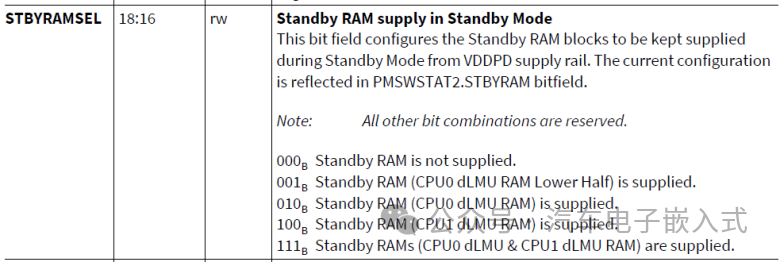

如何使能Standby RAM?

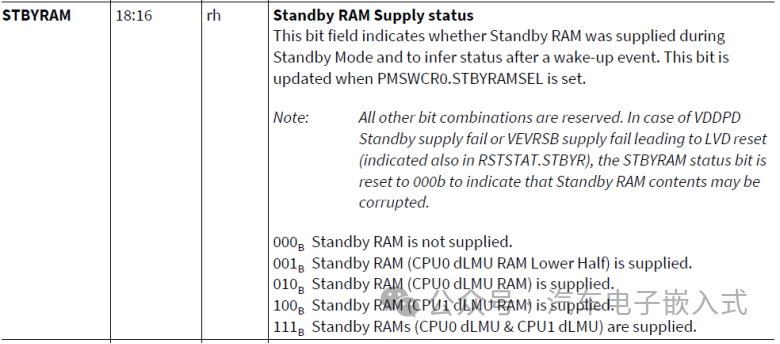

配置PMSWCR0寄存器的STBYRAMSEL位域Enable/Disable Standby RAM. 配置完后可以通过PMSWSTAT2寄存器的STBYRAM位域来检测Standby RAM是否配置成功。

注意:配置使用了Standby RAM后,目的就是为了进入Standby状态后保存RAM的数据,所以当唤醒系统后一般会重新运行软件,这个时候在Startup Software里面需要判断PMSWSTAT2. STBYRAM信号来决定要不要初始化Standby RAM区域(没有使用Standby RAM就需要进行RAM初始化,防止ECC错误产生)。

3.3.3 Standby ControllerR(SCR)接口

Tricore在RUN的初始化阶段会启动SCR,Tricore进入到Standby Mode后SCR还在运行,一般通过SCR来负责唤醒Tricore. 这样就需要Tricore和SCR直接由硬件接口。

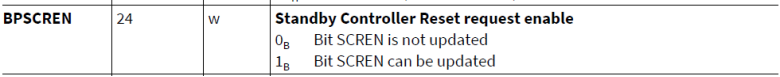

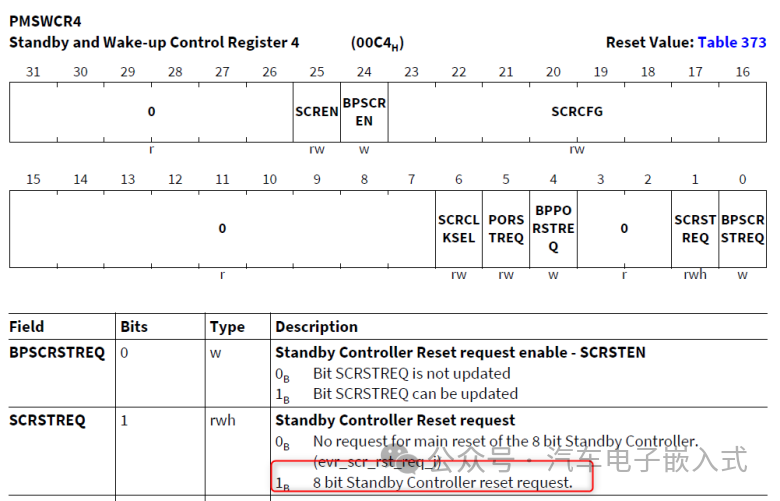

PMSWCR4.SCREN寄存器信号配置是否使能SCR.

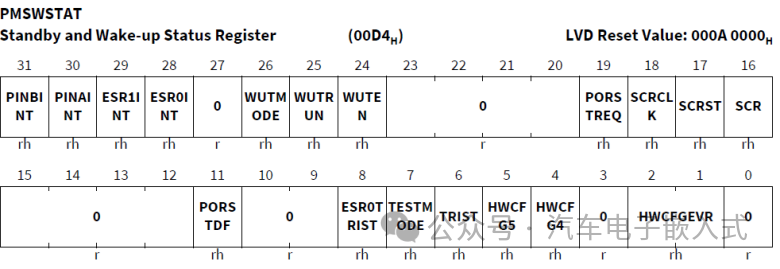

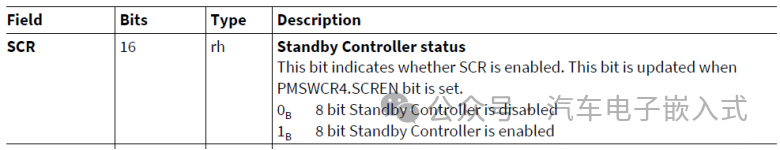

PMSWSTAT.SCR寄存器位域信号能反馈SCR是否已经使能。

PMSWCR4.SCRSTREQ寄存器位域信号能在Tricore核请求复位SCR.

PMSWSTAT.SCRST寄存器信号能标识SCR有没有复位。

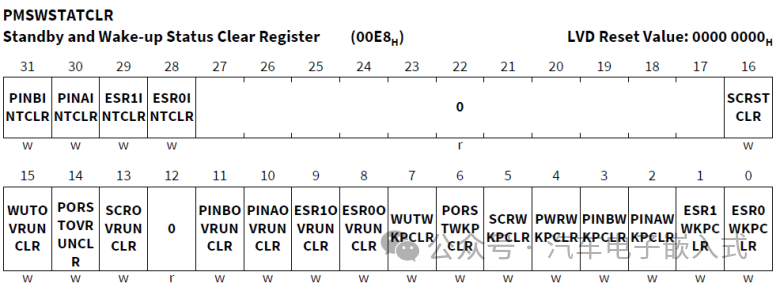

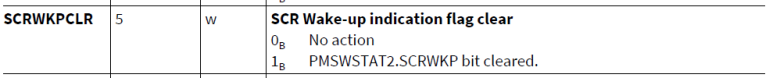

PMSWSTATCLR.SCRSTCLR寄存器信号请求清除SCR复位标志。

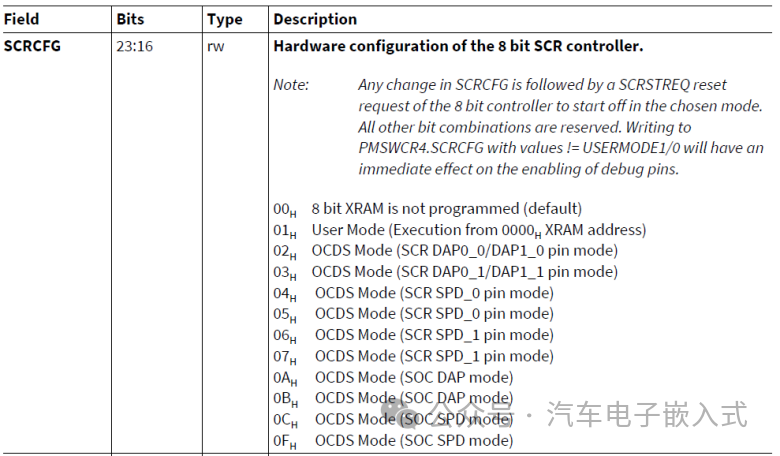

在Reset释放后,固件将根据 PMSWCR4.SCRCFG的硬件配置初始化 SCR 子系统。

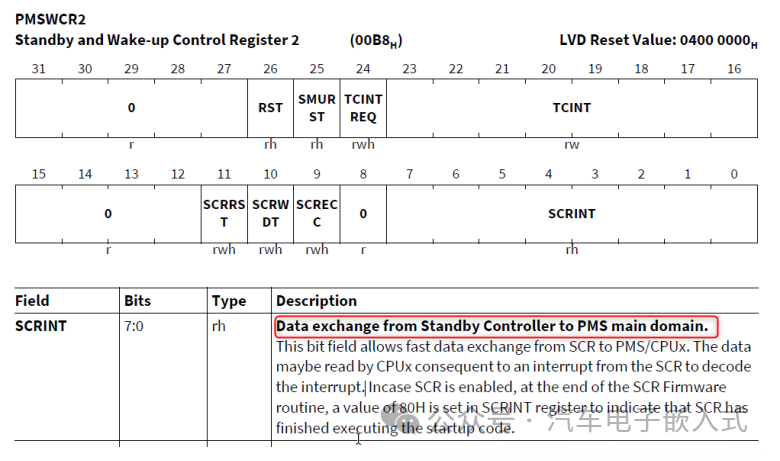

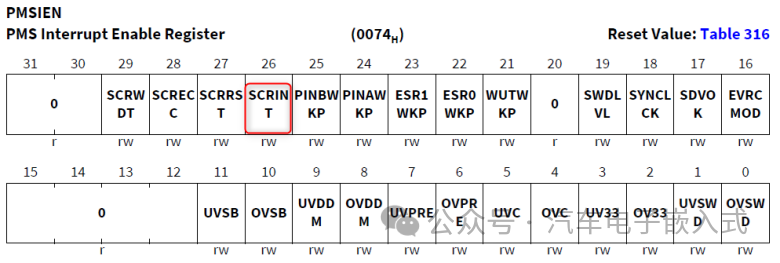

SCR通过SCRINTEXCHG字段传递信息到Tricore,Tricore通过PMSWCR2.SCRINT寄存器字段从 SCR 到 PMS/CPUx 的快速数据读取。 CPUx 读取的数据可能是由于 SCR 中断而导致的,从而对SCR中断进行解码。使用此功能的前提是配置PMSIEN. SCRINT使能。也就是:

SCR 写数据 -> SCRINTEXCHG

Tricore读数据 -> PMSWCR2.SCRINT(前提是PMSIEN. SCRINT使能)

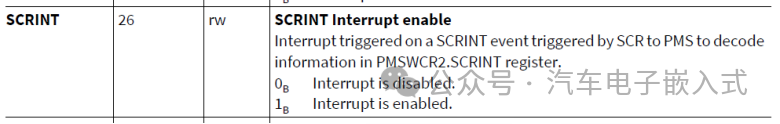

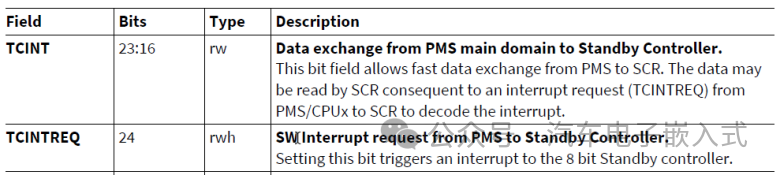

PMSWCR2.TCINTREQ寄存器字段能触发SCR中的中断,PMSWCR2.TCINT寄存器字段能快速的从Tricore传递信息到SCR. SCR可以从TCINTEXCHG读取数据,也就是:

Tricore写数据 -> PMSWCR2.TCINT

SCR读数据 -> TCINTEXCHG

SCR能通过NMICON.SCRINTTC寄存器字段请求Tricore中断,

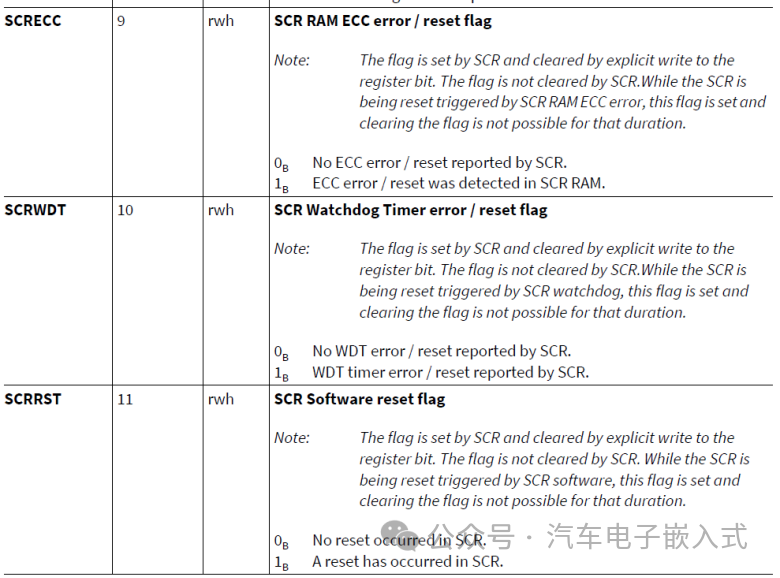

SCR的ECC错误,WDT看门狗报错,SCR内部软件复位标志都可以通过PMSWCR2.SCRECC, SCRWDT and SCRRST寄存器字段获取。

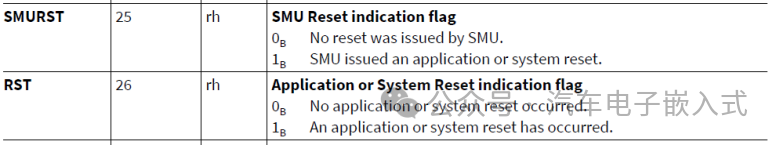

Tricore的各种复位(application,system, power-on resets)可以标识在PMSWCR2.RST字段,并能传递到SCR的MRSTST.RST寄存器字段。SMU引起的复位标识在PMSWCR2.SMURST寄存器字段,能传递到SCR寄存器的MRSTST字段(SCR中可能产生中断)。

如果配置了 SCRWKEN 寄存器字段, SCR 能将主核从Standby 状态唤醒。 当 SCR 以 20 MHz 运行时,课堂通过配置 SCRWKEN 启用 SCR 唤醒。 SCR SW 通过 STDBYWKP 寄存器中的 SCRWKP 位发出唤醒请求,如 SCR SCU 章节所述。 在主核唤醒时,设置了 SCRWKP 事件标志,该标志应通过 SCRWKPCLR 寄存器位清除。

3.3.4 进入到Standby Mode前应该考虑的问题

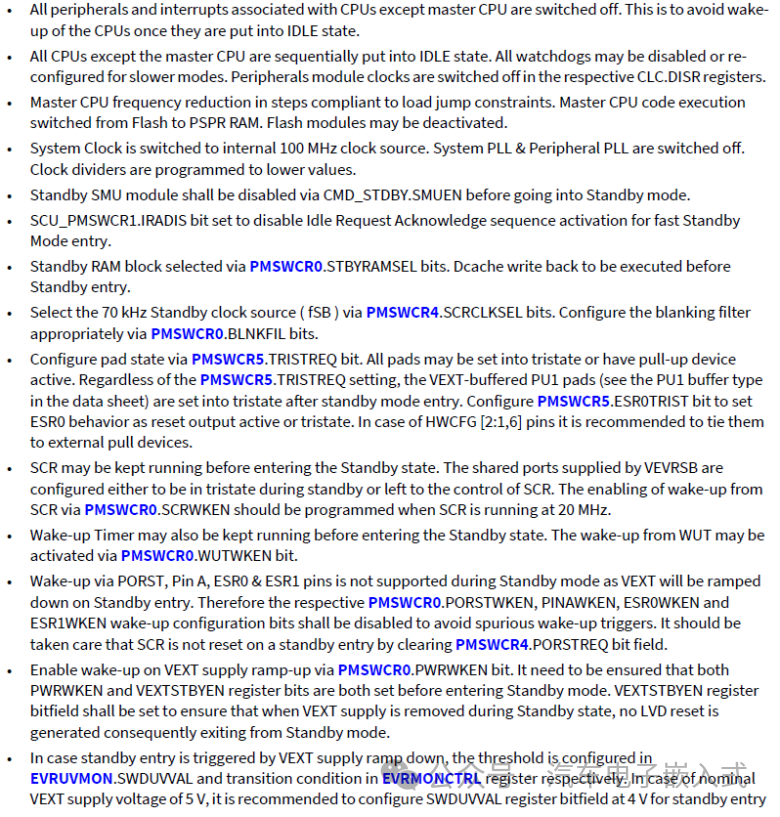

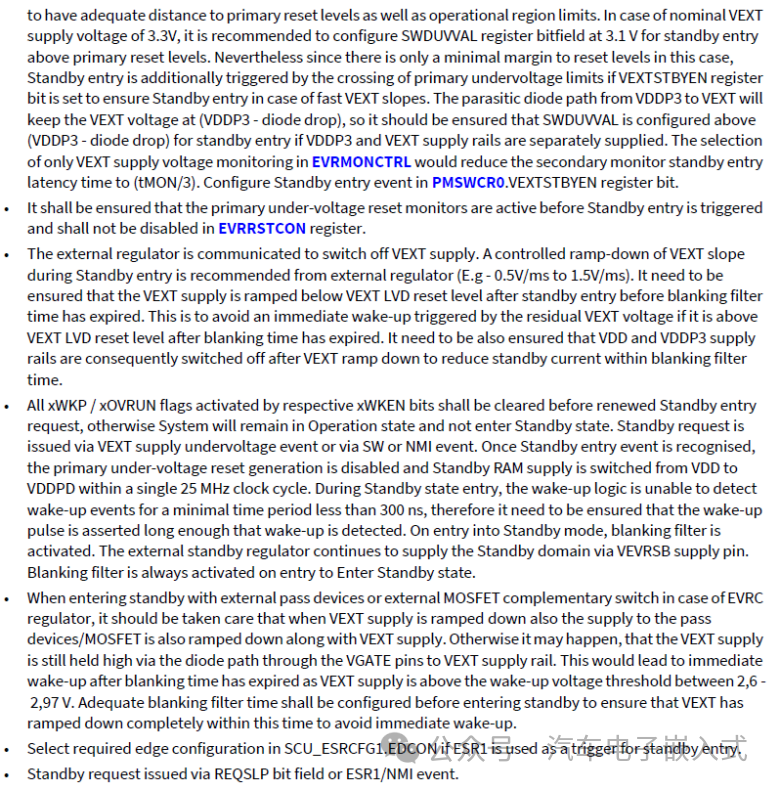

进入Standby模式之前,模块应该按顺序关闭,以避免大负荷跳动。

这篇关于【TC3xx芯片】TC3xx芯片电源管理系统PMS详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!