本文主要是介绍Arm的Morello SoC与CHERI架构,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Arm发布Morello SoC原型,使用CHERI架构显著改善内存安全。

一、Morello SoC

十多年来,剑桥大学的研究人员一直在开发能力 硬件增强 RISC 指令 (Capability Hardware Enhanced RISC Instructions) 架构模型。今天,Arm 宣布推出首款基于 Arm 的 SoC 与 CHERI 架构集成的硬件,这是其为期五年的 Morello 计划的一个重要里程碑。

Arm 与剑桥研究人员密切合作,开发了一个 64 位 Armv8-A 驱动的 SBC(单板计算机),以允许测试其声称的“显着改进”的硬件增强设备安全性。

剑桥大学和 Arm 一直在规划一个新架构,以增强基于 Arm SoC的内存访问安全。根据微软和谷歌的研究,通过补丁解决的漏洞中,超过三分之二涉及内存安全问题。

该SoC和演示板通过 UKRI 数字安全设计 (DSbD) 计划向微软和谷歌等合作伙伴以及行业和学术界感兴趣的合作伙伴发布。Innovate UK 将在 1 月 25 日的发布网络研讨会上发布有关这些板分布的更多信息。

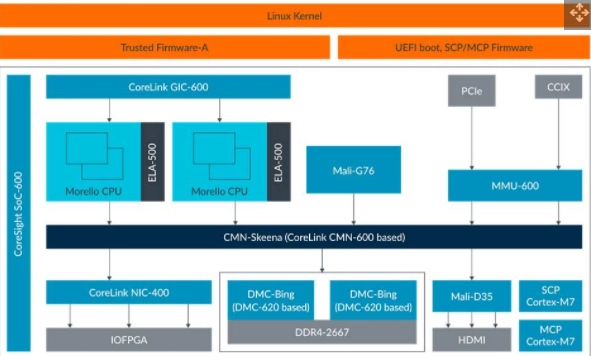

基于 Arm Neoverse N1的SoC

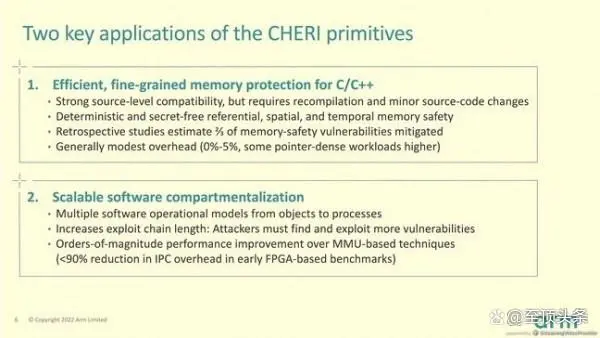

Arm 今天的一篇博客文章深入探讨了 Morello 技术演示器背后的技术。据透露,原型架构是Armv8.2a 64位的扩展。由于 CHERI,这种经过调整的架构提供细粒度的内存保护和高度可扩展的软件划分。

Morello 的 SoC 基于基于 TMSC N7 的 Arm Neoverse N1 双集群四核设计。 Arm 表示,CHERI按期实现,并且在优化功率和性能方面还需要做更多的工作,但很高兴里程碑式的硬件能够运行在 2.5GHz的SoC中,并且可以进行演示。许多 Neoverse 的新功能,如 SCP(系统控制处理器)、MCP(可管理性控制处理器)、Mali GPU、Mali DPU 等。

Morello SBC 配备 DDR DRAM 和 PCIe 等基本要素,以及 Arm 的 ULINK-Plus 调试适配器,可进行最彻底的测试。

Arm 的Morello 原型板是 Morello 计划的一个重要里程碑,软件开发人员和安全研究人员将在未来两年内检查 SoC 和板的功能,并协作提供有关其质量的反馈。如果一切顺利并按计划进行,Morello 计划将催生新的 Arm SoC 系列,为未来的设备形成基本的安全设计。

二、什么是CHERI

CHERI的全称,是Capability Hardware Enhanced RISC Instructions,即对能力的硬件增强RISC指令,属于英国剑桥大学与美国SRI International的合作研究项目。而Morello则是Arm将CHERI与Arm v8.2-A架构相融合所设计出的处理器原型方案。

CHERI和Arm Morello的意义,在于调整现有处理器架构以提高系统安全性,尽可能消除内存访问所引发的各类漏洞。

Arm公司在今年1月发布了用于测试的Morello评估系统板,甚至还搭配一套能够在该硬件上运行的CheriBSD(基于FreeBSD)操作系统。

CHERI和Arm Morello的意义,在于调整现有处理器架构以提高系统安全性,尽可能消除内存访问所引发的各类漏洞。

根据Arm公司执行副总裁、首席架构师兼研究员Richard Grisenthwaite的介绍,目前上报的相当一部分漏洞源自缓冲区溢出或使用后释放等内存安全错误,而且这些漏洞在不同计算生态系统中往往有着广泛的“兼容性”。虽然以往业界普遍将其视为软件问题,但CHERI还是希望能从硬件出发部分加以解决。

Grisenthwaite表示,“人们已经愈发意识到,随着网络犯罪带来的损失成本日益高企,可信、可靠的安全技术方案正变得越来越重要。”

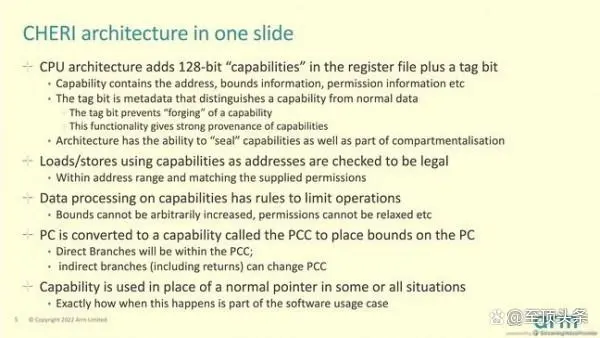

为此,Morello引入了“能力”(capabilities)这一概念,其操作类似于指针及其他数据访问寄存器。而且除地址之外,这些能力还负责存储权限和边界信息,硬件则可以使用这些信息来检查特定内存空间是否允许执行相应的代码操作。

其实能力这个概念在计算领域并不算新鲜事物,以往已经有不少大型机系统就采取过类似的机制。

Grisenthwaite解释道,“这些独立的128位单元被保存在一起,同时进一步为寄存器文件和内存系统添加元数据标签,用以将能力与数据区分开来。”这里的元数据标签非常重要,能够“帮助我们保证能力具备不可伪造的特性。”

这意味着元数据标签只能由内核或其他高权限进程所设置,攻击者只要尝试把能力当成数据来操作并更改其属性,都会导致该能力失去状态。而失去状态,也就意味着能力失效。

Grisenthwaite解释称,“最主要的变化,就是我们建立起一套完整的加载和存储体系,它们会从能力寄存器中获取自身基础地址并检查所生成的地址。这些地址通常可能会在能力范围内添加一个整数偏移量。”

对能力权限的检查会与常规内存管理检查一同进行,任何与能力检查相冲突的行为都将导致内存中止,其中止方式与转译后备缓冲器(TLB)中的内存管理故障相同。

根据Grisenthwaite的描述,Morello架构同样支持普通的加载和存储指令,这些指令会从传统的通用寄存器中获取地址。但Arm还添加了所谓默认数据能力的机制,能够为此类访问添加边界和权限,相当于为不具备能力感知的遗留代码创建起相应的沙箱。

与此同时,对能力的操作自然也需要新的数据处理指令。这些新的数据处理指令包含某些规则,允许用户在能力边界定义的范围之内执行地址调整。

Grisenthwaite还提到,“重要的是,一般来说无法在能力内添加边界。这些指令允许大家减少能力的边界或权限,通过原始对象创建子对象。但用户无法在能力不提供相应权限的前提下,扩大权限边界。”

该项目的目标之一就是调整程序计数器,将其转化为程序计数器能力,从而建立一组与之相关的边界。直接分支可以在边界之内实现分支,而间接分支则可以改变能力边界,从而在不同代码块之间实现调用。

Grisenthwaite提到,“在建立起这套功能体系之后,我们就可以用能力来全面替代以往保存在通用寄存器内的部分或全部地址,由此建立起更高的安全性基础。”

而使用这些新能力的方法之一,就是通过重新编译将程序代码中的几乎每个地址指针都替换为一项能力,这很可能需要对代码内容做出调整。根据Grisenthwaite的说法,这样能够带来更强大的内存安全性优势,通过元数据把能力跟数据区分开来,允许在C语言中释放内存时实现隔离和垃圾收集等方法。

但这套方案也有缺点,主要就是新能力会占用更大的缓存和内存。Morello原型系统中的Arm CPU内核经过定制和调整,只能支持包含一组能力的寄存器文件,而非标准的64位通用寄存器。实际上,这意味着全部寄存器都被扩展为129位,用以包含元数据标记、缓存和系统总线。

Grisenthwaite指出,在测试阶段,Arm会让所有32个CPU寄存器都可以保存数据或能力。但后续商业实施肯定会酌情削减能力寄存器的具体数量。

他解释道,“从本质上讲,已经有很多微架构扩展至129位能力,这会对整体数据路径设计产生很大影响。在Morello中,我们没有简单选择把内存中的所有数据路径宽度加倍,希望借此让处理器在性能与面积尺寸之间拥有合理的平衡点。但在生产系统中,一般会更多从性能的角度出发进行芯片设计。”

能力的存在还有助于进一步细化应用程序的划分粒度。目前的应用程序划分通常要依靠多进程来实现。

通过提供更细粒度的划分,即可限制单一漏洞利用可能造成的危害,在提高软件健壮性的同时增强系统的整体安全性。

而另外一个优势是,与传统的进程切换相比,CHERI架构还能够将把不同划分间的切换成本降低几个数量级。

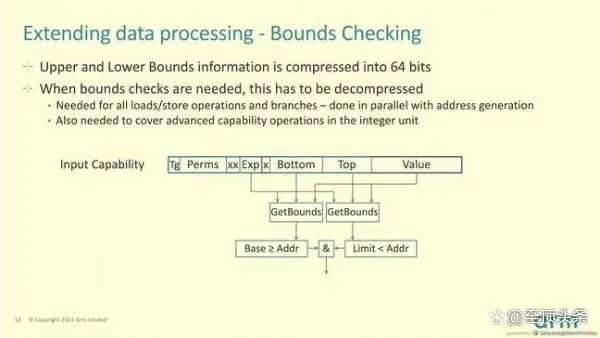

CHERI中还有一种非常有趣的实现方式,也就是把能力的边界和权限信息以压缩格式加以存储,因此只需要添加额外的64位状态信息。但这也意味着在执行地址检查时,基址和边界值需要经过解压,之后才能跟地址计算结果进行比较。

根据Grisenthwaite的介绍,他们在压缩方面投入了大量精力,希望提出一种随时能够快速解压的方案,以免影响设备上的其他关键部件。

“在内存访问路径当中,基址和边界的解压缩会作为地址生成算法的并行扩展同步完成。这意味着边界检查的耗时,与正常的TLB命中非常相似。”

至于对软件的影响,Grisenthwaite表示,CheriBSD中基于X11 KDE的桌面环境是由一位工程师耗时三个月移植到Morello的,全程只对全部600万行代码中的不到0.03%进行了更改。而小小的变化,让系统脆弱性和漏洞缓解率提升了约73.8%。

微软安全研究中心(MSRC)发布的一项详尽研究,也证实了Arm对于Morello的安全信心。研究中心调查了2019年影响微软产品并需要更新修复的所有内存安全漏洞,并得出结论称,配合其他处理措施,CHERI至少可以缓解其中三分之二的安全问题。

由于目前尚处于纯原型设计阶段,还不属于商业产品,因此Arm只制造了少量Morello系统板。在英国研究与创新(UKRI)组织的指导下,Arm开始将Morello交付给各家合作伙伴,包括谷歌、微软以及其他高校和企业。

但CHERI并没有申请技术专利,Arm也鼓励计算行业内的其他各方开展评估,同时将Morello作为技术展示架构。

Grisenthwaite总结道,“我们对这项技术的前景万分期待,也希望看到Morello将以怎样的方式开拓出这条大有可为的安全改善道路。”

参考链接:

https://baijiahao.baidu.com/s?id=1722545933581078352&wfr=spider&for=pc

https://baijiahao.baidu.com/s?id=1742500360236343307&wfr=spider&for=pc

这篇关于Arm的Morello SoC与CHERI架构的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!