本文主要是介绍8051单片机的CPU组成与四个并行I/O端口,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

AT89S51的CPU与并行I/O端口

本文主要涉及8051的CPU组成以及并行的4个I/O端口。CPU,主要由

运算器(ALU)和控制器(CU)构成;4个双向的8位并行I/O端口`,分别记为P0、P1、P2和P3

文章目录

- AT89S51的CPU与并行I/O端口

- 一、CPU的组成

- 1、 运算器(ALU - Arithmetic Logic Unit)

- 1.1 算术逻辑运算单元ALU

- 1.2 累加器A

- 3.程序状态字寄存器PSW

- 2、 控制器(CU - Control Unit)

- 二、 并行I/O端口

- 2.1、 P0口

- 2.2、P1口

- 2.3、P2口

- 2.4、P3口

一、CPU的组成

AT89S51是一种由Intel(现在的Microchip Technology)推出的8位单片机,它的核心是Intel 8051架构。下面简要介绍AT89S51的CPU部分,主要由运算器(ALU)和控制器(CU)构成。

1、 运算器(ALU - Arithmetic Logic Unit)

功能: 对操作数进行算术、逻辑和位操作运算。

组成: 算术逻辑运算单元ALU、累加器A、位处理器、程序状态字寄存器PSW及两个暂存器等。

1.1 算术逻辑运算单元ALU

可对8位变量逻辑运算(与、或、异或、循环、求补和清零),还可算术运算(加、减、乘、除)

ALU还有位操作功能,对位变量进行位处理,如置“1”、清“0”、求补、测试转移及逻辑“与”、“或”等。

1.2 累加器A

累加器A是CPU中使用最频繁的一个8位寄存器,在使用汇编语言编程时,有些场合必须写为Acc。

作用如下:

(1)ALU单元的输入数据源之一,又是ALU运算结果存放单元

(2)数据传送大多都通过累加器A,相当于数据的中转站。为解决“瓶颈堵塞”问题,AT89S51增加了一部分可以不经过累加器的传送指令。

A的进位标志Cy是特殊的,因为它同时又是位处理机的位累加器.

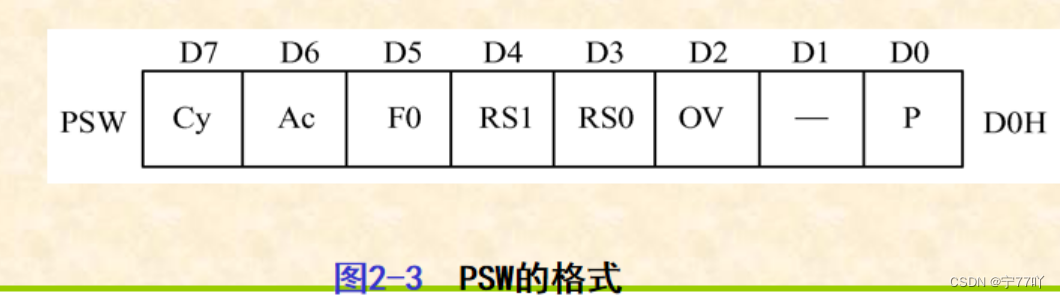

3.程序状态字寄存器PSW

PSW(Program Status Word)位于片内特殊功能寄存器区,字节地址为D0H。

包含了程序运行状态的信息,其中4位保存当前指令执行后的状态,供程序查询和判断.

PSW中各个位的功能:

(1)Cy(PSW.7)进位标志位

可写为C。在算术和逻辑运算时,若有进位/借位,Cy=1;否则,Cy=0。在位处理器中,它是位累加器。

(2)Ac(PSW.6)辅助进位标志位

在BCD码运算时,用作十进位调整。即当D3位向D4位产生进位或借位时,Ac=1;否则,Ac=0。

(3)F0(PSW.5)用户设定标志位

由用户使用的一个状态标志位,可用指令来使它置“1”或清“0,控制程序的流向。用户应充分利用。

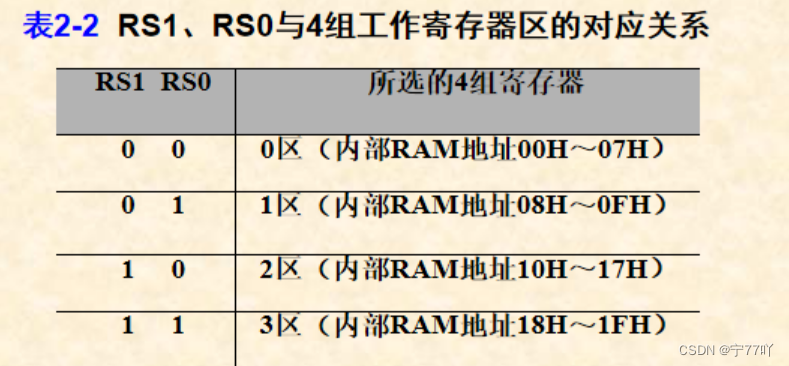

(4)RS1、RS0(PSW.4、PSW.3)4组工作寄存器区选择

选择片内RAM区中的4组工作寄存器区中的某一组为当前工作寄存区。如表2-2。

(5)OV(PSW.2)溢出标志位

当执行算术指令时,用来指示运算结果是否产生溢出。

如果结果产生溢出,OV=1;否则,OV=0。

(6)PSW.1位 保留位

(7)P(PSW.0)奇偶标志位

指令执行完,累加器A中“1”的个数是奇数还是偶数。

P=1,表示A中“1”的个数为奇数。

P=0,表示A中“1”的个数为偶数。

此标志位对串行通信有重要的意义,常用奇偶检验的方法来检验数据串行传输的可靠性。

2、 控制器(CU - Control Unit)

任务识别指令,并根据指令的性质控制单片机各功能部件,从而保证单片机各部分能自动协调地工作。

控制器包括:程序计数器、指令寄存器、指令译码器、定时及控制逻辑电路等。

功能是控制指令的读入、译码和执行,从而对各功能部件进行定时和逻辑控制。

程序计数器PC是一个独立的16位计数器,不可访问。单片机复位时,PC中的内容为0000H,从程序存储器0000H单元取指令,开始执行程序。

PC工作过程是:CPU读指令时,PC的内容作为所取指令的地址,程序存储器按此地址输出指令字节,同时PC自动加1。

PC中内容变化轨迹决定程序流程。

当顺序执行程序时自动加1;

执行转移程序或子程序、中断子程序调用时,自动将其内容更改成所要转移的目的地址。

PC的计数宽度决定了程序存储器的地址范围。PC为16位,故可对64KB(=2^16B)寻址。

二、 并行I/O端口

4个双向的8位并行I/O端口,分别记为P0、P1、P2和P3,其中输出锁存器属于特殊功能寄存器。端口的每一位均由输出锁存器、输出驱动器和输入缓冲器组成,4个端口按字节输入/输出外,也可位寻址。

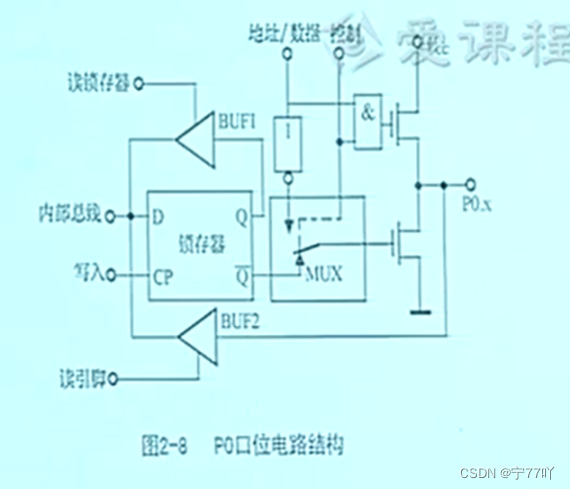

2.1、 P0口

P0口字节地址为80H,位地址为80H~87H。

P0口可作为双功能口:在外扩程序存储器、数据存储器(或外扩I/O)情况下,只能作为系统的低8位地址/数据总线端口来使用,否则可作为通用I/O端口使用。

P0口具有如下特点。

(1)当P0口用作地址/数据复用口时,是一个真正的双向口,用作与外部存储器的连接,输出低8位地址和输出/输入8位数据。

(2)当P0口用作通用I/O口时,由于需在片外接上拉电阻,端口不存在高阻抗(悬浮)状态,因此是一准双向口。为保证正确读入引脚信号,应首先向锁存器写1。单片机复位后,锁存器自动被置1;当P0口由原来的输出状态转变为输入状态时,应首先向锁存器写1,方可执行输入操作。

一般情况下,P0口大多作为地址/数据复用口使用,这时就不能再作为通用I/O口使用。

2.2、P1口

单功能的I/O口,字节地址为90H,位地址为90H~97H。

特点如下。

(1)P1口由于有内部上拉电阻,没有高阻抗输入状态,故为准双向口。作为输出口时,不需要在片外接上拉电阻。

(2)P1口“读引脚”输入时,必须先向P1口锁存器先写入1。

2.3、P2口

是一个双功能口,字节地址为A0H,位地址为A0H~A7H。在片外扩有存储器或I/O的情况下,P2口大多作为高8位地址总线口使用,这时就不能再作为通用I/O口。

特点如下:

(1)作为地址输出线使用时,P2口可输出外部存储器的高8位地址,与P0口输出的低8位一起构成16位地址,可寻址64KB的地址空间。当P2口作为高8位地址输出口时,输出锁存器的内容保持不变。

(2)作通用I/O口使用时,P2口为准双向口,功能与P1口一样

2.4、P3口

由于AT89S51的引脚数目有限,因此在P3口电路中增加了引脚的第二功能。P3口的第二功能定义如表2-7

P3口的每一位都可定义为第二输入功能或第二输出功能。

P3口的字节地址为B0H,位地址为B0H~B7H。

P3口的特点如下:

(1)P3口内部有上拉电阻,不存在高阻抗输入状态,为准双向口。

(2)P3口作为第二功能的输出/输入,或第一功能通用输入,需要先将相应位的锁存器置1。

实际应用中,由于复位后P3口锁存器自动置1,满足第二功能所需的条件,所以不需要任何设置工作,就可以进入第二功能操作。

当某位不作为第二功能使用时,可作为第一功能通用I/O使用。

这篇关于8051单片机的CPU组成与四个并行I/O端口的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!