本文主要是介绍第七届集创赛海云捷讯杯教程(一),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 海云捷讯杯教程

- 设计任务

- 整体教程

- 解析DVP时序获取帧图像,然后进行图像预处理

- 使用模型和CNN加速器进行推理

- 叠加推理结果到图像上

- 将叠加后的视频流转换为HDMI时序,并进行外观瑕疵质检

- 设计任务补充

- 对AI框架进行深度优化

- 设计PL端CNN加速器

海云捷讯杯教程

设计任务

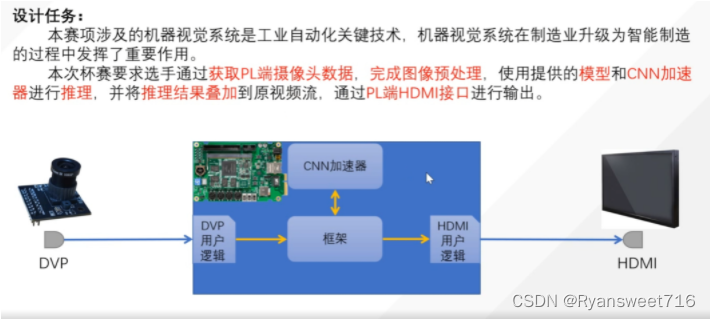

要求选手通过获取PL端摄像头数据,完成图像预处理,使用提供的模型和CNN加速器进行推理,并将推理结果叠加到原视频流,通过PL端HDMI接口进行输出,最终通过HDMI输出刷新帧率和推理结果刷新速度来进行评分。

整体教程

- 准备工具和硬件:

- Cyclone V FPGA板

- 虚拟摄像头(如vcam)

- HDMI显示器

- 电源线和数据线

- 环境搭建:

- 安装Quartus Prime Lite Edition以进行FPGA编程

- 安装ModelSim用于仿真

- 安装OpenCV库以进行图像处理

- 下载或获取所需的CNN模型及加速器

- 硬件设计:

- 使用Quartus Prime Lite Edition设计一个硬件模块,包括以下组件:

- 摄像头数据接口模块(用于获取PL端摄像头数据)

- 图像预处理模块(实现图像预处理功能)

- CNN加速器接口模块(与提供的CNN加速器进行通信)

- HDMI输出接口模块(用于输出视频流)

- 验证设计是否能成功编译且不含错误和警告

- 使用Quartus Prime Lite Edition设计一个硬件模块,包括以下组件:

- 图像预处理:

- 使用OpenCV库对摄像头数据进行预处理,包括以下步骤:

- 图像缩放和裁剪,使其符合CNN模型的输入要求

- 色彩空间转换,例如将RGB转换为灰度图

- 数据归一化,将像素值映射到特定的范围(如0-1)

- 任何其他必要的预处理步骤

- 使用OpenCV库对摄像头数据进行预处理,包括以下步骤:

- 使用CNN进行推理:

- 将预处理后的图像数据输入到提供的CNN模型和加速器中

- 获取推理结果,并将其与原视频流叠加

- HDMI输出:

- 使用HDMI输出接口模块,将叠加后的视频流通过PL端HDMI接口输出到显示器

- 记录HDMI输出刷新帧率和推理结果刷新速度,以便进行评分

- 仿真和测试:

- 使用ModelSim对硬件设计进行仿真,确保其功能正确

- 在实际硬件上进行测试,确保Cyclone V FPGA板能够正确处理摄像头数据,并通过HDMI接口输出叠加后的视频流

- 根据HDMI输出刷新帧率和推理结果刷新速度评估系统性能

- 优化:

- 如果需要,对硬件设计和图像处理算法进行优化,以提高帧率和推理速度

解析DVP时序获取帧图像,然后进行图像预处理

- DVP摄像头接口简介: DVP摄像头使用并行接口传输图像数据。主要信号包括:

- PCLK(像素时钟):用于同步数据传输

- HREF(水平参考):指示水平有效数据

- VSYNC(垂直同步):指示新帧的开始

- DATA(图像数据线):并行传输的图像数据

- 解析DVP时序: 首先,您需要设计一个FPGA模块来解析DVP摄像头的时序信号。以下是实现步骤:

- 通过PCLK对摄像头数据进行采样

- 当检测到VSYNC信号为高电平时,表示新帧的开始。重置行计数器和列计数器

- 当检测到HREF信号为高电平时,表示当前行的数据有效。将并行数据线上的数据存储到内存中,并递增列计数器

- 在HREF为低电平期间,递增行计数器

- 存储帧图像:

- 将解析后的图像数据存储在FPGA板上的内存(如BRAM或DDR)中

- 存储时需要注意行和列的顺序,确保图像数据的正确性

- 图像预处理: 使用OpenCV或自定义硬件模块进行图像预处理。以下是一些建议的预处理步骤:

- 图像缩放和裁剪:将图像缩放到CNN模型要求的输入尺寸

- 色彩空间转换:将RGB图像转换为灰度图(如果模型需要)

- 数据归一化:将图像数据归一化到特定范围(如0-1)

- 其他可能的预处理步骤,例如图像增强

- 将预处理后的图像数据传输给CNN模型进行推理

以下是一个简单的DVP时序解析模块伪代码:

module dvp_parser (input PCLK,input HREF,input VSYNC,input [7:0] DATA,output reg [7:0] image_data,output reg [15:0] row,output reg [15:0] col,output reg frame_valid

);integer row_counter, col_counter;

reg new_frame;always @(posedge PCLK) beginif (VSYNC) beginrow_counter <= 0;col_counter <= 0;new_frame <= 1;end else beginif (HREF) beginimage_data <= DATA;col_counter <= col_counter + 1;end else beginrow_counter <= row_counter + 1;col_counter <= 0;endend

使用模型和CNN加速器进行推理

- 准备工作:

- 确保您已经完成了图像预处理步骤,得到了适用于CNN模型输入的图像数据

- 准备好您的CNN模型和加速器。这可能是一个预训练的模型,或者您自己训练的模型。确保了解模型的输入和输出要求

- 将模型部署到Cyclone V FPGA:

- 使用适当的工具,如OpenCL或高级C语言,将CNN模型转换为适用于Cyclone V FPGA的硬件描述

- 使用Intel Quartus Prime工具将转换后的模型编译,并生成适用于Cyclone V FPGA的配置文件(.sof)

- 将生成的配置文件下载到FPGA板上,并确保与CNN加速器相连

- 创建推理模块:

- 在FPGA设计中,创建一个用于推理的模块,该模块可以将预处理后的图像数据发送给CNN加速器,并接收推理结果

- 该模块应具有以下功能:

- 将预处理后的图像数据加载到CNN加速器的输入缓冲区

- 控制CNN加速器的启动和停止

- 从CNN加速器的输出缓冲区中读取推理结果

- 将推理结果发送到下一个处理阶段(例如,将结果叠加到原始视频流上)

- 编写软件代码:

- 使用C或C++编写软件代码,以控制FPGA上的CNN推理模块

- 该代码应具有以下功能:

- 通过FPGA接口发送预处理后的图像数据

- 启动和停止CNN推理过程

- 从FPGA接口读取推理结果

- 使用Intel SoC EDS工具链(例如ARM DS-5)编译软件代码,并生成可执行文件

- 在Cyclone V SoC上运行软件:

- 将可执行文件下载到Cyclone V SoC的ARM处理器上

- 运行可执行文件,观察推理结果,并确保系统按预期运行

叠加推理结果到图像上

-

创建叠加模块: 在FPGA设计中,创建一个用于将推理结果叠加到图像上的模块。该模块应具有以下功能:

- 接收原始视频流和推理结果

- 将推理结果(例如边界框、类别标签等)绘制到原始视频流上

- 输出叠加后的视频流,以便通过HDMI显示或其他输出接口显示

-

绘制推理结果: 根据推理结果的类型(例如目标检测、分割或分类),采用不同的绘制方法。以下是一些常见的绘制方法:

- 目标检测:在原始图像上绘制边界框,标明检测到的目标,并在边界框附近显示类别标签和置信度

- 分割:将分割结果(通常为每个像素的类别标签)覆盖到原始图像上,以不同颜色表示不同类别

- 分类:在原始图像的某个位置(例如图像顶部)显示分类结果和置信度

在硬件设计中,可以使用专门的图形绘制模块(例如,基于BRAM的画笔),也可以在软件中实现此功能,例如使用OpenCV库。

-

输出叠加后的视频流: 将叠加后的视频流输出到HDMI显示器或其他输出接口,以便查看效果。这可能需要一个HDMI驱动模块或其他视频输出模块。

-

测试和验证: 在实际硬件上进行测试,确保推理结果正确叠加到原始视频流上,并能够通过输出接口显示。

以下是一个简单的伪代码,用于将边界框叠加到原始图像上:

void draw_bbox(cv::Mat &image, vector<BBox> bboxes) {for (const auto &bbox : bboxes) {// 绘制边界框cv::rectangle(image, bbox.top_left, bbox.bottom_right, bbox.color, 2);// 显示类别标签和置信度std::string label = bbox.label + ": " + std::to_string(bbox.confidence);int base_line;cv::Size label_size = cv::getTextSize(label, cv::FONT_HERSHEY_SIMPLEX, 0.5, 1, &base_line);cv::putText(image, label, bbox.top_left, cv::FONT_HERSHEY_SIMPLEX, 0.5, bbox.color, 1);}

}

将叠加后的视频流转换为HDMI时序,并进行外观瑕疵质检

- 创建HDMI输出模块: 在Cyclone V FPGA设计中,创建一个HDMI输出模块,用于将叠加后的视频流发送到HDMI显示器。HDMI输出模块应具有以下功能:

- 将视频流转换为HDMI时序信号

- 通过HDMI接口发送HDMI时序信号

- 实现HDMI时序信号转换: 要将视频流转换为HDMI时序信号,需要实现以下步骤:

- 将视频流的像素数据以RGB格式传递给HDMI输出模块

- 将RGB像素数据转换为HDMI时序信号(TMDS时序)

- 在HDMI时序信号中添加同步信号(Hsync和Vsync),以及其他控制信号

- 将生成的HDMI时序信号发送到HDMI PHY(物理层)模块

- 实现外观瑕疵质检: 在FPGA设计中,创建一个用于外观瑕疵质检的模块。该模块可以利用边缘检测、轮廓检测等图像处理算法,在FPGA上实时检测产品的外观缺陷。具体实现步骤如下:

- 从原始视频流中提取感兴趣区域(ROI),例如产品表面区域

- 在ROI中使用图像处理算法(如Sobel、Canny等)进行边缘检测

- 对检测到的边缘进行轮廓检测,识别潜在的缺陷区域

- 通过设置阈值和其他条件,筛选出真正的缺陷区域

- 将缺陷区域的坐标和其他信息发送给HDMI输出模块,以便在视频流上叠加显示

- 叠加缺陷检测结果: 将缺陷检测结果(例如缺陷区域的边界框)叠加到原始视频流上,以便通过HDMI显示器查看。具体实现步骤如下:

- 在HDMI输出模块中接收缺陷检测结果

- 在原始视频流上绘制缺陷区域的边界框或其他标记

- 将叠加后的视频流发送到HDMI显示器

- 测试和验证: 在实际硬件上进行测试,确保HDMI输出和外观瑕疵质检功能正常工作。请注意,这里的教程是通用性的,您可能需要根据具体的FPGA平台、HDMI接口和外观瑕疵质检需求进行适当调整。

- 性能优化: 在实际应用中,您可能需要优化外观瑕疵质检的性能,以满足实时性和准确性要求。可以考虑以下方法进行优化:

- 优化图像处理算法,以减少计算复杂度和资源占用

- 在FPGA设计中使用并行处理技术,以提高处理速度

- 调整参数和阈值,以提高缺陷检测的准确性和鲁棒性

- 集成和部署: 完成上述步骤后,将整个系统集成到Cyclone V FPGA上,并进行部署。具体步骤如下:

- 将HDMI输出模块、外观瑕疵质检模块等集成到Cyclone V FPGA设计中

- 使用Intel Quartus Prime工具对FPGA设计进行综合、布局和布线

- 将生成的配置文件(.sof)下载到Cyclone V FPGA板上

- 连接HDMI显示器和摄像头,运行整个系统,观察实时视频流上的外观瑕疵检测结果

设计任务补充

使用带框架的FPGA AI加速器,虽然比较便利,但是会消耗一定的时间来处理框架开销,会降低加速器性能,影响视频流输出显示的帧率。

因此鼓励选手对AI框架进行深度优化,从而更高效的利用CNN加速器。同时鼓励选手自行设计PL端CNN加速器,以获得更高的帧率输出。

对AI框架进行深度优化

- 网络模型压缩: 对神经网络模型进行压缩,可以有效减少计算量和模型大小,提高运行速度。常见的模型压缩方法包括:

- 权重量化:将模型权重量化为较低精度(例如8位或16位),以减少计算量和存储需求

- 网络剪枝:移除模型中的冗余参数或层,降低模型复杂度

- 知识蒸馏:使用较大的模型指导较小模型的训练,以提高较小模型的性能

- 网络模型加速: 对神经网络模型进行加速,可以提高计算性能。常见的网络加速方法包括:

- 模型融合:将多个相邻层(例如卷积层和激活层)融合成一个操作,减少运算次数

- Winograd卷积:使用Winograd算法替代常规卷积,降低计算量

- 分组卷积:将通道分组进行卷积,减少计算量

- 优化AI框架: 对AI框架进行优化,可以减少框架开销,提高加速器性能。具体方法包括:

- 优化内存管理:减少内存分配和释放的次数,降低内存碎片

- 优化计算图:优化计算图的结构和执行顺序,减少中间结果的存储和传输

- 多线程和任务并行:利用多线程和任务并行提高计算性能,充分利用硬件资源

- 自定义CNN加速器: 设计自定义的PL端CNN加速器,可以充分利用FPGA的并行计算能力,提高帧率输出。设计自定义加速器时,请考虑以下因素:

- 并行计算:利用FPGA的并行计算能力,设计高度并行化的加速器结构

- 资源优化:根据FPGA资源(例如LUT、DSP、BRAM等)进行加速器设计,以充分利用资源

- 管道化:设计高效的数据流水线,减少计算延迟

- 集成和部署: 将优化后的AI框架和自定义CNN加速器集成到FPGA设计中,并进行部署。具体步骤如下:

- 将优化后的AI框架和自定义CNN加速器集成到FPGA设计中

- 使用Intel Quartus Prime工具对FPGA设计进行综合、布局和布线

- 将生成的配置文件(.sof)下载到Cyclone V FPGA板上

- 验证整个系统的性能,确保优化后的AI框架和自定义CNN加速器能够满足性能要求

- 性能测试和优化: 在实际硬件上进行测试,确保优化后的AI框架和自定义CNN加速器能够满足性能要求。如果性能不符合预期,可以进一步调整优化方法:

- 分析性能瓶颈:通过性能分析工具找出系统的瓶颈,例如计算、内存、带宽等

- 调整优化策略:根据性能分析结果,调整优化方法,例如增加/减少模型压缩程度、调整并行计算策略等

- 重新部署和测试:将调整后的优化方法应用到AI框架和CNN加速器上,重新部署和测试性能

设计PL端CNN加速器

- 了解CNN的基本结构: 在设计CNN加速器之前,需要了解CNN的基本结构,例如卷积层、激活层、池化层和全连接层等。了解这些层的工作原理和计算过程,有助于设计高效的加速器。

- 确定加速器架构: 根据CNN的结构和计算特点,确定加速器的架构。典型的加速器架构包括数据流式架构、脉动阵列和卷积处理单元(Convolutional Processing Unit, CPU)等。选择适合您应用的架构,以实现最佳性能。

- 并行计算与管道化设计: 充分利用FPGA的并行计算能力,设计高度并行化的加速器结构。同时,根据加速器架构,实现数据和任务的流水线处理,以降低计算延迟。

- 优化内存访问: CNN加速器的性能通常受限于内存访问。设计高效的内存访问策略,例如缓存、局部缓冲区和数据重用等,以降低内存访问延迟和带宽需求。

- 权重压缩与量化: 对模型权重进行压缩和量化,可以降低计算量和存储需求。设计加速器时,应考虑支持压缩和量化后的权重格式,以实现高效的计算。

- 动态调度与负载均衡: 根据不同层的计算需求,设计动态调度和负载均衡策略,以充分利用硬件资源。例如,为不同层分配可配置的计算资源,或者动态调整计算资源的分配。

- 模型部署与运行时优化: 针对部署到加速器的模型,实现运行时优化,例如模型融合、计算图优化和多线程执行等。这可以进一步提高加速器的性能。

- 集成与部署: 将设计好的CNN加速器集成到FPGA设计中,并进行部署。具体步骤如下:

- 使用Intel Quartus Prime工具对FPGA设计进行综合、布局和布线

- 将生成的配置文件(.sof)下载到Cyclone V FPGA板上

- 测试与验证: 在实际硬件上进行测试,确保CNN加速器可以正常工作,并满足性能要求。如果性能不符合预期,可以进一步调整优化方法。

- 分析性能瓶颈: 通过性能分析工具找出系统的瓶颈,例如计算、内存、带宽等。定位问题后,针对性地进行优化。

- 调整优化策略: 根据性能分析结果,调整优化方法,例如增加/减少模型压缩程度、调整并行计算策略、优化内存访问策略等。

- 重新部署和测试: 将调整后的优化方法应用到CNN加速器上,重新部署和测试性能。持续迭代优化,直到达到期望的帧率输出。

这篇关于第七届集创赛海云捷讯杯教程(一)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!