本文主要是介绍【学习笔记】单片机结构与原理(MCS-51为例),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

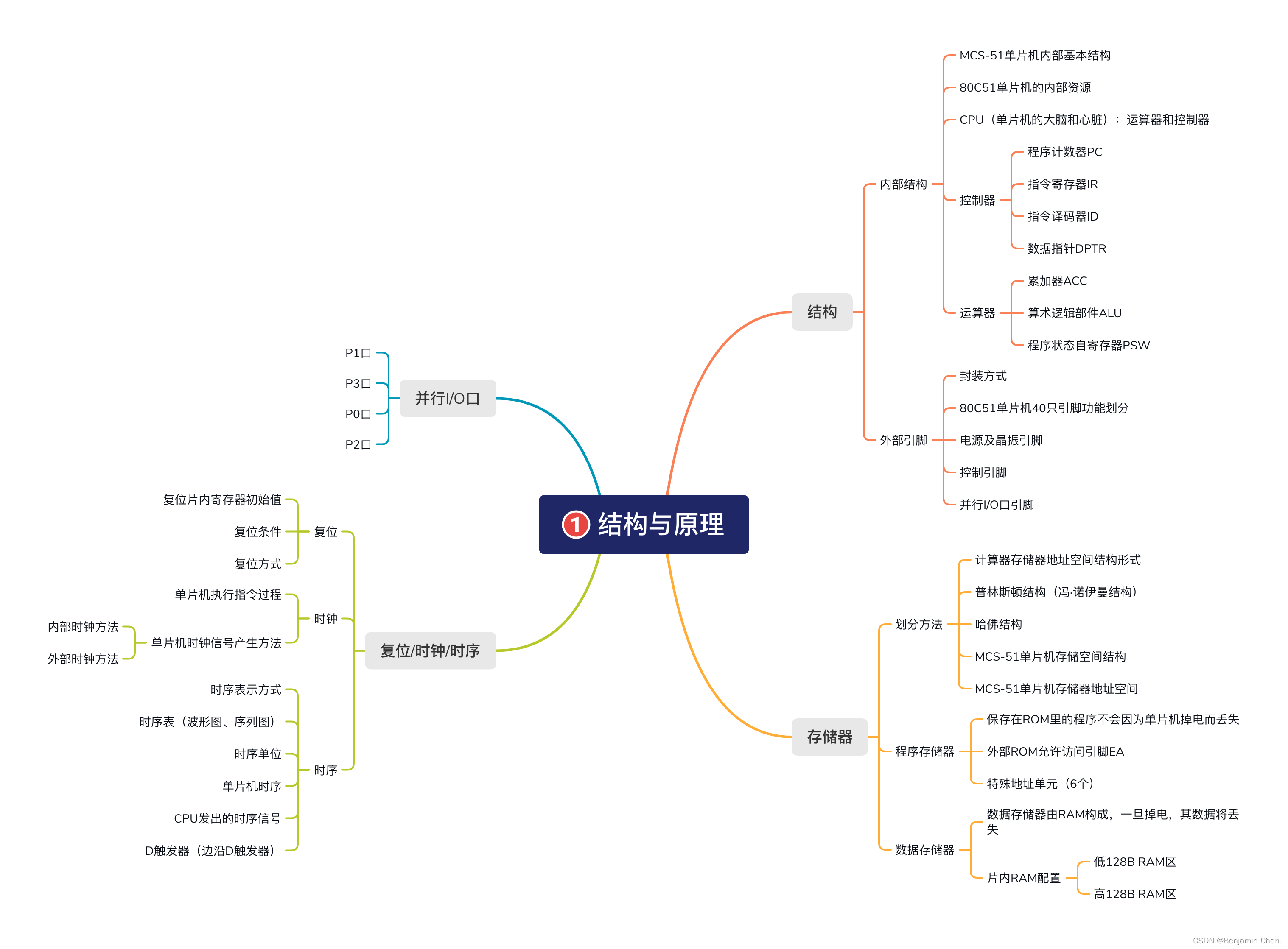

单片机结构与原理(MCS-51为例)

基础知识

概述

- 什么是单片机

- 单片机(Single-Chip-Microcomputer)又称为单片微计算机

- 结构特点:将微型计算机的基本功能部件全部集成在一个半导体芯片上

- 单片机的特点

- 集成度高,体积小,抗干扰能力强,可靠性高

- 开发性能好,开发周期短,控制功能强

- 低功耗,低电压,具有掉电保护功能

- 通用性和灵活性好

- 具有良好的性能价格比

- 单片机的应用领域

- 工业自动化控制

- 智能仪器仪表

- 通信设备

- 汽车电子与航空航天电子系统

- 家用电器

- 单片机发展趋势

- 高集成度

- 高性能

- 低功耗

- 高性价比

预备知识

-

数制及其变换

- 数制:十进制D、二进制B、十六进制H

- 进制转换:BH转D(加权展开)、B转H(4位对应)、D转BH(除基取余)

-

有符号数表示方法

- 原码:0正1负,其余数值

- 反码:正数(与原码相同)、负数(符号位不变,数值位取反)

- 补码:正数(与原码相同)、负数(符号位不变,数值位取反,末位加1)

- 负数补码 = 模 - 绝对值差值

- 补码的补码为原码

-

位、字节、字

- 位(bit):0和1

- 字节(Byte):1Byte = 8bit

- 字(Word):计算机一次存取、加工和传送的数据长度

-

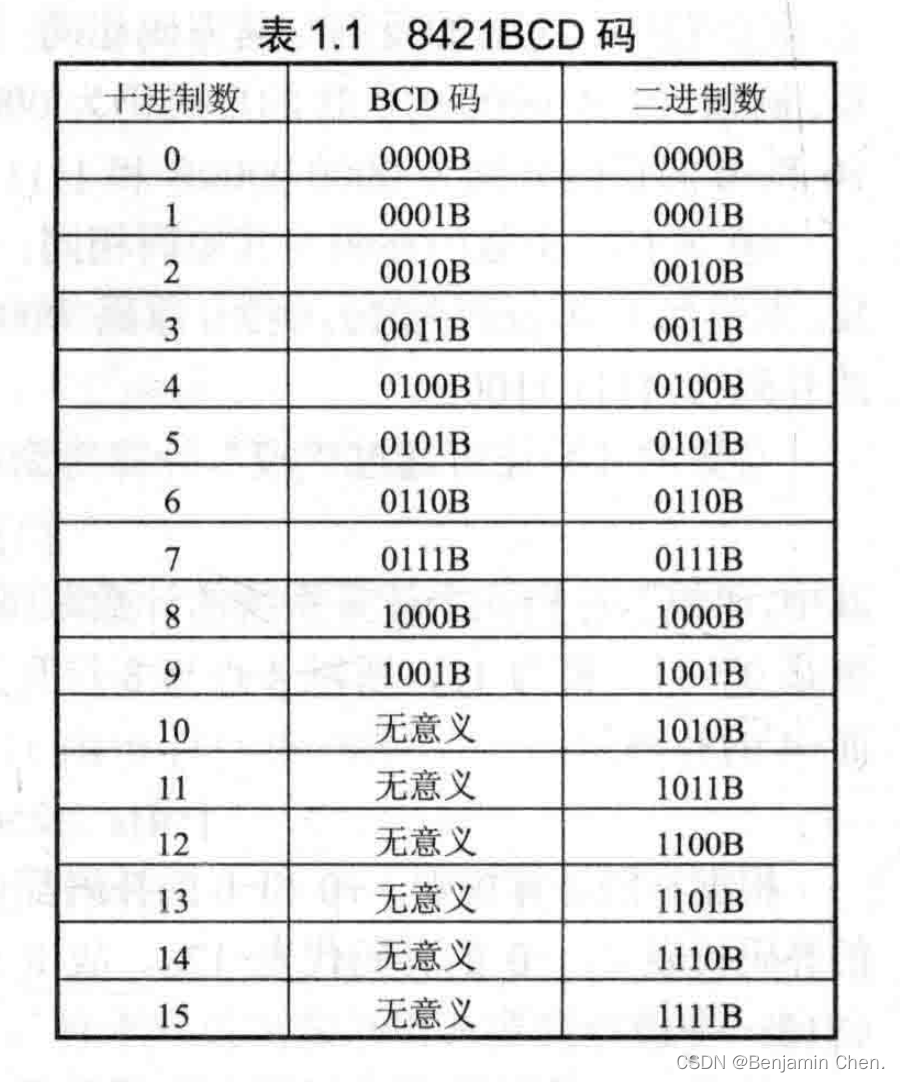

BCD码

-

以二进制数表示十进制数

-

8421BCD码

-

压缩BCD码:1字节表示2个十进制数

-

非压缩BCD码:1字节只表示1个十进制数

-

-

ASCII码

- 采用7位二进制编码表示128个字符

- 采用7位二进制编码表示128个字符

-

基本逻辑门电路

- 与门、或门、非门、异或门、与非门、或非门

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-bmMJxl6J-1651216399446)(/Users/jermy/Library/Application Support/typora-user-images/截屏2022-04-28 14.11.44.png)]](https://img-blog.csdnimg.cn/d7e80d460a7d489dacf205aee390ac99.png)

![**[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-nRmNAaA9-1651216399448)(/Users/jermy/Library/Application Support/typora-user-images/截屏2022-04-28 14.12.03.png)]**](https://img-blog.csdnimg.cn/108883daa12d40fcb5f2c9aa926287d9.png)

- 与门、或门、非门、异或门、与非门、或非门

结构与原理

结构

-

内部结构

-

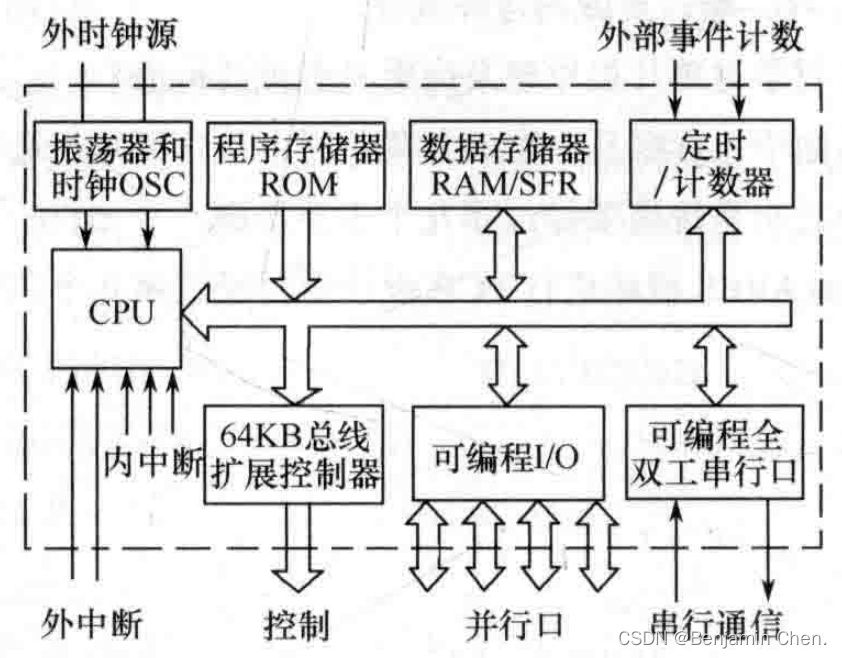

MCS-51单片机内部基本结构

-

80C51单片机的内部资源

- 1个8位中央处理器(CPU)

- 1个片内振荡器和时钟电路

- 4KB片内程序存储器(ROM)

- 256字节的片内RAM

- 2个16位定时/计数器

- 可寻址64KB外部程序存储器和64KB数据存储空间控制电路

- 4个8位双向I/O口

- 1个全双工串行口

- 5个中断源

-

CPU(单片机的大脑和心脏):运算器和控制器

-

控制器:对取自程序存储器中的指令进行译码,在规定时间发出各种操作所需的控制信号,完成指令所规定的功能。

- 程序计数器PC:存放下一条要执行指令的首地址(决定程序的运动轨迹)

- 指令寄存器IR:暂存待执行的指令,等待译码

- 指令译码器ID:对指令进行译码,转变为执行指令所需电信号

- 数据指针DPTR:DPH(高8位)和DPL(低8位)

- 定时控制与条件转移逻辑电路

-

运算器

-

累加器ACC(CPU工作中使用最频繁的寄存器):存放一个操作数或中间结果

-

算术逻辑部件ALU:对数据进行四则运算和逻辑运算

-

程序状态字寄存器PSW:存放程序运行过程中的各种状态信息

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-1umCF0Rb-1651216399449)(/Users/jermy/Library/Application Support/typora-user-images/截屏2022-04-28 14.30.14.png)]](https://img-blog.csdnimg.cn/67df50ae98e340a0880684f8fe95b984.png)

- 进位标志CY(PSW7):位累加器

- 辅助进位标志AC(PSW6)

- 用户标志位F0(PSW5)

- 工作寄存器组指针RS1、RS0(PSW4、PSW3):选择CPU当前工作的寄存器组

- 溢出标志OV(PSW2):指示是否发生益处,由硬件自动形成

- 用户标志位F1(PSW1)

- 奇偶标志位P(PSW0):跟踪累加器A中含“1”个数的奇偶性

-

运算调整电路

-

-

-

外部引脚

- 封装方式

- HMOS制造工艺:40只引脚的双列直插封装(DIP)

- CHMOS制造工艺:44只引脚方形封装方式(其中4只是无用的)

- 80C51单片机40只引脚功能划分

- 电源及晶振引脚(4只)

- 控制引脚(4只)

- 并行I/O口引脚(32只)

- 电源及晶振引脚

- 电源引脚:VCC(+5V电源引脚)、VSS(接地引脚)

- 外接晶振引脚:XTAL1、XTAL2

- 控制引脚

- RST/VPD(复用/备用电源引脚)

- ALE/PROG(地址锁存使能输出/编程脉冲输入)

- PSEN(输出访问片外程序存储器读选通信号)

- EA/VPP(外部ROM允许访问/编程电源输入)

- 并行I/O口引脚

- P0口(P0.0~P0.7)

- P1口(P1.0~P1.7)

- P2口(P2.0~P2.7)

- P3口(P3.0~P3.7)

- 封装方式

存储器

- 划分方法

-

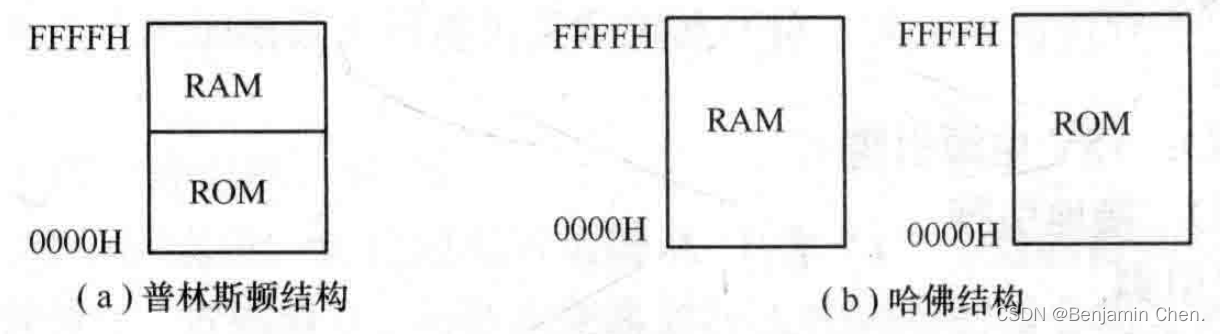

计算器存储器地址空间结构形式:普林斯顿结构(冯·诺伊曼结构)、哈佛结构

-

普林斯顿结构(冯·诺伊曼结构)

- 将程序指令存储器和数据存储器合并在一起(ROM和RAM位于统一存储空间的不同物理位置处)

- CPU可以使用相同指令访问ROM和RAM

-

哈佛结构

- 将程序指令存储器和数据存储器分开设置(ROM和RAM位于不同存储空间)

- ROM和RAM中的存储单元可以有相同的地址

- CPU需要采用不同的访问指令加以区别

-

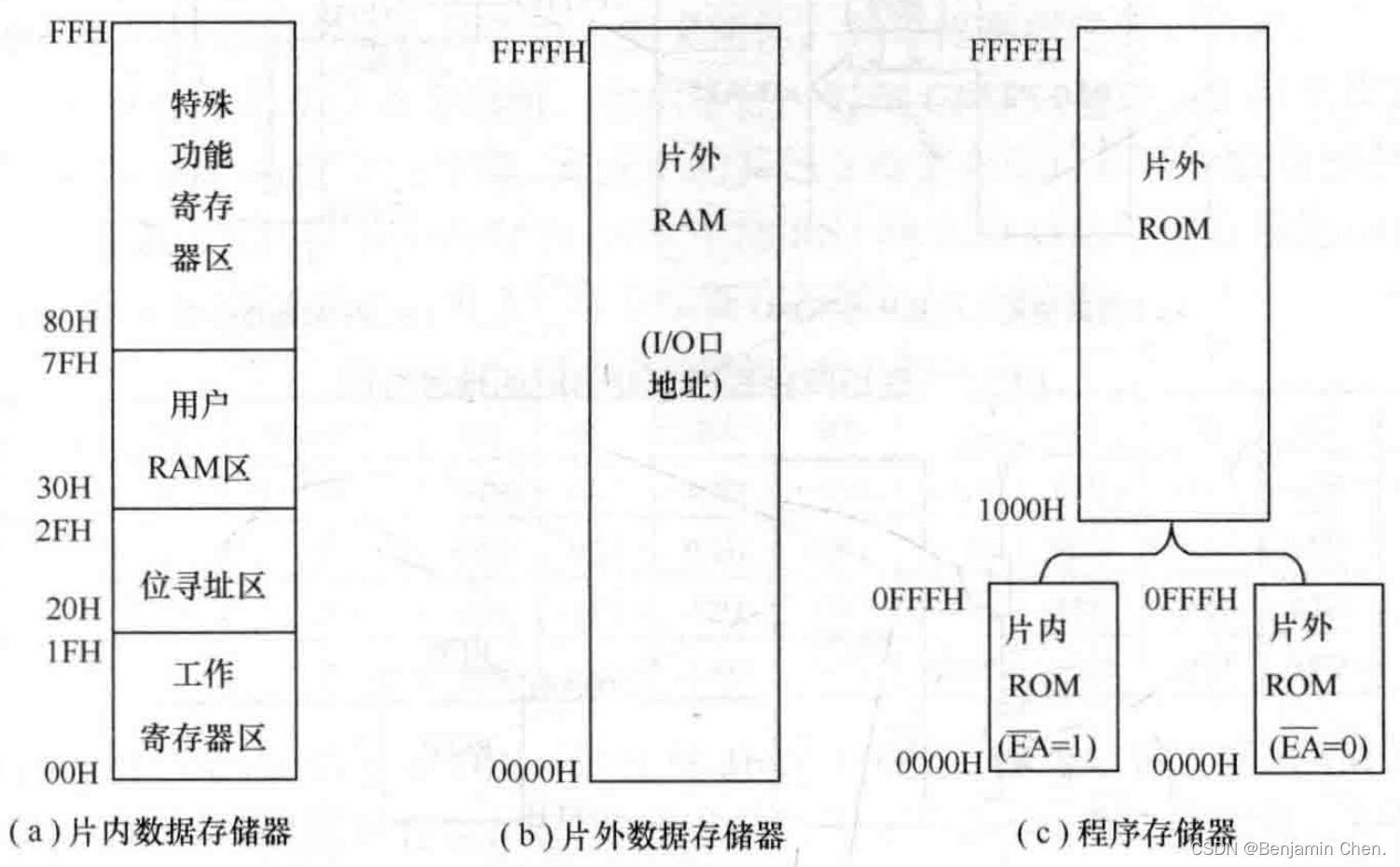

MCS-51单片机存储空间结构

- 物理地址(4个):片内程序存储器(片内ROM)、片外程序存储器(片外ROM)、片内数据存储器(片内RAM)、片外数据存储器(片外RAM)

- 逻辑地址(3个):程序存储器、片内数据存储器、片外数据存储器

-

MCS-51单片机存储器地址空间

- 片内ROM地址空间:0000H~0FFFH(4KB)

- 片外ROM地址空间:0000H~FFFFH(64KB)

- 片内RAM地址空间:00H~FFH(256B)

- 片外RAM地址空间:0000H~FFFFH(64KB)

-

- 程序存储器(存放程序代码及程序中用到的常数)

- 保存在ROM里的程序不会因为单片机掉电而丢失

- 外部ROM允许访问引脚EA

- EA引脚接高电平:片内ROM(小于等于4KB地址)和片外ROM(大于4KB地址)共同构成64KB空间

- EA引脚接低电平:片内ROM被禁用,全部64KB地址都在片外ROM中

- 特殊地址单元(6个):专门为复位和中断功能设计

- 0000H(程序首地址):单片机复位后程序从首地址开始运行

- 0003H(外部中断0入口地址)

- 000BH(定时器0益处中断入口地址)

- 0013H(外部中断1入口地址)

- 001BH(定时器1溢出中断入口地址)

- 0023H(串行口中断入口地址)

- 数据存储器(存放运算中间结果、标志位、待调试程序)

-

数据存储器由RAM构成,一旦掉电,其数据将丢失

-

数据存储器在物理上和逻辑上都占有两个地址空间:片内256B的RAM、片外64KB的RAM

-

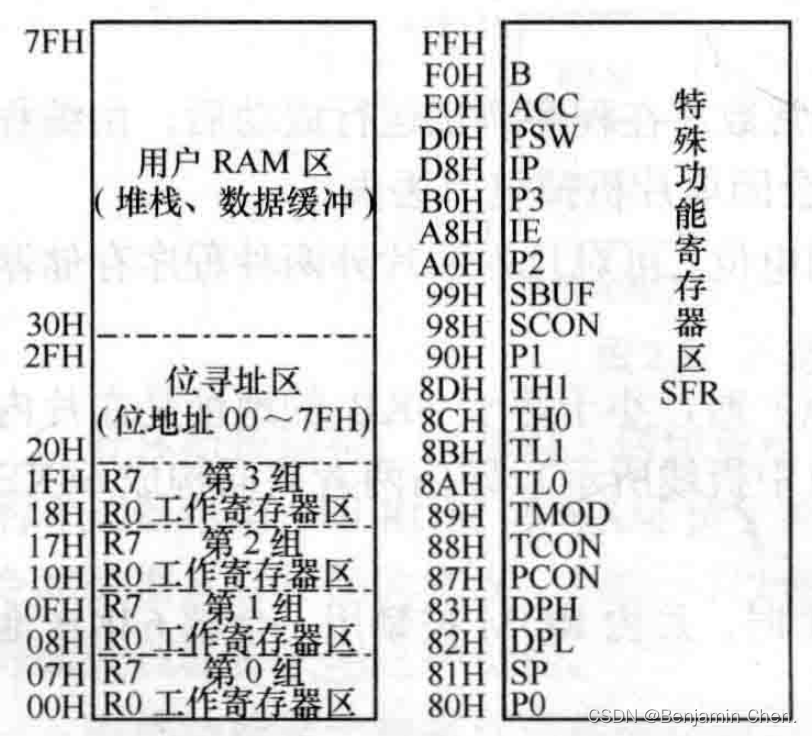

片内RAM配置:低128B RAM区、高128B RAM区

- 低128B RAM区

- 00H~1FH:作为工作寄存器使用(通用寄存器R0-R7)

- 20H~2FH:位寻址区

- 30H~7FH:用户可以设置堆栈区和存储中间数据

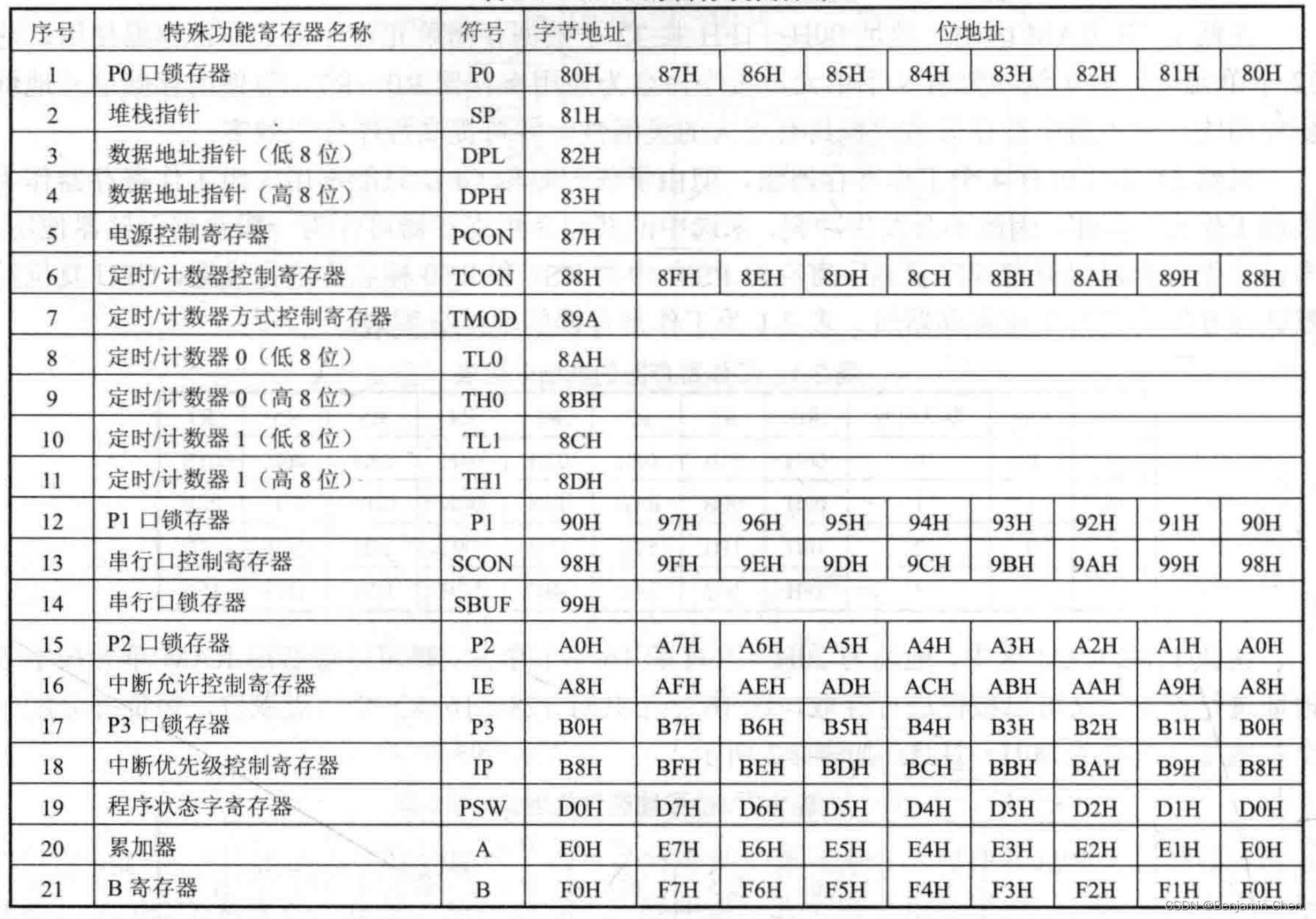

- 高128B RAM区:21个特殊功能寄存器

- 低128B RAM区

-

复位、时钟、时序

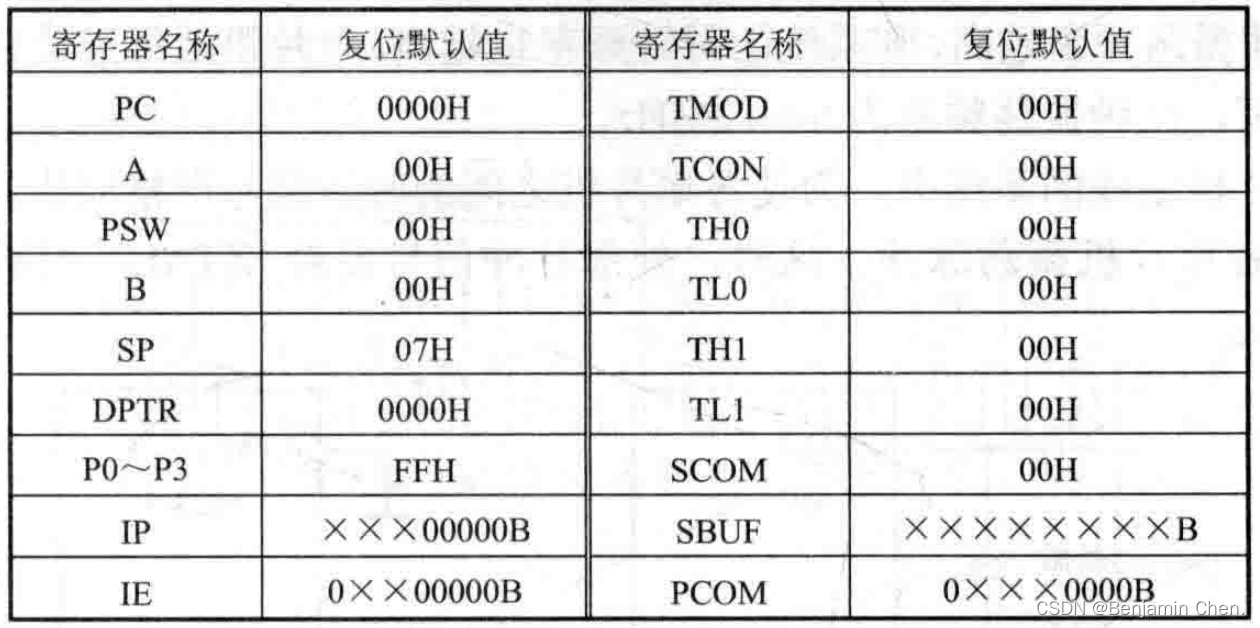

- 复位

-

复位片内寄存器初始值

-

复位条件

- 在RST引脚端出现满足复位要求的高电平状态

- 该时间等于系统时钟振荡周期建立时间再加2个机器周期时间(一般不小于10ms)

-

复位方式

- 上电复位:利用阻容充电电路实现

- 按键复位:利用电阻分压电路实现

- 复合复位

-

- 时钟

- 单片机执行指令过程:取指令、分析指令、执行指令

- 单片机时钟信号产生方法

- 内部时钟方法:利用单片机芯片内部的振荡电路实现

- 定时元件一般用晶体振荡器和电容组成并联谐振电路

- 晶体振荡频率越高,则系统的时钟频率也越高,单片机运行速度也就越快

- MCS-51时钟振荡频率为6~12MHz

- 外部时钟方法:采用公用外部脉冲信号作为各单片机振荡脉冲

- 内部时钟方法:利用单片机芯片内部的振荡电路实现

- 时序

-

时序:按照时间顺序显示的对象序列关系

-

时序表示方式:状态方程、状态图、状态表、时序表

-

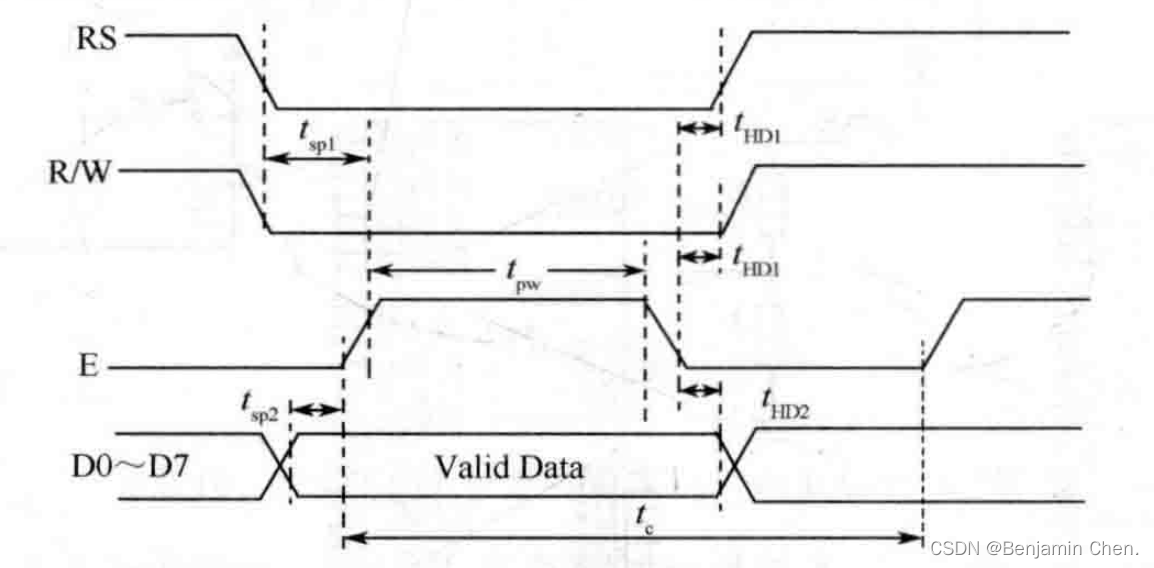

时序表(波形图、序列图)

- 从上到下查看对象间的交互关系

- 时间轴从左往右的方向为时间正向轴(时间在增长)

- 最左边是引脚的标识

- 交叉线部分标识电平的变化

- 封闭菱形部分标识数据有效范围

- 水平方向的尺寸线标识持续时间长度

-

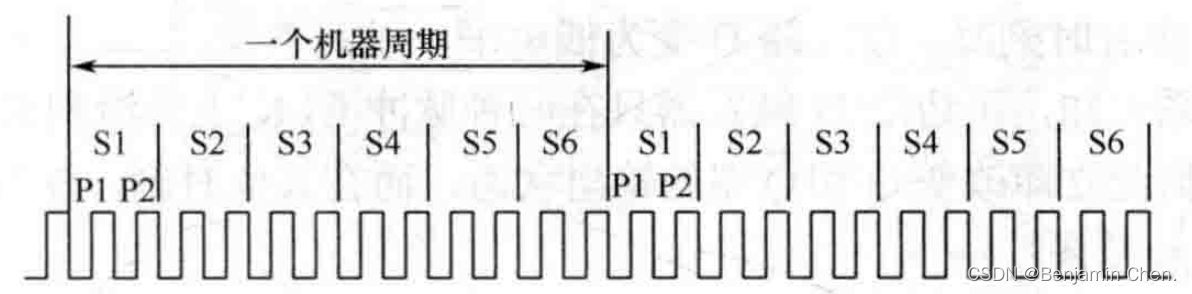

时序单位

- 时钟周期(节拍P):晶振或外加振荡源的振荡周期(最小时序单位)

- 状态周期(S):1个状态周期等于2个时钟周期

- 机器周期:1个机器周期等于6个状态周期(12个节拍)

- 指令周期:执行一条指令所需要的时间(1个指令周期由1~4个机器周期组成)

-

单片机时序:CPU在执行指令时所需控制信号的时间顺序

-

CPU发出的时序信号:用于片内个功能部件的控制、用于片外存储器或I/O端口的控制

-

D触发器(边沿D触发器)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-44rbiPgW-1651216399450)(/Users/jermy/Library/Application Support/typora-user-images/截屏2022-04-28 15.50.22.png)]](https://img-blog.csdnimg.cn/fc449c82ad064439a3987bdc9876d65b.png)

- 正边沿D触发器:只在CLK上升沿时刻采样D输入信号,改变Q输出状态

- 负边沿D触发器:只在CLK下降沿时刻采样D输入信号,改变Q输出状态

-

并行I/O口

-

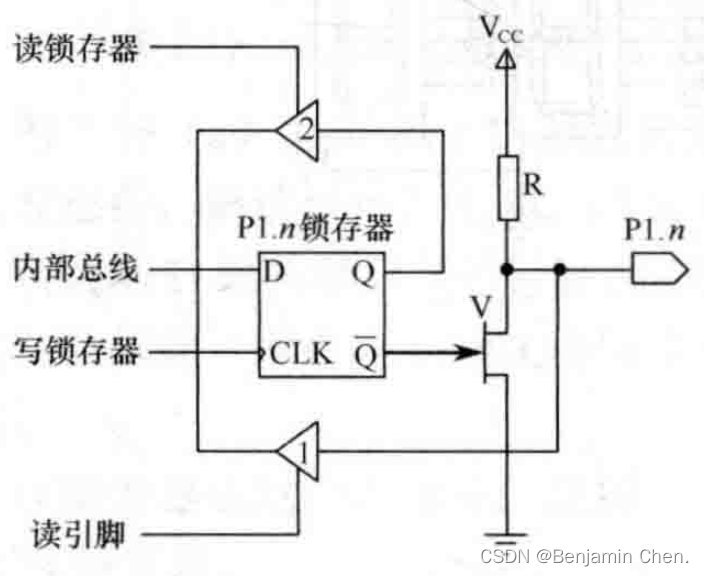

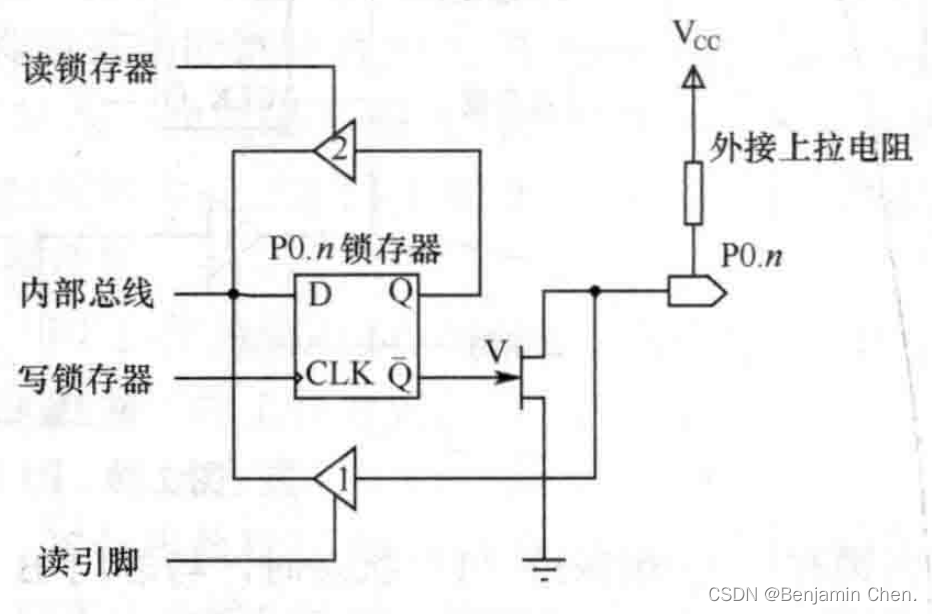

P1口(作为通用I/O口使用):字节地址90H

- 输出方式

- 读引脚方式(准双向口):必须先用输出指令置Q=1,使V截止

- 读锁存器方式:P1口已有内部上拉电阻,无需外接上拉电阻

-

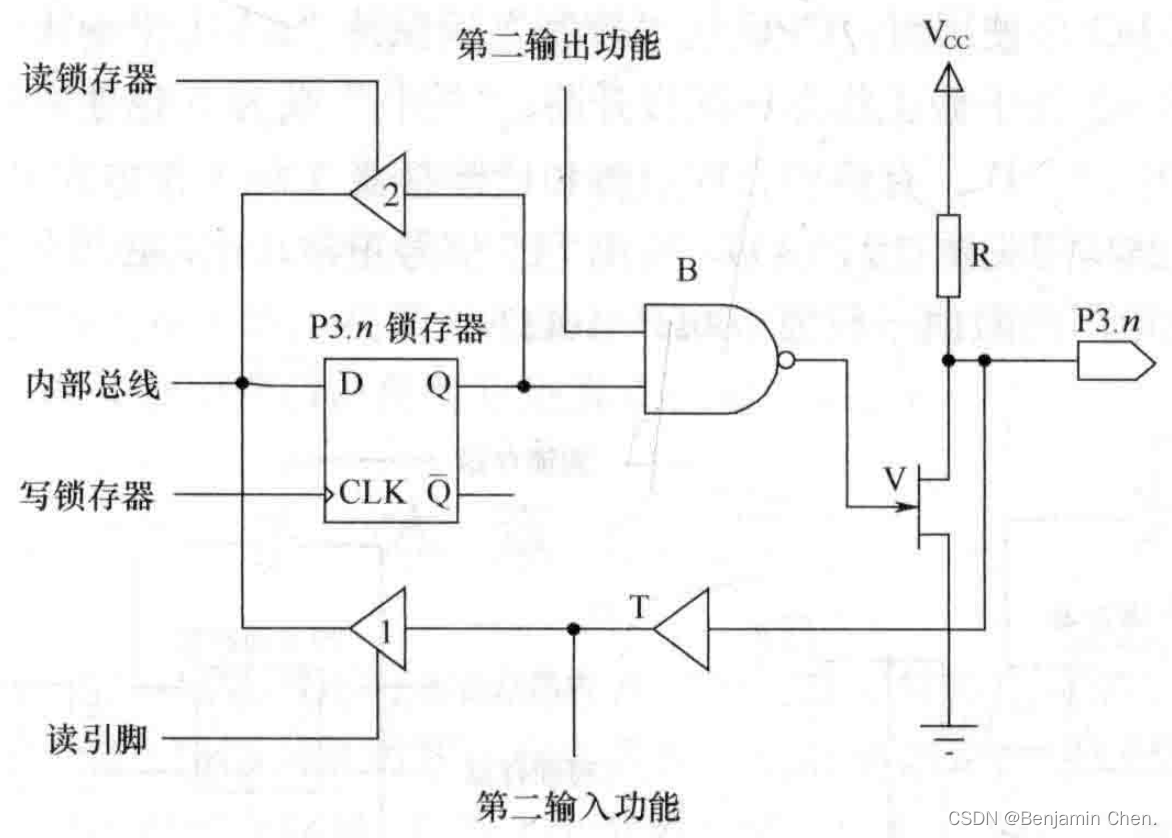

P3口:字节地址B0H

- 通用I/O功能(与P1口完全相同):当“第二输出功能”段保持“1”状态

- 第二功能口状态:当锁存器Q端保持“1”状态

-

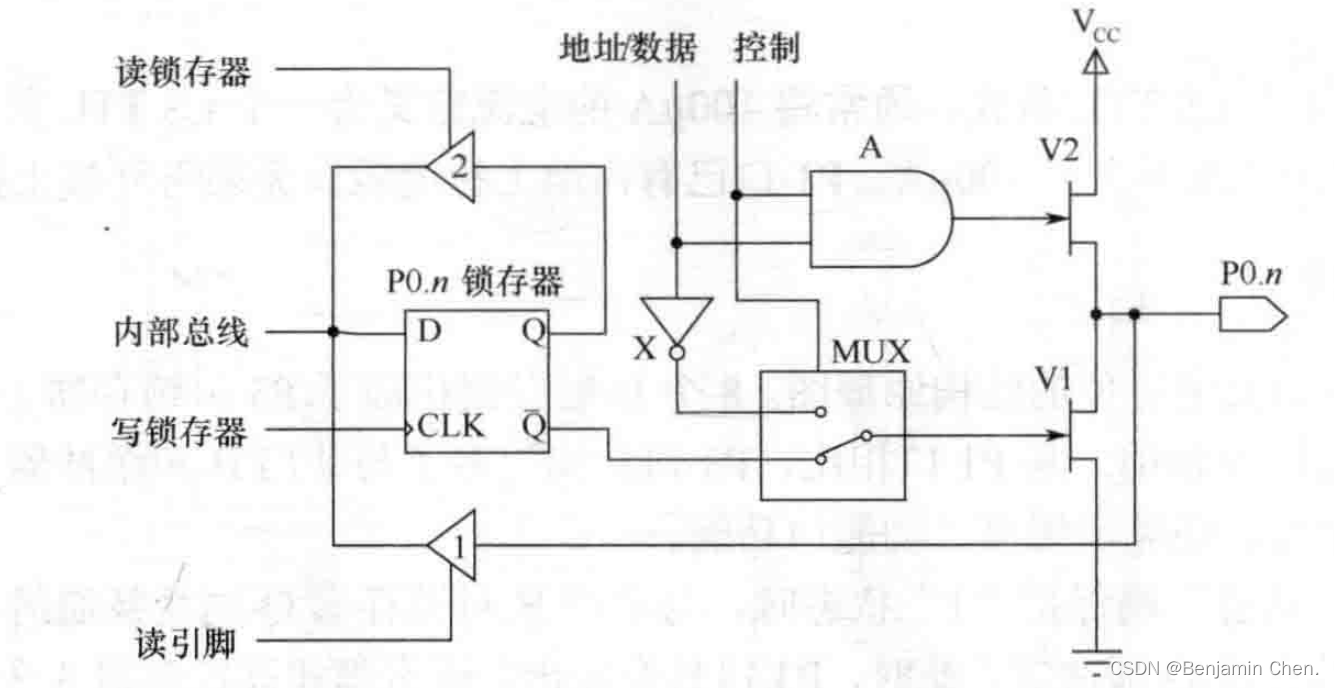

P0口字节地址80H

-

通用I/O口:要使“1”信号正常输出,必须外界一个上拉电阻(上拉电阻一般为100Ω~10kΩ)

-

单片机系统的地址/数据线(连接外部存储器):双向口

- 当需要输入外部数据时,CPU自动向P0.n的锁存器写“1”(保证引脚电平不会被误读)

- P0口在“地址/数据”方式下没有漏极开路问题(不必外接上拉电阻)

-

-

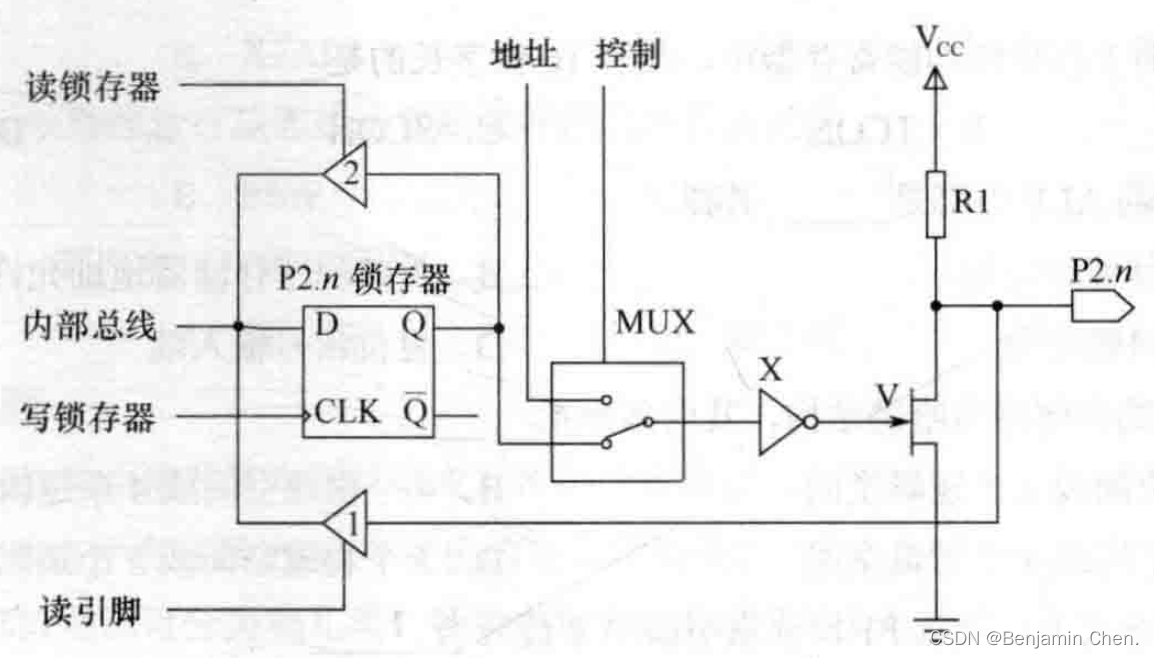

P2口:字节地址A0H

- 通用I/O口(准双向口):输出、读引脚、读锁存器

- 地址线接口

-

并行I/O口

- P0~P3口都可作为准双向通用I/O口提供给用户

- P1~P3口无需外接上拉电阻

- P0口需要外接上拉电阻

- 拓展片外存储器

- P2口作为地址线接口

- P0口作文地址线/数据线复用接口(双向口)

- P0~P3口都可作为准双向通用I/O口提供给用户

这篇关于【学习笔记】单片机结构与原理(MCS-51为例)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!