本文主要是介绍STM32单片机开发----GPIO(General-purpose Input Output)通用IO口,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、GPIO的相关配置寄存器

1.CRL端口配置低寄存器&CRH端口配置高寄存器(均为32位)

一组GPIO有16个GPIO口(例如GPIOA简称PA,有PA0-PA15这16个GPIO口)

一个GPIO口由4个bit位配置分别是MODE[1:0]和CNF[1:0],所以一组GPIO就需要4*16=64bit位去配置,这正好对应我们的CRL和CRH寄存器。PA0-PA7由CRL配置,PA8-PA15由CRH配置。

以PA0为例对应

MODE0[1:0] CNF0[1:0]

MODE[1:0]用于设置GPIO口的模式(输出/输入)

若MODE[1:0]=00,则为输入模式;MODE[1:0]>00,则为输出模式。

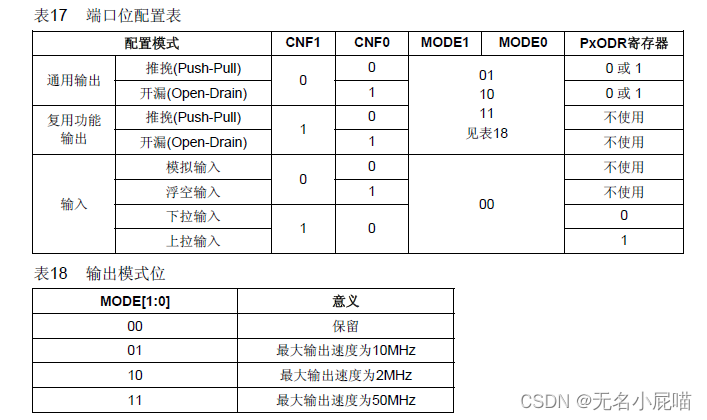

CNF[1:0]用于设置输出/输出的方式对应下表:

值得注意的是:在通用输出模式下,GPIO口输出的高低电平是由ODR寄存器设置;在输入模式下若使用上拉或者下拉输入模式也需要设置ODR寄存器,具体见上表。

2.IDR端口输入数据寄存器&ODR端口输出数据寄存器(均为32位,且16-31bit保留)

这两个寄存器都是每一个bit位控制该组GPIO中的一个GPIO口。

IDR[15:0]存放的是每个GPIO口的输入电平值。IDR为只读寄存器,且只能以字(16位)的形式读出。

ODR[15:0]设置对应GPIO口的输出电平。ODR为可读可写寄存器,且只能以字(16位)的形式读写。

3.BSRR端口位设置/清除寄存器(32位)&BRR端口位清除寄存器(16位)

BSRR[15:0]

每一个bit位用于设置对应的ODR寄存器对应位;

1:设置对应的ODR位为1;

0:对对应的ODR位不产生影响。

BSRR[16:31]

每一个bit位用于清除对应的ODR寄存器对应位;

1:清除对应的ODR位为0;

0:对对应的ODR位不产生影响。

BRR[15:0]

作用等同于BSRR[16:31]。

不难发现其实BSRR与BRR寄存器底层实现的都是对ODR寄存器的控制。在程序的书写时候,建议设置使用BSRR寄存器,清除使用BRR寄存器。

二、GPIO寄存器版本步骤

1.使能IO口时钟。配置RCC_APB2ENR寄存器;

2.初始化IO口模式。配置CRH/CRL寄存器;

3.操作IO口,输出高低电平。配置寄存器ODR/BSRR/BRR。

以简单的LED闪烁程序为例:

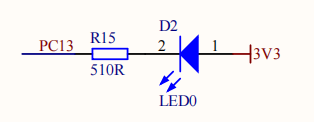

1.原理图:

2.程序:

#include "stm32f10x.h"

#include <stdio.h>void LED_Init()

{RCC->APB2ENR |= 1<<4;//GPIOC时钟使能GPIOC->CRH &= 0xFF0FFFFF;GPIOC->CRH |= 0X00300000;//配置CRH寄存器GPIOC->ODR |= 1<<13;

}

void delay_ms(u16 time)

{u16 i=0;while(time--){i=12000;while(i--);}

}

int main(void)

{LED_Init();while (1){ //通过配置BSRR和BRR寄存器控制ODR寄存器改变输出电平值GPIOC->BSRR |= 1<<13;//PC13=1delay_ms(500);GPIOC->BRR |= 1<<13;//PC13=0delay_ms(500);}

}

3.运行效果:

这篇关于STM32单片机开发----GPIO(General-purpose Input Output)通用IO口的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!