本文主要是介绍Signal Integrity: Crosstalk Delay 和 Crosstalk Noise-2,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

接上篇

东坡ju士,公众号:东坡ju士Signal Integrity: Crosstalk Delay 和 Crosstalk Noise-1

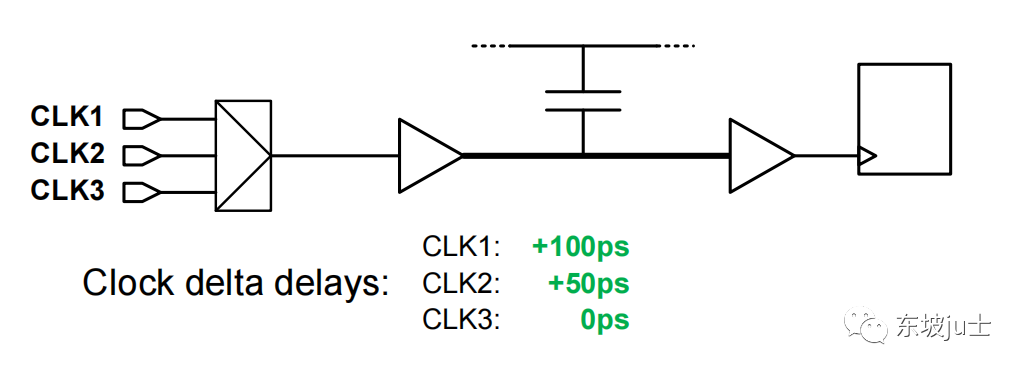

3,Multiple-Clock Domains Victim Nets 分析原则

对于在时钟网络上的nets,PTSI会分开计算每个时钟下的delta delay,也就是说在CLK1 domain 下时有delta delay,但在CLK3的时候就没有,这样不会过悲观。

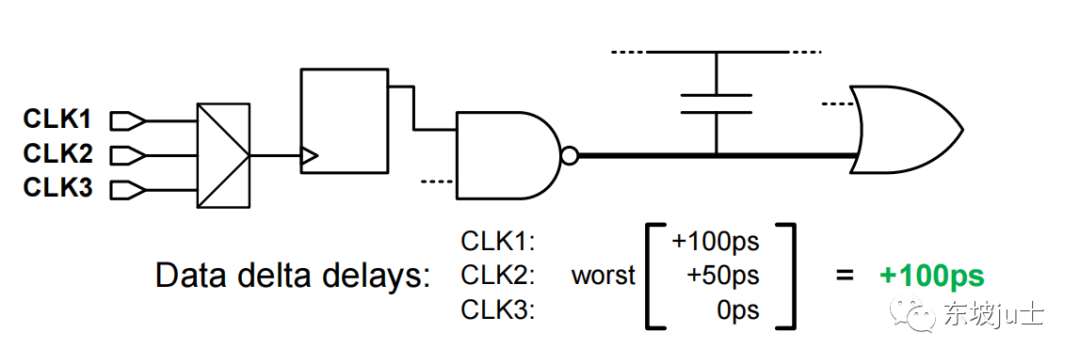

对于在数据网络上的nets,PTSI会在不同的clock domain下使用相同的最差的delta delay(默认none),如下图所示,这样做的优点就是更快节省空间,缺点就是比较悲观一点,也可以使用all_clocks,这样就会跟clock nets 一样分析,消除过悲观。

pt_shell> set_app_var \timing_enable_independent_crosstalk_in_data_network \none | all_clocks | physically_exclusive_clocks

如果使用 physically_exclusive_clocks,PTSI会把设置了physcially exclusive的两个分开计算。

4,All Paths 和All Path Edges

All Paths 和All Path Edges是 timing window overlap中的两种分析模式 set_app_var si_xtalk_delay_analysis_mode all_path & all_path_edges

all_path mode:

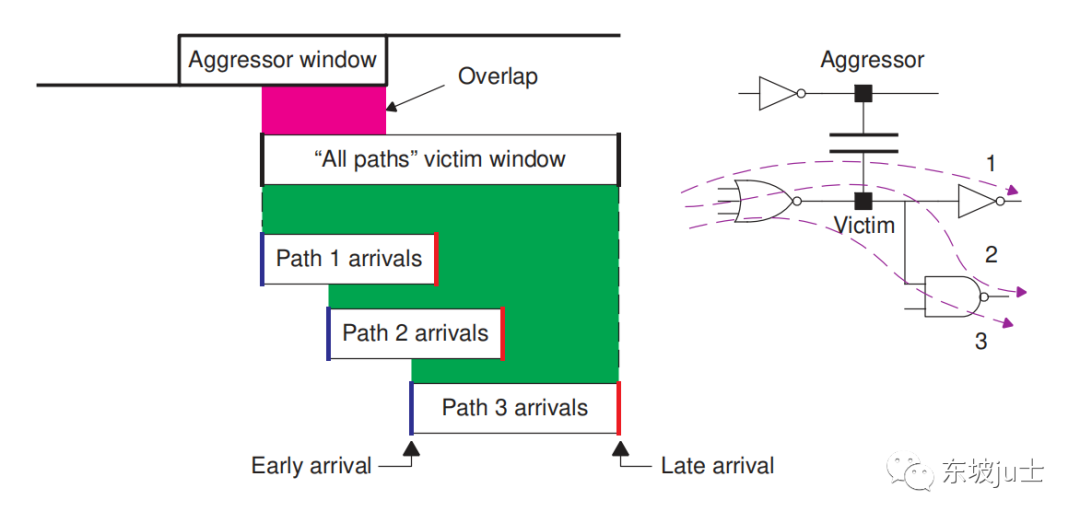

all_path 模式下,PTSI 会计算三条path的最早时间(对应计算hold)和最晚时间(对应计算setup)作为timing window 的范围,显然这种分析方法是有点过悲观的。如下图所示,红色部分是Aggressor window和victim window的overlap部分,工具计算delay 的时候就按照这部分 overlap来考虑他们之间的关系的,也就是说不管计算setup 还是hold,都是按照这个overlap来计算。但实际上在计算setup 的时候,3条path late arrival edgs是没有和 Aggressor window 有overlap 的,也就是说理论上计算setup 的时候不应该计算crosstalk的影响,但实际上计算了,就会产生一部分过悲观。这部分悲观度可以用两种方法去除,一种是pba,一种是下面说的all_path_edges mode。

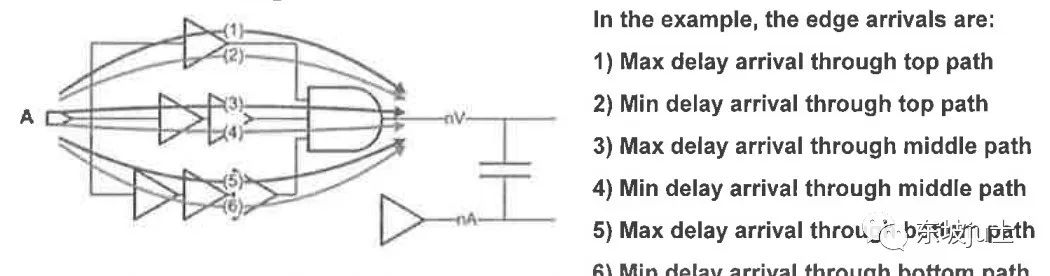

all_path_edges mode:

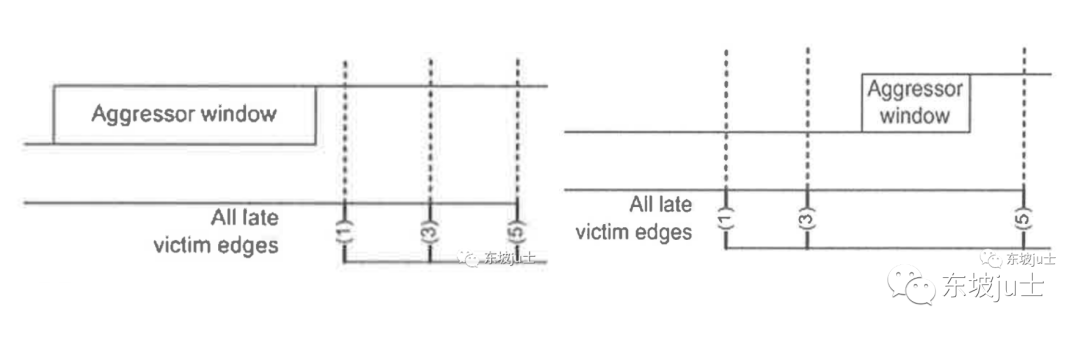

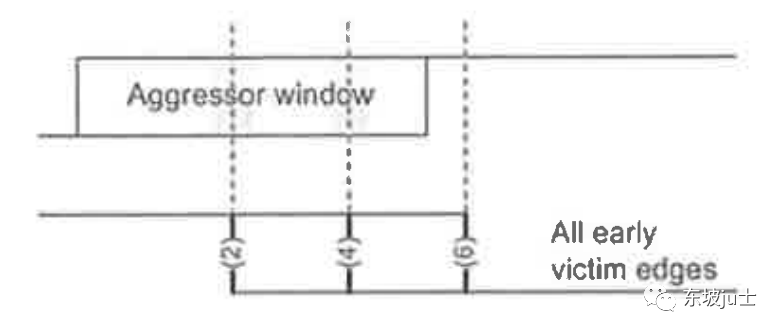

对max paths进行分析时,delay 计算应该按照1,3,5,此时1,3,5与aggressor window没有overlap,工具会计算delta delay 为0。

对min paths进行分析时,delay 计算应该按照2,4,6,有overlap ,工具计算delta delay 时就不为0。

一般都是使用较为悲观的all_path 分析模式,这样存储的数据量相对较小,计算更快,节省机器资源。一般项目后期会使用比较真实的pba或者all_path_edges mode来signoff。

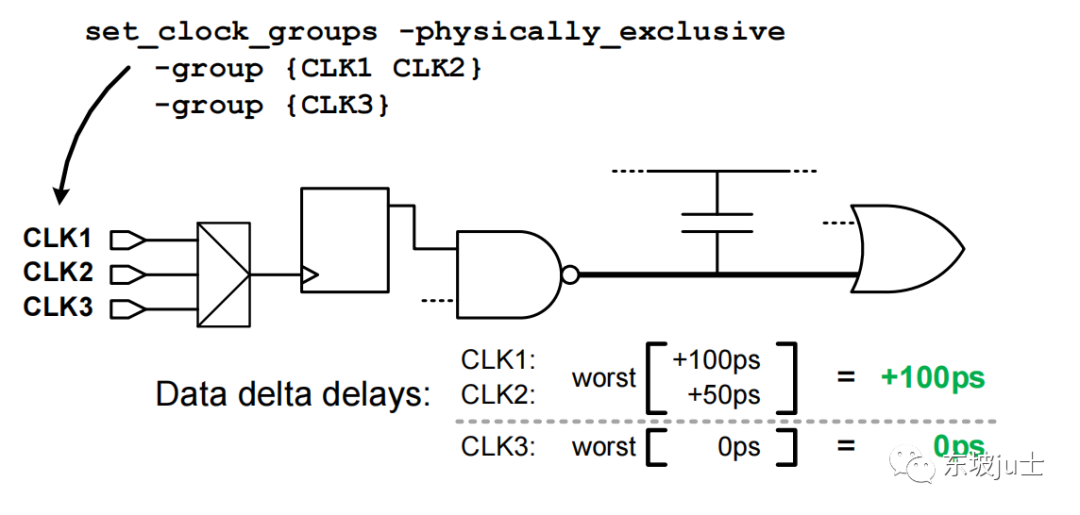

5,在不同clock group之间的crosstalk分析:

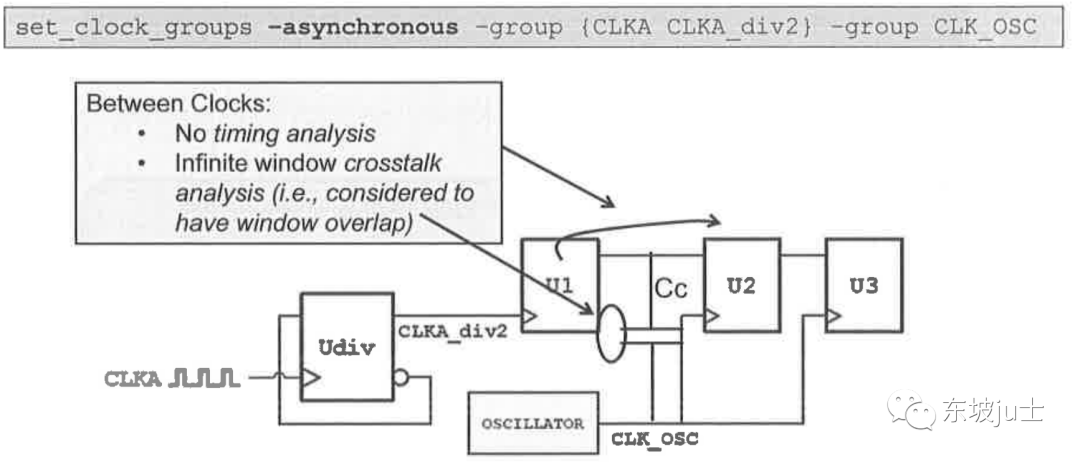

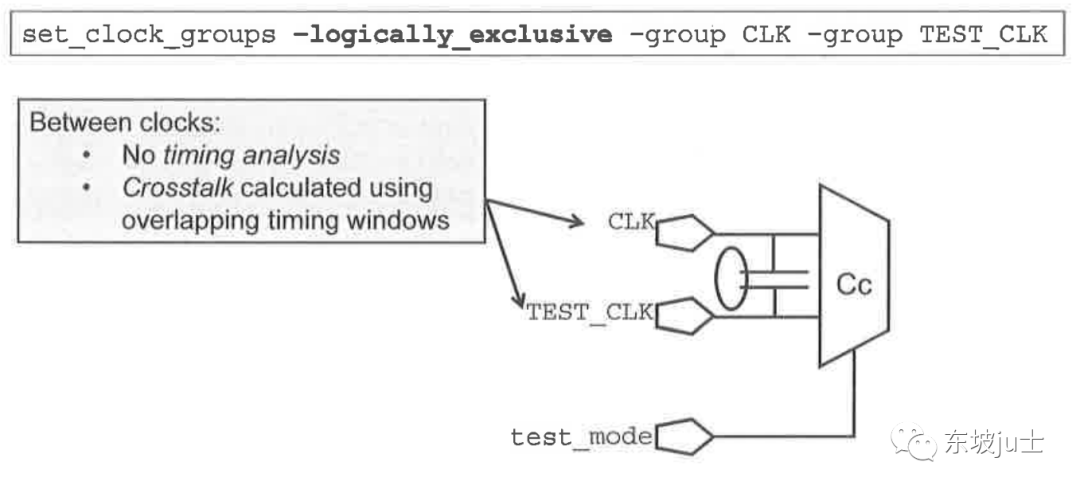

clock group 常用的一般有三种:Asynchronous、Logically Exclusive和 Physically Exclusive Clocks。一般使用 set_clock_groups 来指定。

下图所示比较清楚的表示出,两个group 之间是没有timing check的,但是会考虑到crosstalk的影响,因为不确定沿啥时候到来,所以会当成无限的timing window来计算,会有点过悲观。

下图所示是被设置了logically_exclusive 的两个group,他们之间不会有timing check,使用timing window 真实的overlap 来计算。另外 physical exclusive在物理上是两个不能共存的group,两者之间不会做crosstalk检查,更不会有timing check。

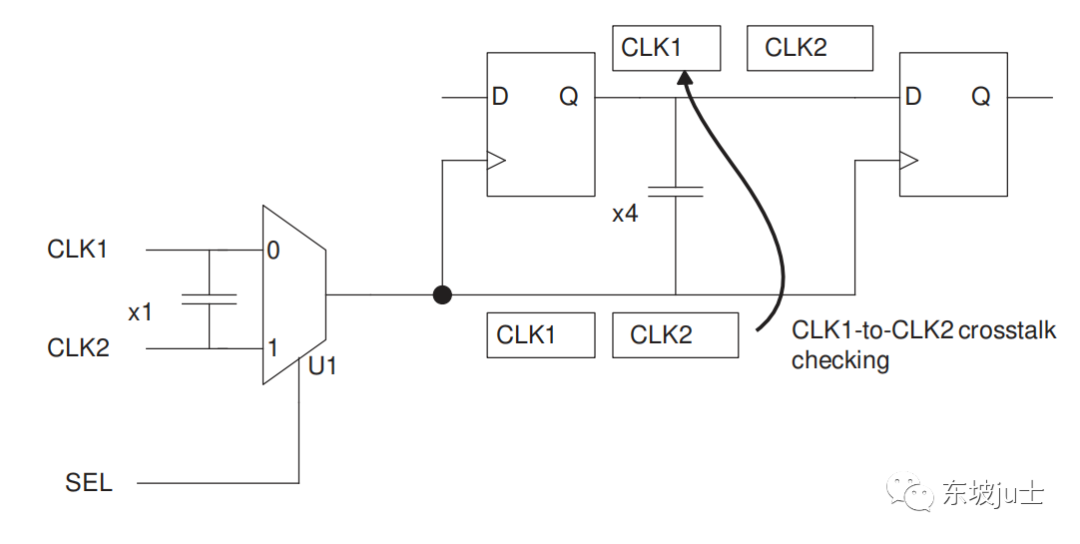

有一种case,如下图所示,我的目标是让mux U1之前的部分做crosstalk 的分析,让mux 之后的部分不做crosstalk 分析。

如果设置logically_exclusive :

pt_shell> set_clock_groups -logically_exclusive \-group {CLK1} -group {CLK2}

这样的话,mux 后面的部分就会做crosstalk分析,如果两个CLK 不同时出现在clock net 上,就会存在过悲观。

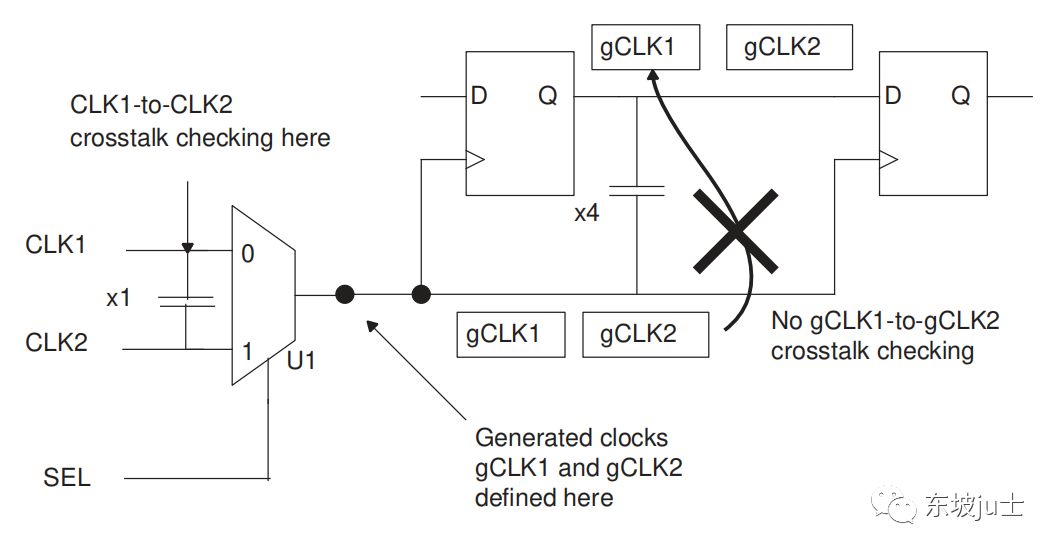

如果设置physical_exclusive :

pt_shell> set_clock_groups -physically_exclusive \-group {CLK1} -group {CLK2}

这样的话mux U1之前的部分就不会做crosstalk 分析,如果mux 前面的path 很长,就可能有比较严重的crosstalk,不做分析的话,不够悲观,这是不想看到的。

针对这种case,一般做法是设置两个分频时钟,然后把它们设置为physical_exclusive,这样就能满足需求。

pt_shell> create_generated_clock -name gCLK1 \-source [get_ports CLK1] -divide_by 1 \-add -master_clock [get_clocks CLK1] \[get_pins U1/z]pt_shell> create_generated_clock -name gCLK2 \-source [get_ports CLK2] -divide_by 1 \-add -master_clock [get_clocks CLK2] \[get_pins U1/z]pt_shell> set_clock_groups -physically_exclusive \-group {gCLK1} -group {gCLK2}

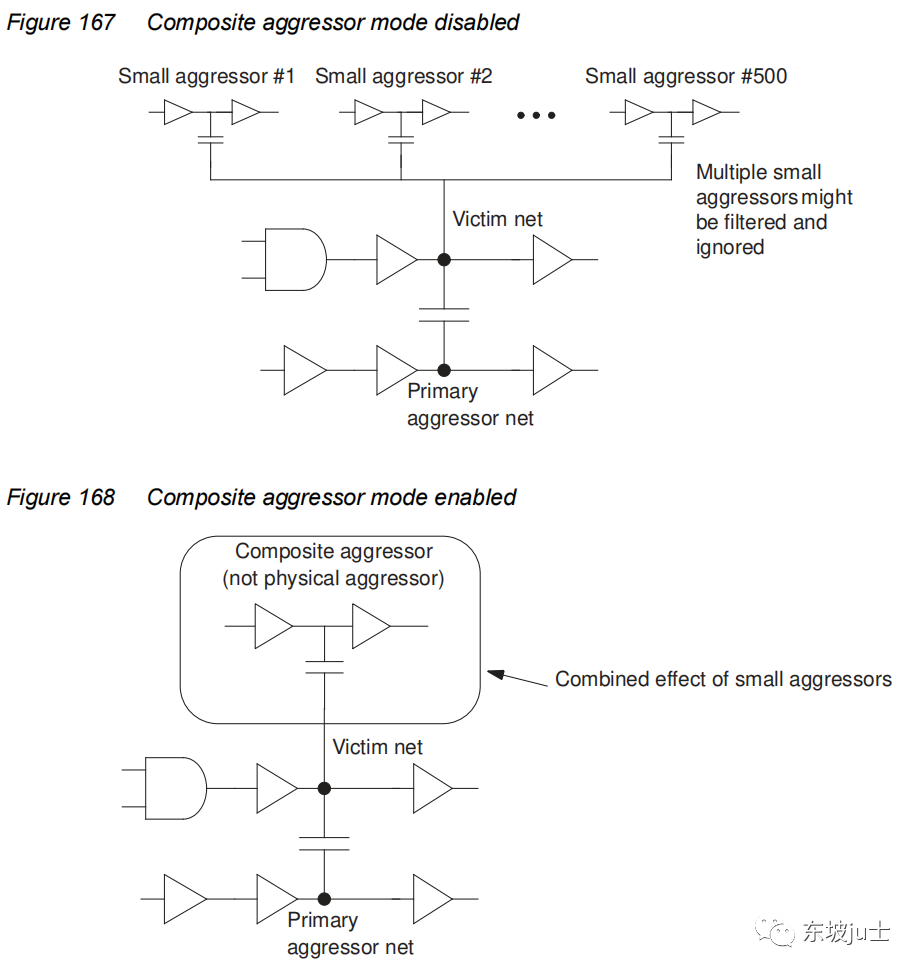

6,Composite Aggressors

PTSI在进行crosstalk分析时,有些victim nets会有很多小的 aggressors nets,它们的影响很小但数量很多,如果对每一条进行分析就会花费很长的时间和很大的机器资源,为了解决这一问题,PTSI有了composite aggressor mode (即把很多小的aggressors组合到一起形成一个复合的分析模型,用这个复合的aggressor来等价这些小aggrs带来的影响),这种mode 一般应用在 每一条victim net有很多aggressors 的design,或者对crosstalk calculations 设置high effort的时候。

下图是composite aggressor mode 的disable和enable 的示意图:

默认情况下,composite aggressor mode 是disable的,enable 可以设置si_xtalk_composite_aggr_mode statistical。可以使用si_xtalk_composite_aggr_noise_peak_ratio 来调整composite 的阈值,默认是0.01,bump voltage低于供电电压的0.01的aggressor nets 将会被复合到一起形成一个composite aggressor net,这里包含本来应该被electrical filtering的部分。

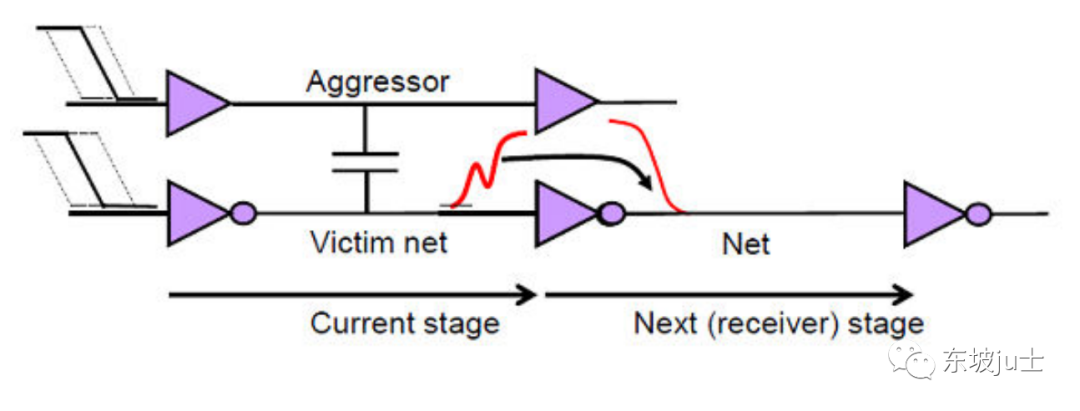

7,带有CCS Models的crosstalk 分析

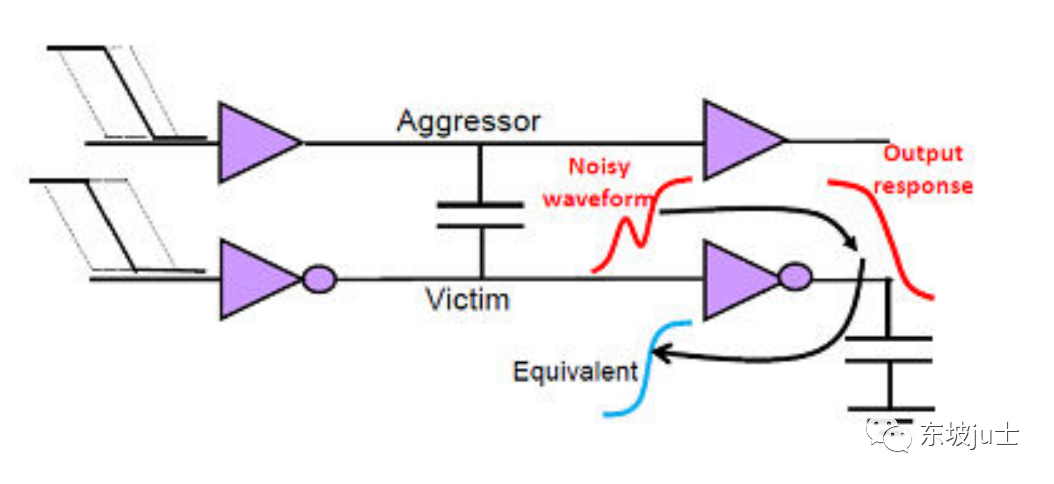

在先进工艺下,libraries 中一般会包含CCS timing和Noise models,PTSI 会使用这些数据对 victim nets 的drivers 和 receivers进行门级的建模,以此得到对crosstalk 更加精准的描述。

如下图所示,由于aggressor 的影响,victim net receiver的input pin翻转波形失真,这影响到后面的receiver stage,PTSI 会根据这种影响来建模得到delta delay。

PTSI 使用了一种等价波形来模拟这种影响,即根据output response 波形向前反推一个等价的波形,这个等价的波形(Equivalent waveform,蓝色)和 没有受到crosstalk影响的波形(Uncoupled waveform,绿色)之间的差值就是 delta delay,这个值是反推过来的值,对后面的计算没有太大意义,只是比较直观的反应出crosstalk 带来的影响大小。

8,Reports

-

report_timing 生成包含crosstalk的timing rpt

-

report_si_bottleneck 报出主要的 victim nets 或者aggressor nets

-

report_delay_calculation -crosstalk 报出指定victim net的详细crosstalk 信息

-

report_si_double_switching 报出 有double_switching的victim nets

更多文章和专题请关注微信公共号

未完待续...

有问题请指正!

这篇关于Signal Integrity: Crosstalk Delay 和 Crosstalk Noise-2的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!