本文主要是介绍TC275 GTM之CMU学习笔记,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

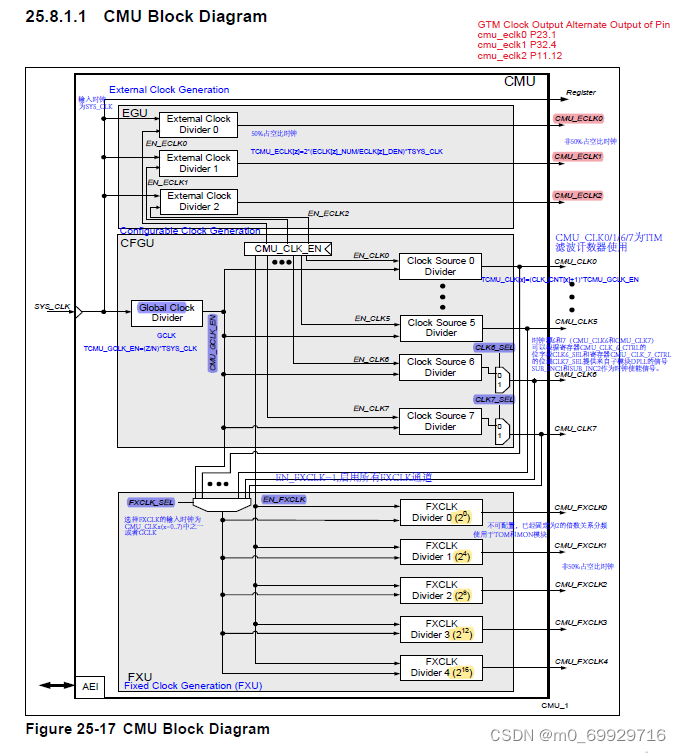

总言:CMU的共产生3种时钟:EGU(外部时钟CMU_ELCLKx,3路);CFGU(可变时钟CMU_CLKx,8路);FXU(固定时钟FXCLKx,5路),下面就以上三种类型时钟分别说明。

1.EGU(外部时钟)

CMU_ECLKx的时钟输入来源于SYS_CLK,时钟输出的周期可通过下式计算,其中CLK[x]_NUM与ECLK[x]_DEN可通过寄存器配置,理论上CMU_ELCLKx与SYS_CLK成线性关系。该时钟基本为50%占空比。

TCMU_ECLK[x]=2*(ECLK[x]_NUM/ECLK[x]_DEN)*TSYS_CLK

外部时钟的输出按以下映射到GPIO上.映射配置为后,对应的GPIO的pin可输出给外设作为时钟使用或作为PWM输出的控制端也可以。

CMU_ECLK0 P23.1

CMU_ECLK1 P32.4

CMU_ECLK2 P11.12

2.CMU_CLKx(x=0...7)可变时钟

CMU_CLKx时钟输入来源于GCLK。GCLK的计算按照以下,其中Z和N可通过寄存器配置

TCMU_GCLK_EN=(Z/N)*TSYS_CLK

CMU_CLK0/1/6/7输出可供给TIM(timer input module)使用,CMU_CLKx的计算按照以下,其中CLK_CNT[x]可通过寄存器配置。

TCMU_CLK[x]=(CLK_CNT[x]+1)*TCMU_GCLK_EN

时钟源6和7(CMU_CLK6和CMU_CLK7)可以根据寄存器CMU_CLK_6_CTRL的位字段CLK6_SEL和寄存器CMU_ CLK_7_CTRL的位域CLK7_SEL提供来自子模块DPLL的信号

SUB_INC1和SUB_INC2作为时钟使能信号。

即CMU_CLK6输出可以来源于DPLL上SUB_INC1,CMU_CLK7输出可以来源于DPLL上SUB_INC2.

3.CMU_FXCLKx(x=0...2)固定时钟

CMU_FXCLKx的时钟输入来源于CMU_CLKx(0..7)之一或GCLK.

GCLK的计算见上2.

CMU_FXCLKx(x=0...2)不可配置,已经固定为2的倍数关系分频使用于TOM和MON模块。

倍数依次是2^0,2^4,2^8,2^12,2^12.

另外,使能EN_FXCLK,那么CMU_FXCLK全部开启;反之全部关闭。与CMU_CLK/CMU_ECLK的个通道分别独立启用/关闭的不同。

寄存器说明

以上说明用到的可配寄存器参照以下

这篇关于TC275 GTM之CMU学习笔记的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!