本文主要是介绍无毛刺时钟切换电路,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

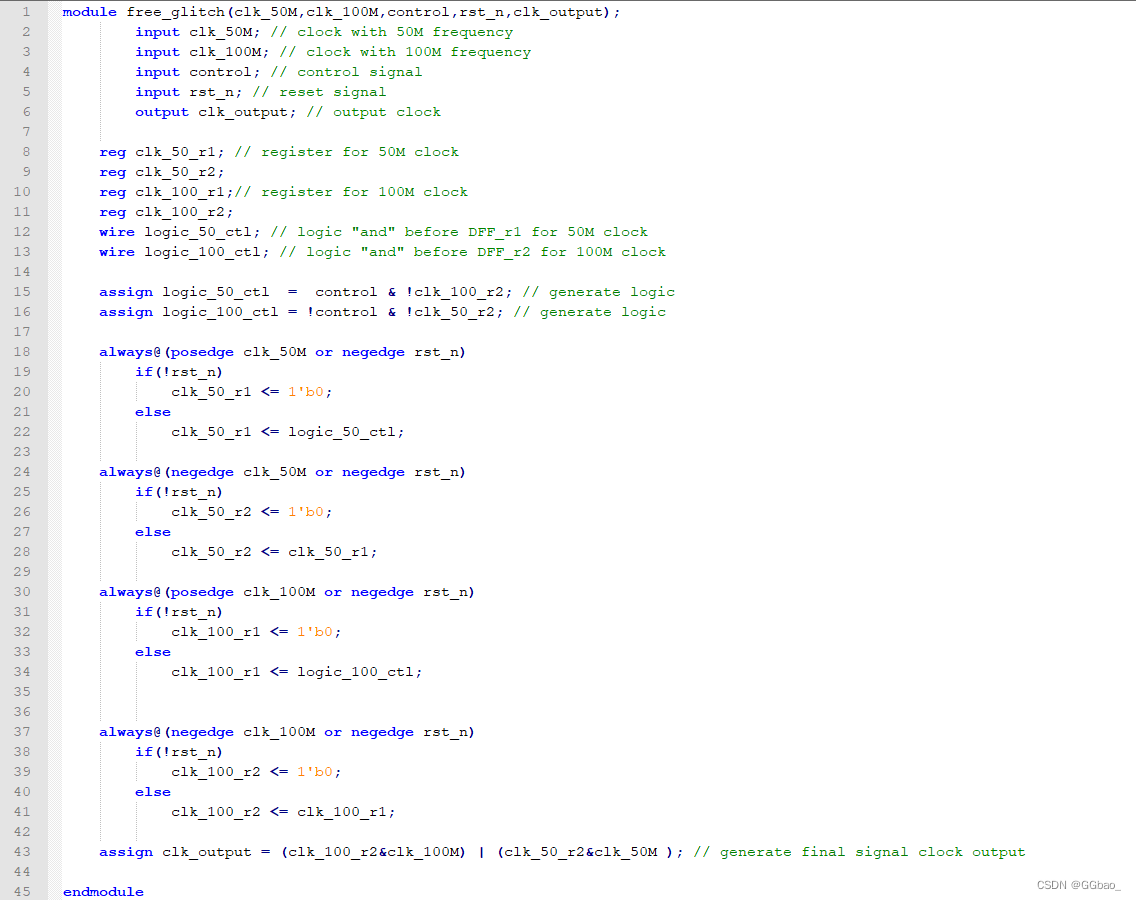

为了SOC设计的低功耗性,多时钟域的划分是常用手段之一,有两个时钟,A为50Mhz,B为100Mhz,请设计无毛刺时钟切换电路,根据控制信号control,输出所需时钟信号。

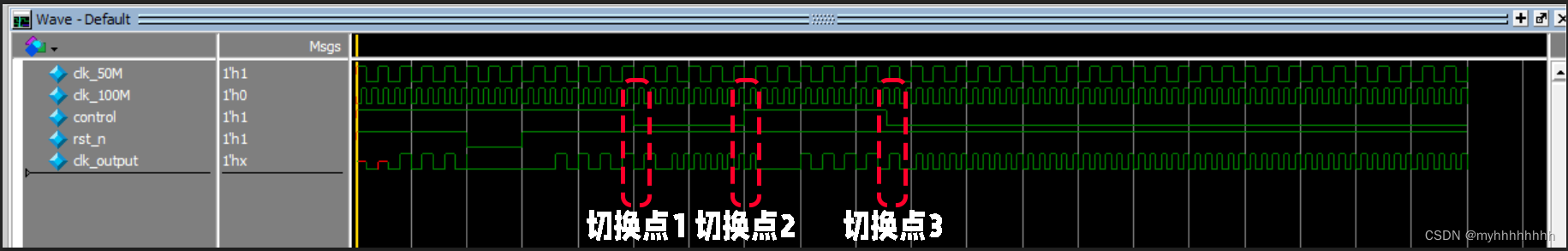

control信号至少对一个时钟信号为异步信号,导致了毛刺的出现,假如control,clk_50M,还是clk_100M都是边沿完全同步的理想信号话,应该是不会出现毛刺的。

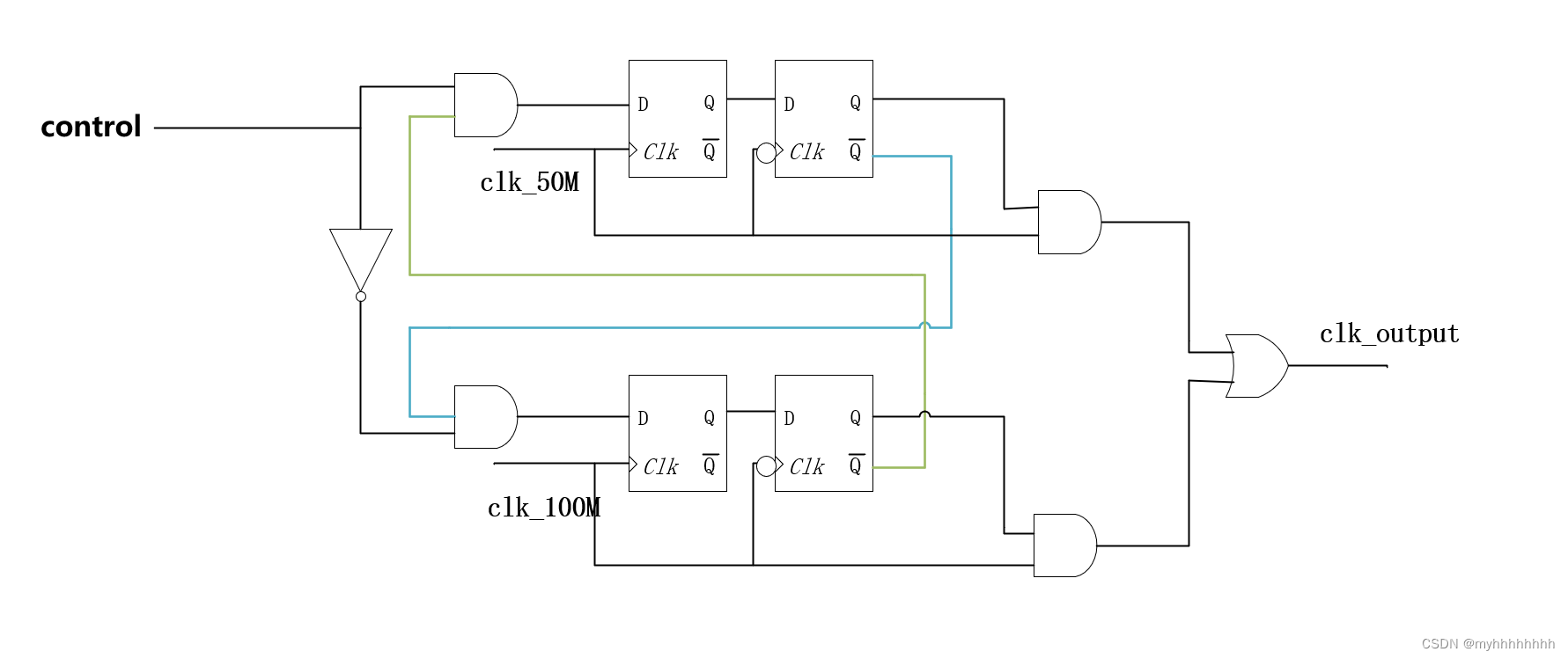

所以避免毛刺发生的方法顺理成章地过渡到了“异步信号同步化”这个理论上面,毫无疑问,肯定是需要打拍/采样的方式。我们打两拍,第一拍可以采用上升沿,第二拍可以采用下降沿。

control信号无论是从上面通过还是从下面通过,都经过两级采样,避免了亚稳态的出现

后一级的DFF用下降沿采样,避免了采样毛刺的出现

第二级DFF的not Q的逻辑以负反馈的形式接回了输入,取了与逻辑,构建起50M时钟和100M时钟的关系,代表着切换前时钟等待一阵子后,才会转换到切换后时钟,避免了切换毛刺的出现

最终上面的电路和下面的电路,以或的逻辑相取,输出clk_output.

原文链接:https://blog.csdn.net/weixin_43698385/article/details/125540056

无毛刺的时钟切换电路(Glitch-free clock switching circuit)设计(Verilog)_glitch free clock switch_李锐博恩的博客-CSDN博客

这篇关于无毛刺时钟切换电路的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!