本文主要是介绍ic后端学习笔记-floorplan,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

floorplan基础

什么是floorplan

为什么要floorplan

floorplan所需文件

floorplan的内容

创建芯片面积

放置hard macros

分配端口区域

添加特殊物理单元

创建placement及routing的blockages/halo

创建groups和regions(可选)

PG(电源/地)预布线

什么是好的floorplan

floorplan基础

什么是floorplan

floorplan是布图规划,规划包括定义芯片的大小,定义芯片内各种模块、hard macros(硬核。比如RAM,ROM及其他IP模块等)、IO等的大小和位置,有时候还需要提前定义一些placement blockages,groups/regions等等,是后端设计的第一步,也是后续所有P&R工作的基础。

floorplan与placement的区别是:floorplan规划的是抽象的module,需要摆放的东西较少,这些大块的东西摆好之后实际相当于给芯片划好片了,floorplan完成之后才可以进行placement,placement放的是具体的standard cells(标准逻辑单元)以及blocks,需要摆放的单元数目巨大,一般交给工具自动做。

为什么要floorplan

- floorpan的合理性直接关系到芯片的时序收敛、布线通畅、电源稳定及良品率。

- 一个好的floorplan和一个差的floorplan在时序上差别甚大,floorplan的目的是在保证布线畅通的同时尽量缩短走线的长度(缩小互连线的延时),需要设计者对逻辑设计及其功能有一定了解,如各个模块间的连接关系、数据通路结构等

- floorplan做的好,能够明显减小迭代次数,加快时序的signoff,以及PV方面的DRC,LVS的signoff工作。

floorplan所需文件

- netlist

- lef文件:包括tech lef&cell lef

- mmmc(多模式多端角文件):sdc&lib&qrc

floorplan的内容

- 创建芯片面积。

- 放置hard macros。

- 分配端口区域。

- 添加特殊物理单元。

- 创建placement及routing的blockages/halo。

- 创建groups和regions(可选)。

- PG(电源/地)预布线。

后面将分别介绍以上部分摆放时的注意事项。

创建芯片面积

- initial chip area。根据芯片的功能及模块的大小,估计芯片的尺寸。这通常是一个粗略的估计,经过几轮迭代后,芯片的大小将被最终固定下来。

放置hard macros

- 大多摆放在core boundary(核心边缘)的附近->减少信号传输延迟,降低功耗,节省面积。

- 在hard macros与芯片边缘之间留一些空间->后期优化方便插buffer/inverter。

- hard macro的pin脚要朝向core->方便绕线。

- 特殊IP比如pcie/PLL有特殊的摆放规则。比如pcie通常涉及高速数据传输,要避免将其放置在可能干扰其关键信号的区域;PLL对外部干扰敏感,要避免将其放置在可能受到干扰的区域,如高功耗区域或较强的EMI(电磁干扰)源附近。

- 将相同的module macro放在一起。

分配端口区域

- 通常,IO引脚应该位于芯片的边缘,以便与外部系统连接。

- 将芯片的边缘区域划分为专门的IO区域,用于放置所有的输入输出引脚。这样做可以方便后续布线和封装。

添加特殊物理单元

包括:

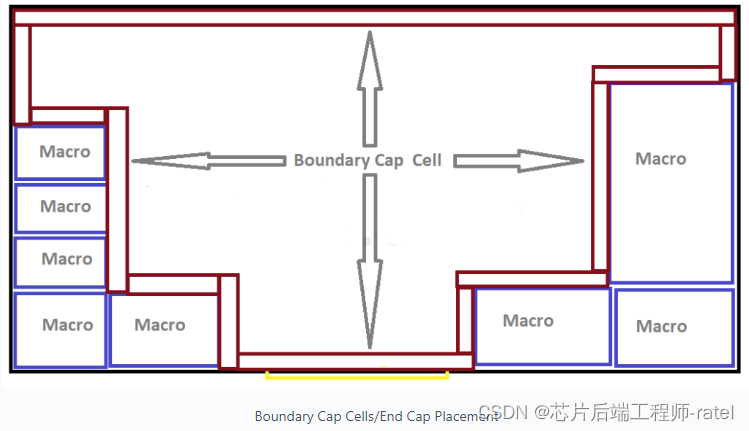

- endcap cell(boundary cell)。确保block或者hard周围是封闭的,缓解边缘效应带来的布局和电性能影响。

- well-tap cell。预防闩锁效应。CMOS闩锁效应及版图解决办法_哔哩哔哩_bilibili

- spare cell。方便postMask ECO,不需要修改base layer,只需要修改metal layer即可实现逻辑关系修改。

创建placement及routing的blockages/halo

为了避免congestion(拥堵)或不好的IR drop导致DRC,定义一些blockage约束:

- placement blockage/halo:约束工具对cell的摆放

- routing blockage:约束绕线

有四种placemnet blockages:

- hard:Hard pblk(placement blockage)区域是tool不论在任何阶段都不能放cell进来,最终出来的database一定是没有任何cell在hard pblk里的,除非user手动加。

- soft:tool在摆放阶段时候不能放cell进来,但是后续的legalization和optimization就可以放进来了(only place buffer&inverter)。

- partial:可以摆放,但是要约束在一定的密度下。就是tool可以摆进来一定数量的cell,其面积不能超过partial pblk所规定的百分比。

- macro only:不能摆放macro。

placement blockage与halo的区别:

还有一种很像placement blockage的概念,叫做halo,或者keep out margin。它不是加在floorplan上的,而是加在特定instance上的。比如我给一个macro加了一个宽度1um的halo,它的作用其实也等效于加宽度1um的pblk。但是halo是加载instance上的,意思是如果我们移动了instance,其halo也会跟着一起移动,永远保证它周围1um范围不会有cell。而pblk不一样,instance动的话和pblk没关系。Halo能帮我们方便地处理某些情况,比如我们不希望某一类cell靠在一起,就可以给这类cell左右两边加halo。

————————————————

版权声明:本文为CSDN博主「伟酱的芯片后端之路」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_52636726/article/details/122501706

创建groups和regions(可选)

指的是创建布局约束。布局约束是对标准cell或module的位置约束,PR工具允许我们将一定的单元约束到特定的区域内。布局约束有四种,分别为soft guide,guide,region,fence。四种约束能力由弱变强。

- guide(向导约束):可进可出。被指定的单元可以放在guide内,也允许放在guide外(可出);其他不属于该模块的单元允许进入guide(可进)。

- region(区域约束):可进不可出。被指定的单元只能防在region内,不可以放在region外(不可出);其他不属于该模块的单元允许进入region(可进)。

- fence(限制约束):不可进不可出。被指定的单元只能放在fence内(不可出);不属于该模块的单元不允许进入fence(不可进)。

- soft guide(弱向导约束):与guide类似,只不过不指定具体的位置。

上面的blockage/halo约束的是cell不能放在哪,这里的groups/regions约束的是cell要放在哪。

PG(电源/地)预布线

电源布线贯穿设计的整个阶段,是一个随设计阶段不断迭代的过程。而floorplan中的电源预布线规划非常关键,奠定后续布线的基础。

- PG网络包括core power mesh,IO power connection,hard macro power connection。

- 特殊IP比如PLL/DDR有特定的PG约束,比如ARM要特别注意IR及EM问题。

什么是好的floorplan

- 各模块的cell符合data flow

- congestion map和cell density适度

- 通过cell density分布图可以预估可能会出现的density过高导致的烧线或timing等风险

- cell density过低,congestion map也特别好,这也不恰当,会浪费芯片面积

- routing的DRC尽量clean

- base layer没有DRC

这篇关于ic后端学习笔记-floorplan的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!