本文主要是介绍传习录-Mentor-dft 学习笔记 day6-flattenlearning,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Model Flattening

T为了正常工作,ATPG工具和Tessent Scan必须使用自己的内部设计表示。这些工具通过展平模型并用它们自己的primitive源于替换网络列表(如库中所述)中的设计单元来创建这些内部设计模型。在设计规则检查之前,当您最初尝试退出设置模式时,这些工具将展平模型。这就是一个扁平化的过程。

The Flattening Process

The flattened model contains only simulation primitives and connectivity, which makes it an

optimal representation for the processes of fault simulation and ATPG.(注意的是仿真原始话和连通性)。

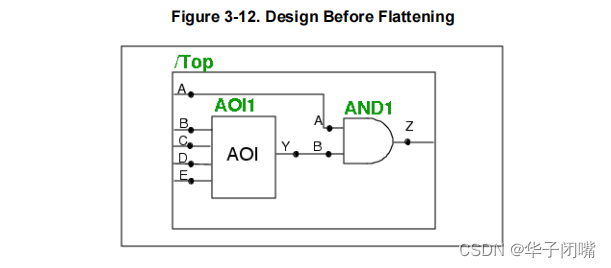

这是flatten之前的电路

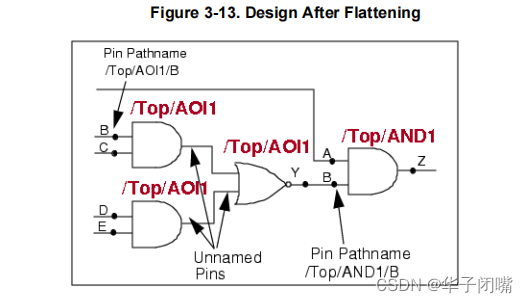

下面是扁平化之后的图形

展平后,只有命名才能保留设计层次结构;也就是说,扁平网表通过实例命名来维护层次结构。图3-12-3-13 ,top为最高等级 用 两个and门和一个nor门替代了一个aoi,展平过程引入的管脚保持未命名状态,相同引脚保持命名不变

Learning Analysis

flattening后,ATPG工具对设计进行广泛的分析,以学习可能有助于在后续过程中进行智能决策的行为

这篇关于传习录-Mentor-dft 学习笔记 day6-flattenlearning的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!