本文主要是介绍可编程定时计数器8253/8254,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在微机应用系统中,定时控制具有重要的作用。经常会有这样的应用要求:一种是要求有一些外部实时时钟,以实现延时控制或定时;另一种是要求能对外部事件计数的计数器。在微机系统中,常采用以下三种方法实现:软件定时,不可编程硬件定时和可编程硬件定时。

可编程定时/计数器的工作原理

定时和计数的本质是相同的,它们都是对一个输入脉冲进行计数,如果输入脉冲的频率一定,则记录一定个数的脉冲,其所需的时间是一定的,例如,输入脉冲的频率为2MHZ,则:计数 2∗106 —- 定时1秒。

因此,使用同一个接口芯片,既能进行计数,又能进行计时,统称为计时器/计数器。(Timer/Counter简称T/C)。计数器逻辑原理如图6-4所示,定时/计数器的基本原理如图6-5动画所示。

主要构成

- (1)控制寄存器;决定工作模式。

- (2)状态寄存器;反应工作状态(可无,如8253无此寄存器)。

- (3)初值寄存器;计数的初始值。

- (4)计数输出寄存器;CPU从中读出当前计数值。

- (5)计数器;执行计数操作,CPU不能访问。

工作原理

对 CLK 信号进行“减1计数”。首先CPU把“控制字”,写入“控制寄存器”,把“计数初始值”写入“初值寄存器”,然后, 定时/计数器按控制字要求计数。计数从“计数初始值 开始,每当 CLK 信号出现一次,计数值减1,当计数值减为0时,从 OUT 端输出规定的信号(具体形式与工作模式有关)。当 CLK 信号出现时,计数值是否减1(即是否计数),受到“门控信号” GATE 的影响,一般,仅当 GATE 有效时,才减1.门控信号 GATE 如何影响计数操作,以及输出端 OUT 在各种情况下输出的信号形式与定时/计数器的工作模式有关。这里,应该指出如此三点。

- (1) CLK 信号是计数输入信号,即计数器对 CLK 端出现的脉冲个数进行计数。因此 CLK 端可以输入外部事件,如产品线上通过一个产品,脉 冲电度表发出一个脉冲。这种情况,对应于 定时/计数器作为计数器使用。 CLK 端也可接入一个固定频率的时钟信号,即对该时钟脉冲 计数,从而达到计时的目的。

- (2) OUT 信号在计数结束时,发生变化,可以将 OUT 信号作为外部设备的控制信号,也可以将 OUT 信号作为向CPU申请中断的信号。

- (3) CPU可以从“计数输出寄存器”中读出当前计数值。一般情况下,“计数输出寄存器”的值随着计数器的计数值变化,CPU读取其值 之前,应向“控制寄存器”发送一个锁存命令,这时,“计数输出寄存器”的值不再随计数器的值变化,CPU用输入指令从“计数输出 寄存器”中读得当前计数值。输入指令(读命令)同时又使“计数输出寄存器”的值随计数器的值变化。

8253/8254 的内部结构和外部引脚

8253/8254 的内部结构

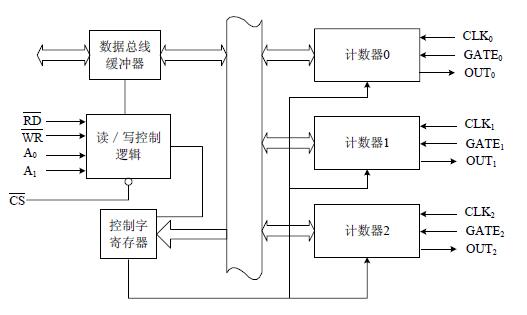

8253 内部结构框图可知,它由数据总线缓冲器、读/写控制逻辑、控制字寄存器以及3 个计数器(计数器0、计数器1、计数器2)等组成。

动态过程展示链接

-

(1)数据总线缓冲器

8 位双向三态缓冲器,用于连接系统数据总线和8253 内部总线。以便编程时:- 处理器对8253写入控制字

- 处理器写入计数初值

- 处理器从计数器读取计数值。

-

(2)读/写控制逻辑

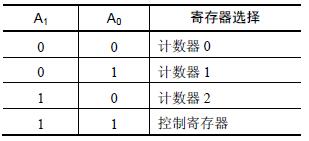

8253 内部的控制电路,读写逻辑接收来自CPU 的控制信号,经过组合,产生对8253各部分的控制。具体为:- A1 、 A0 —用来对3个计数器和控制积存器进行寻址。

- RD¯¯¯¯¯ —读信号。当 RD¯¯¯¯¯ 为低电平时有效,此时,表示CPU正在对8253的一个计数器进行读操作。

- WR¯¯¯¯¯¯ —写信号。当 WR¯¯¯¯¯¯ 为低电平时有效,此时,表示CPU正在对8253的几个计数器进行写操作。

- CS¯¯¯¯¯ —片选信号。只有在 CS¯¯¯¯¯ 为持续低电平的情况下, RD¯¯¯¯¯ 和 WR¯¯¯¯¯¯ 才会受到确认,否则会被忽略。

-

(3)控制字寄存器

控制字寄存器接收CPU 送来的控制字,决定每个计数器的工作方式、读写格式和计数的数制。当 A1 A0 =11 时,用来接收CPU 输出的控制字。该寄存器是个只能写入寄存器。

有兴趣多多了解的请点链接。

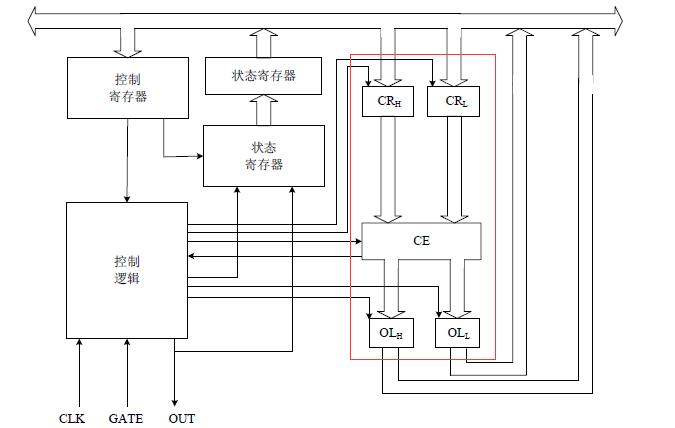

- (4)计数器(计数器0、计数器计1、数器2)

8253 内部有3 个相互独立且结构功能完全相同的定时/计数器:0、1 和2。每个计数器包含一个控制字寄存器、16 位的初值寄存器CR(Count Register)、减“1”计数器CE(Counting Element)和16 位输出锁存寄存器OL(Out put Latch)。

减“1”计数器的初始值由程序设定,是初值寄存器的内容。计数器的当前值存放在输出锁存寄存器,CPU 可以在需要的时候读出这个值。

每个计数器有3 根信号线:时钟输入信号 CLK 、门控信号输入 GATE 和输出信号 OUT 。

计数器工作时,每出现一个 CLK 脉冲,减“1”计数器中的计数值减1,当计数值减为0 时,通过 OUT 输出结束信号,表明计数执行单元已为0,输出信号的波形由工作方式确定。当 CLK 是一个周期性的时钟信号时,计数器为定时器功能;当 CLK 是一个非周期性事件计数信号时,此时为计数器功能。8253 的定时时间取决于时钟脉冲的频率和计数器的初值:

此外,可以通过 GATE 引脚上的门控信号允许或停止计数器的过程。

8253 的外部引脚

-

D7 ~ D0 :双向数据线,与系统数据总线相连,供CPU 对8253 进行读/写操作,进行信息交换。

-

CS¯¯¯¯¯ :片选线,输入低电平有效。当 CS¯¯¯¯¯ = 0 时,表示CPU 选中8253 芯片,可对8253 进行读/写操作;当 CS¯¯¯¯¯ = 1 时,表示CPU 未选中8253 芯片。 CS¯¯¯¯¯ 信号是由CPU 输出的高位地址(通常 A9 ~ A2 )和AEN 信号经过电路译码后产生。

-

A1 ~ A0 :地址输入信号,用于选择8253 内部寄存器。当 CS¯¯¯¯¯ 为低电平有效时,选中8253芯片,然后通过 A1 A0 组合编码决定选中计数器

-

RD¯¯¯¯¯ 和 WR¯¯¯¯¯¯ :读/写控制输入信号端,低电平有效。当 CS¯¯¯¯¯ = 0, RD¯¯¯¯¯ = 0 时,表示CPU 可对8253 的一个计数器进行读操作;当 CS¯¯¯¯¯ = 0, WR¯¯¯¯¯¯ = 0 时,表示CPU 可对8253 的一个计数器或控制字寄存器进行写操作。

-

GATE :门控输入信号。是一根外部控制计数器工作的输入信号线,用作控制启动或中止定时/计数。对于8253 这6 种不同的工作方式, GATE 信号的有效方式也不同,可以是上升沿信号有效或是电平信号有效。

-

CLK :外部脉冲信号输入端 CLK0 、 CLK1 、 CLK2 ,分别为计数器0、计数器1、计数器2的脉冲信号输入端。计数器对该引脚输入的脉冲信号进行计数, CLK 脉冲信号可以由系统时钟、系统时钟分频或者其他脉冲源提供。 CLK 输入脉冲可以是均匀的、连续的或周期精确的信号,也可以是不均匀的、不连续的或非周期的信号。如果输入脉冲是精确的时钟信号,则8253 起定时作用;如果输入脉冲是非周期的信号,则8253 起计数作用。

-

OUT :定时时间到或计数减为零的向外输出信号端 OUT0 、 OUT1 、 OUT2 ,分别为计数器0、计数器1、计数器2 的脉冲信号输出端。无论8253 的计数器工作在什么方式,当计数器减到0 时,信号输出端 OUT 必定有一个电平或脉冲信号输出,用以指示定时时间到或者计数结束。该信号可供CPU 检测,也可以作为中断请求信号。

8253/8254 的工作方式

8253 共有6 种工作方式,由方式控制字确定,同一芯片中的三个计数器可以通过初始化分别设定为不同的工作方式。各方式下的工作状态是不同的,输出的波形也不同,但大致相同。

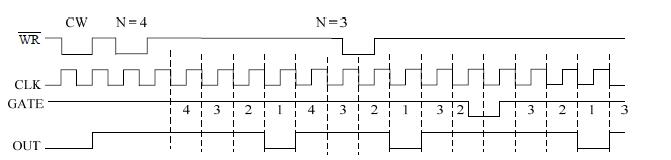

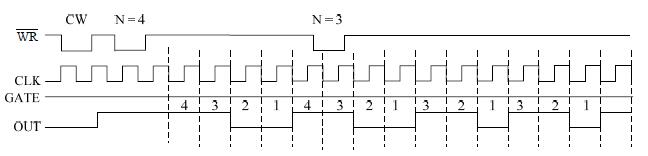

方式0:计数结束产生中断(Interrupt on Terminal Count)

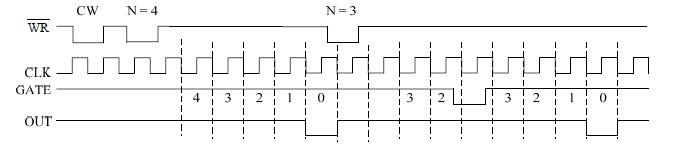

方式0 为计数结束产生中断,工作时序如图下示。

当计数器工作方式设置为方式0 后,该计数器的OUT 输出信号立即变为低电平,且计数过程中一直保持低电平。在经初值寄存器赋初值后,如图中初值为N=4,开始计数,在每个CLK 时钟下降沿,计数器进行减1 计数,当计数减1 减到0 时,OUT 输出信号变为高电平,且一直保持到该计数器重新赋初值,或重新设定工作方式。该信号可以作为中断请求信号。

GATE 输入信号用于控制计数的过程。GATE 作用于计数器,GATE 为高电平时,允许计数;GATE 为低电平时,暂停计数。当GATE 重新为高电平时恢复先前的计数过程。

方式0 无自动装入计数初始值的功能,若要继续计数,则需要重新写入计数初始值。在计数期间,装入新的初始值,计数器会在初始值写入后重新开始计数。

方式1:可编程单稳态触发器(Hardware Retriggerable one-shot)

方式1 为一种硬件触发启动,无自动重复计数方式,可在OUT 输出单稳脉冲。

写入方式1 的控制字后,OUT 输出高电平,一直保持。当CPU 写入计数初值,等到GATE上升沿到达后,计数器被启动。此时,在CLK 脉冲下降沿开始计数,OUT 输出低电平。在每个CLK 时钟下降沿,计数器进行减1 计数,当计数减1 减到0 时,OUT 输出信号变为高电平。故OUT 输出一个宽度为计数值N个时钟周期的单稳脉冲。

计数结束后,若GATE 上升沿到达,再次触发启动,则可以又以上次写入的初值开始,在下一个CLK 下降沿开始计数,不需要重新写入初值,OUT 输出一个单稳脉冲。

在整个计数过程中,可以写入新的初值,这对正在进行的计数过程不影响。但当有新的GATE 上升沿到达,则计数器将先前的新初值装入,从头开始计数。

方式2:分频器(Rate Generator)

方式2 是具有自动装入计数常数、GATE 为电平触发方式的分频器。

写入方式2 控制字后,OUT 输出高电平。写入计数初值后,如果GATE 为高电平,计数器开始对输入时钟CLK 脉冲计数。OUT 输出信号在计数过程中一直是高电平,直到减1 计数器减到1 时,OUT 输出变为低电平,维持一个CLK 时钟周期,OUT 又恢复输出高电平,同时计数器开始重新计数。

方式2 可以自动连续工作,输出固定频率的脉冲信号。如果计数值为N,则输出的脉冲信号频率为1/N 的时钟频率,故该方式被称为分频器。

方式2 中,在计数过程中写入新的值,不影响正在进行的计数过程,从下个计数周期开始按新值计数。GATE 为低电平时,禁止计数器,并使OUT 输出为高电平;GATE 为高电平

时,计数器恢复写入的初值,开始计数。

方式3:方波发生器(Square Ware Mode)

方式3 与方式2 类似,也是一种具有自动装入计数常数N 分频方波发生器。

写入方式3 控制字后,OUT 输出高电平。写入计数初值后,如果GATE 为高电平,计数器开始对输入时钟CLK 脉冲计数,当计数到计数值一半时,OUT 输出变为低电平,直到计数为0 时,OUT 输出又变为高电平。当计数值为偶数时,OUT 输出高、低电平都为N/2 个CLK周期的周期信号;当计数值为奇数时,OUT 输出高电平为(N+1)/2 个CLK 周期、低电平为(N-1)/2个CLK 周期的周期信号,即OUT 输出前一半多一个CLK 周期的高电平。

方式4:软件触发选通脉冲(Software Triggered Strobe)

方式4 是一种软件触发启动,无自动重复计数功能的计数方式。

写入方式4 控制字后,OUT 输出立即变为高电平,如果GATE 为高电平,当写入计数初值后,在下一个CLK 脉冲的下降沿开始减1 计数,当计数器减到0 时,OUT 输出为低电平,计数器停止计数。计数过程只执行一次,只有写入新的计数值,才开始新的计数。计数期间,如果写入新的计数值,则在下一个时钟的下降沿立即按新写入的计数值重新计数。当GATE为低电平时,禁止计数;当GATE 为高电平时,从初值开始重新计数。

方式5:硬件触发选通脉冲(Hardware Triggered Strobe)

方式5 为硬件触发启动、无自动重复计数功能的计数方式。

写入方式5 控制字后,OUT 输出保持高电平,写入计数初值后,但不开始计数,当GATE出现上升沿后,启动计数器,在下一个CLK 下降沿开始减1 计数,当计数到0 时,OUT 输出为低电平,经过一个CLK 脉冲,OUT 输出恢复高电平,计数器停止。在计数过程中,GATE重新出现上升沿时,将使计数器从初值开始重新计数。

OUT 输出脉冲宽度在正常计数情况下,如果写入的计数值为N,OUT 输出维持N 个CLK时钟周期的高电平,1 个CLK 时钟周期的低电平。

8253编程命令

因为8253的控制积存器和3个计数器分别具有独立的编程地址,并且控制字本身的内容又确定了所控制的积存器序号,所以,队8253的编程没有太多严格的顺序规定,可以非常灵活.但是,编程有两条原则必须严格遵守:

-

(1)对计数器设置初始值前必须先写控制字。

-

(2)初始值设置时,要符合控制字中的格式规定,即只写低位字节还是写高位字节,或者高低位字节都写,控制字中一旦规定,具体初始值设定时就要一致。

8253 初始化编程

初始化工作有2点:

-

(1)写入控制字;

-

(2)按控制字的要求写入计数初值。

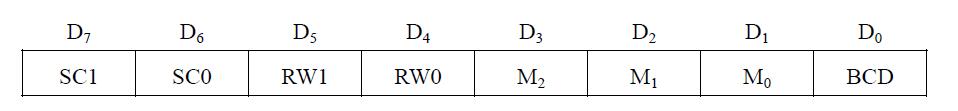

8253 的每个计数器内有一个8 位控制寄存器,用来存放CPU 写入的工作方式控制字,工作方式控制字格式如下图所示,该寄存器只能执行写入操作,不能执行读出操作。8253 内部的3 个计数器在结构上相互独立,在使用时须对指定的计数器写入方式控制字,写入控制字的I/O 地址相同,要求 A1A0=11 。

-

D0 :计数码选择。8253 提供丰富的计数制,该位用来决定计数器在减1 计数过程中采用的是二进制还是十进制,0 表示采用二进制计数制,1 表示采用BCD 计数制。

- 在BCD 计数制下,写入计数值的范围为0000~9999,最大值为104,即十进制数的10000,表示为0000;在二进制计数制下,写入计数值的范围为0000~FFFFH,最大值为216,即十进制数的65536,表示为0000H。

-

D3 ~ D1 :M2、M1、M0 为8253 的工作方式的选择。8253 的每个计数器的6 种工作方式如下表所示。

-

D5 、 D4 :RW1 和RW0 读写格式控制。计数值的读出或写入可按字节或字两种方式进行操作。 D5 D4 =01,只读写低8 位,高8 位自动置0; D5 D4 = 10,只读写高8 位,低8 位自动置0;

-

D5 D4 = 11,必须先读写低8 位,后读写高8 位; D5 D4 = 00,锁存命令,用于把当前计数值存入输出锁存器,供以后读取。

-

D7 、 D6 :计数器选择。 D7 D6 = 00,选择计数器0; D7 D6 = 01,选择计数器1; D7 D6 = 10,

选择计数器2; D7 D6 = 11,在8253 中为非法编码,在8254 中用于读回命令。

设三个计数器的CR/OL端地址为0070H、0071H、0072H控制寄存器端口地址为0073H。

例1. 计数器0,工作在模式2,计数初值和输出锁存器仅使用低8位,初值为100,计数值为二进制格式。

MOV AL,00010100B ;控制字 OUT 73H,ALMOV AL,100 ;计数初值 OUT 70H,AL - 1

- 2

- 3

- 4

- 1

- 2

- 3

- 4

例2.计数器1,工作在模式1,CR和OL使用16位,初值为1234,先写入低8位,再写高8位,计数值为BCD。

MOV AL,01110011B ;控制字 OUT 73H,AL MOV AX,1234H ;BCD 1234OUT 71H,AL ;计数初值低8位MOV AL,AHOUT 71H,AL ;计数初值高8位- 1

- 2

- 3

- 4

- 5

- 6

- 1

- 2

- 3

- 4

- 5

- 6

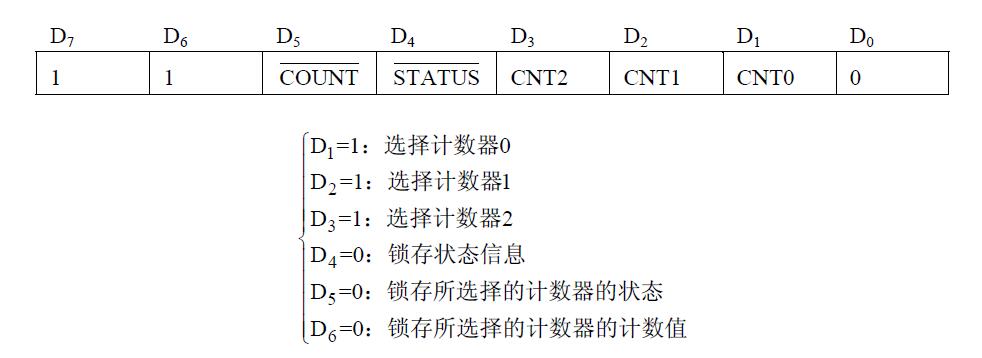

8254 读回命令

8254 较8253 的改进主要有:8254 的计数频率更高;8254 多了一个读回命令。这个读回命令(写入控制寄存器)可以使3 个计数器的计数初值和状态锁存,向CPU 返回一个状态字。

其格式如下图所示。

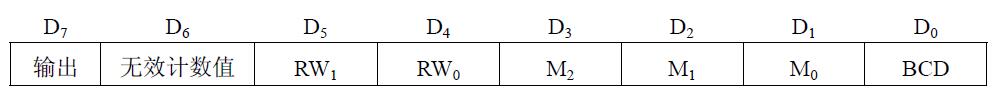

8254 中每个计数器都有一个状态字,可通过读回命令将其锁存,然后由CPU 读取。状态字的格式如下图所示。

格式中D5~D0 位为写入此计数器的控制字的相应部分。D7 位反映该计数器的输出引脚的现行状态,输出为高电平,D7 = 1;输出为低电平,D7 = 0。D6 位反映计数初值寄存器中计数初值是否已装入减1 计数器中,若最后写入计数初值寄存器的计数值已装入减1 计数器,则D6 = 0,表示可读计数;若计数初值寄存器的计数值未装入减1 计数器,则D6 = 1,表示无效计数,读取的计数值将不反映刚才写入的那个新计数值。

读出命令用来读取计数器的当前计数值,读取命令分两步完成:

-

(1)发出锁存命令,使当前计数值锁存在输出锁存器(OL)中

-

(2)读输出锁存器(OL),获得当前计数值。

必须注意:计数值是16位的,但8253均为8位端口,必须分两次读取,才能获得16位的值,为了避免第1次读 取后,计数值发生变化,必须使用锁存命令使计数值锁存在输出锁存器中,然后分两次从输出锁存器中读取16位值。 例:读出计数器0的当前计数值,放在BX中。 MOV AL,00000000B ;锁存,OUT 73H,AL IN AL,70H ;当前计数值低8位MOV BL,ALIN AL,70H ;当前计数值高8位 MOV BH,AL ;读取后,OL的值又随计数执行部件变化

这篇关于可编程定时计数器8253/8254的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!