本文主要是介绍ARM32开发——总线与时钟,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

🎬 秋野酱:《个人主页》

🔥 个人专栏:《Java专栏》《Python专栏》

⛺️心若有所向往,何惧道阻且长

文章目录

- APB总线

- 时钟树

- 时钟树

- 外部晶振

- 内部晶振

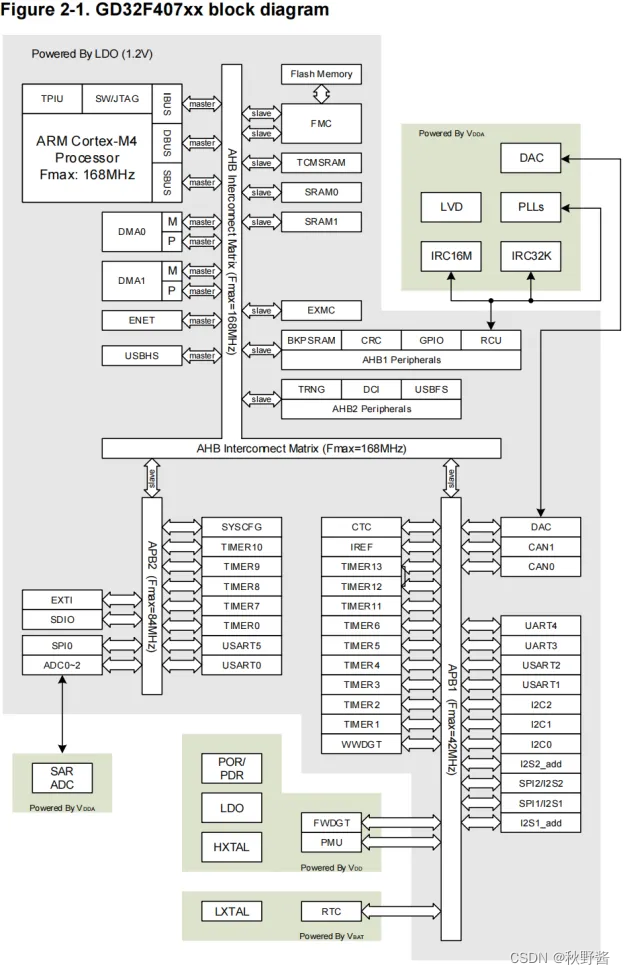

在这个例子中,这条大街和巴士构成了一套系统,我们称之为AHB总线。

● 不同的房子代表着不同的功能功能外设,比如GPIO,SRAM,USBHS等。

● 房子的灯表示是否启用对应的功能。

● 房子的招手员决定了功能执行的频率。

● 大巴士24小时不间断准时发车,可以理解为晶振震荡过程中,会去按照房子招手员的频率去访问他们。

简单的进行总结,AHB的主要作用是帮助不同的硬件组件(比如处理器、内存、外设等等)之间高效地传输数据和信息。想象一下,计算机就像是一个大家庭,各个成员需要分享信息和资源。AHB就像是家庭里的交通工具,让不同的家庭成员之间能够顺畅地交流和共享。

APB总线

APB的全称是"Advanced Peripheral Bus",中文翻译就是"高级外设总线"。这是一种用于连接计算机系统中外部设备(外设)的总线架构,它可以帮助外设和其他部件之间传输数据和信息。这个总线通常用于连接一些相对简单的外部设备。

APB的作用和AHB类似,只不过AHB是大巴士,APB是小巴士,吞吐量不同。

时钟树

时钟树

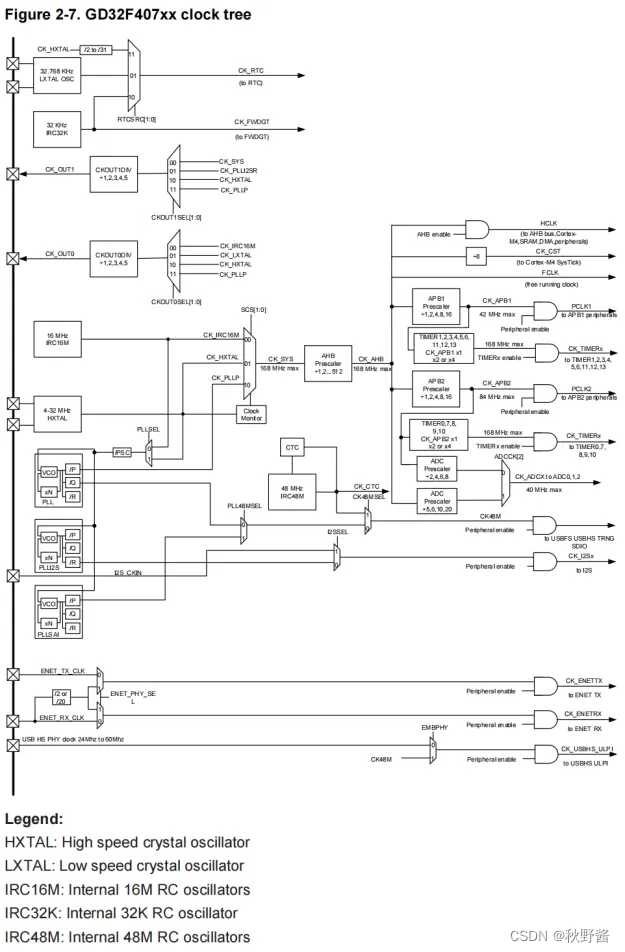

Clock Tree。时钟树是在集成电路设计中的一个重要概念,它是一种组织结构,用于分配和传递时钟信号到芯片内的各个功能模块。时钟树的设计和优化对于确保整个芯片的正常运行、时序准确性和功耗效率都非常关键。

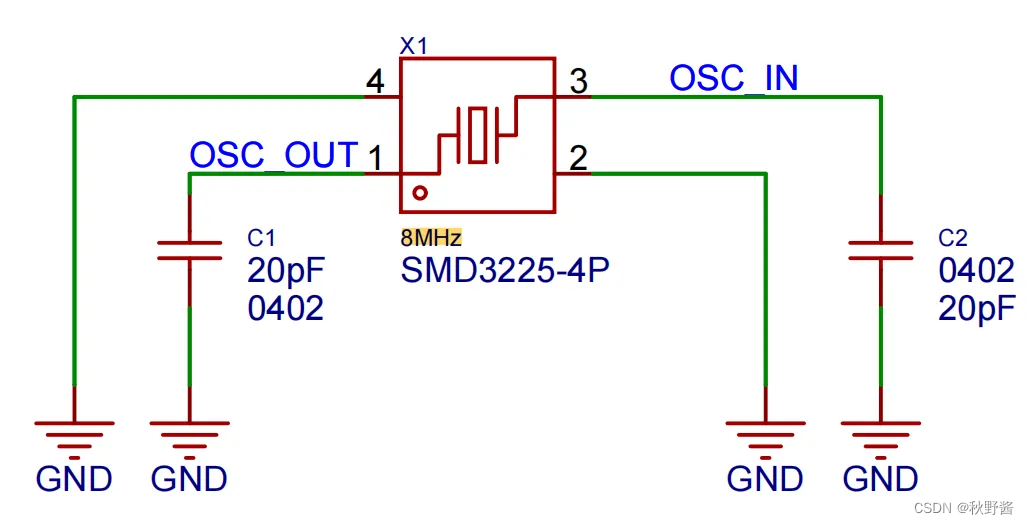

外部晶振

内部晶振

芯片内置了一个16M的晶振和一个48M的晶振

倍频

将一个较低频率的时钟信号倍频到更高频率是一种常见的操作,通常使用锁相环(PLL,Phase-Locked Loop)或者数字锁相环(DLL,Delay-Locked Loop)等电路来实现。以下是一个基本的步骤来将外部晶振8M倍频到168M,假设你使用的是PLL:

- 反馈回路设置:将外部晶振8M连接到PLL的参考输入。这个参考输入相当于上面提到的“主时钟源”。

- 设置分频比:调整PLL的分频比,这个分频比就是你想要的倍频比。在你的情况下,希望从8M倍频到168M,那么分频比就是168M/8M = 21。

- 锁定环路:启动PLL,并且调整它的参数,使得输出频率为所需的168M。这个过程中,PLL会自动调整内部的时钟信号来尽量与输入参考时钟同步。

GD32和STM32采用的就是PLL这种方式实现倍频的。

这篇关于ARM32开发——总线与时钟的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!