本文主要是介绍常用IP核的引脚图,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、复数乘法

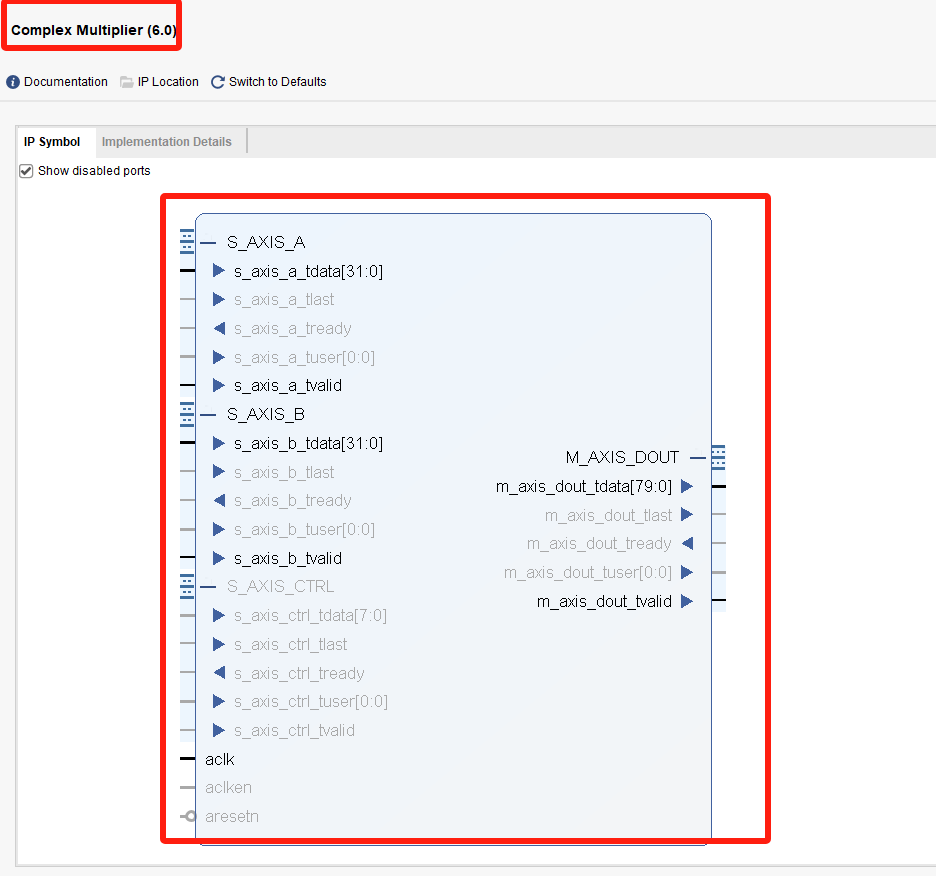

这是一个Xilinx(赛灵思)的复数乘法IP核的接口图,包含了几个主要的AXI-Stream接口。每个接口都有其特定的用途,下面将详细解释各个引脚的作用。

主要接口和引脚说明

S_AXIS_A(输入复数A)

- s_axis_a_tdata[31:0]: 输入数据通道A,通常用于传输复数A的实部和虚部。

- s_axis_a_tlast: 指示传输的最后一个数据(用于分组数据)。

- s_axis_a_tready: 表示从端准备好接收数据。

- s_axis_a_tuser[0:0]: 用户定义信号,用于传输与数据相关的控制信息。

- s_axis_a_tvalid: 表示数据A有效。

S_AXIS_B(输入复数B)

- s_axis_b_tdata[31:0]: 输入数据通道B,通常用于传输复数B的实部和虚部。

- s_axis_b_tlast: 指示传输的最后一个数据。

- s_axis_b_tready: 表示从端准备好接收数据。

- s_axis_b_tuser[0:0]: 用户定义信号。

- s_axis_b_tvalid: 表示数据B有效。

S_AXIS_CTRL(控制信号)

- s_axis_ctrl_tdata[7:0]: 控制数据,通常用于配置或控制IP核的操作模式。

- s_axis_ctrl_tlast: 指示控制数据的最后一个数据。

- s_axis_ctrl_tready: 表示从端准备好接收控制数据。

- s_axis_ctrl_tuser[0:0]: 用户定义的控制信号。

- s_axis_ctrl_tvalid: 表示控制数据有效。

M_AXIS_DOUT(输出复数结果)

- m_axis_dout_tdata[79:0]: 输出数据通道,通常用于传输复数乘法的结果,包括实部和虚部。

- m_axis_dout_tlast: 指示传输的最后一个数据。

- m_axis_dout_tready: 表示从端准备好接收输出数据。

- m_axis_dout_tuser[0:0]: 用户定义信号,用于传输与结果数据相关的控制信息。

- m_axis_dout_tvalid: 表示输出数据有效。

时钟和复位信号

- aclk: 时钟信号。

- aclken: 时钟使能信号,控制时钟是否启用。

- aresetn: 异步复位信号,低电平有效。

总结

- 数据通道(tdata): 传输数据的主要通道,包括输入复数A和B,以及输出复数结果。

- 控制信号(tuser, tvalid, tready, tlast): 控制和协调数据传输,确保数据的完整性和正确性。

- 时钟和复位(aclk, aclken, aresetn): 控制IP核的时钟和复位操作。

这些信号共同工作,确保复数乘法IP核能够正确接收输入数据、执行复数乘法计算,并输出结果。

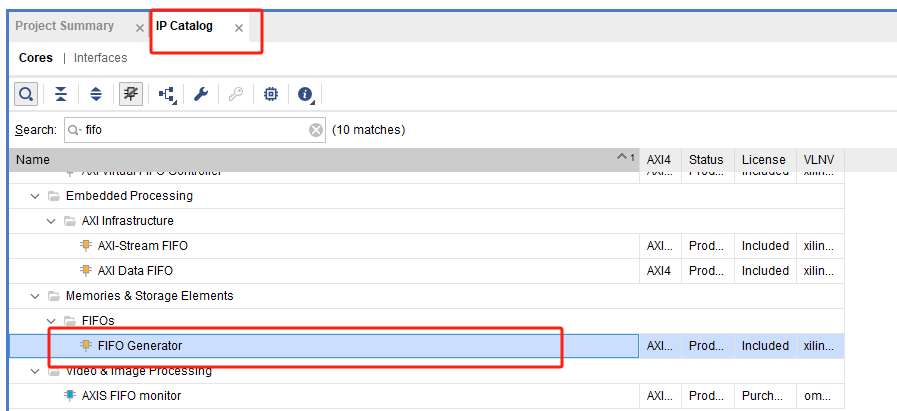

二、fifo

2.1 fifo的IP核创建

2.2 主要接口和引脚

可能用到的技术博客链接:FIFO IP的使用_fifo ip核使用-CSDN博客

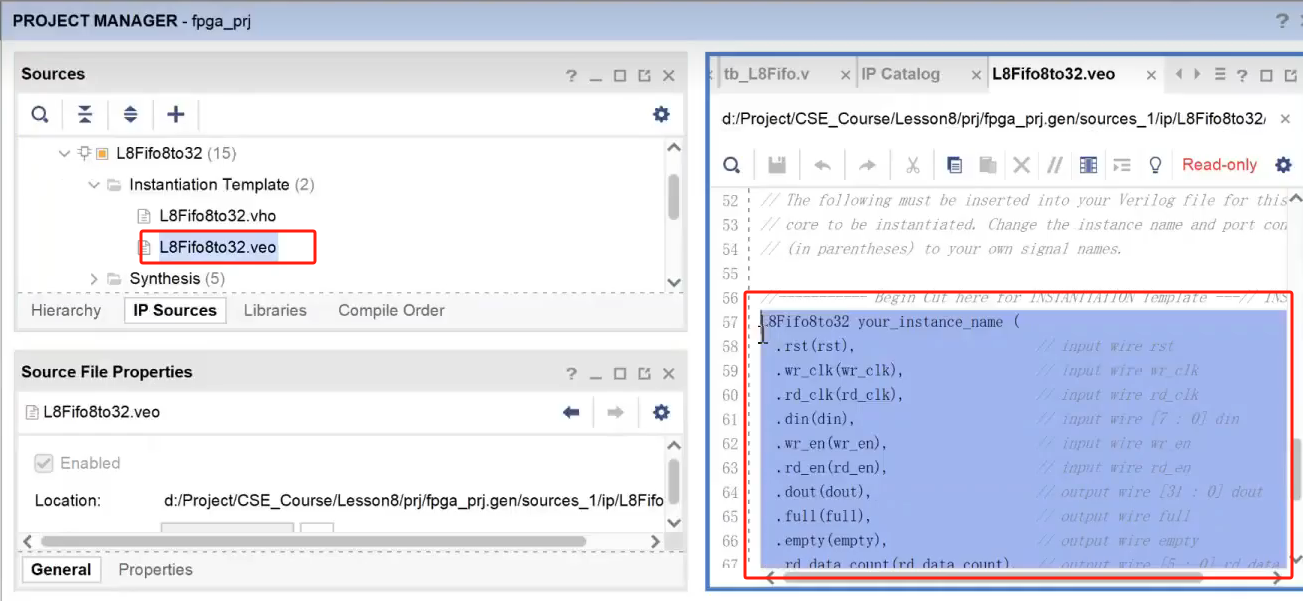

2.3 快捷实例化

找到.veo,然后复制右边的代码就很好实例化模块了

这篇关于常用IP核的引脚图的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!