本文主要是介绍I2S (二) 总线规范 翻译,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

飞利浦半导体

I2S总线规范(爱方诶死)

1.0 简介

许多数字音频系统正被引入消费音频市场,包括光盘、数字音频磁带、数字声音处理器和数字TV-sound.

这些系统中的数字音频信号是被许多大规模集成电路和甚大规模集成电路处理,

-

这些集成电路分类如下:

•A/D和D/A转换器;•数字信号处理器;•光盘和数字录音的纠错;•数字滤波器;•数字输入/输出接口。

标准化的通信结构对设备制造商和集成电路制造商都至关重要,无标准增加了系统的灵活性。

为此,我们开发了集成电路内部声音(i2s)总线,这是一种特别用于数字音频的串行连接。

2.0 基本串行总线要求

总线只需处理音频数据,而其他信号,如子编码和控制,则分别传输。

-

总线组成

为了尽量减少所需的管脚数量并保持布线简单,使用一条3线串行总线,该总线由一条分时复用数据通道(IN,OUT)的线、一条选字线和一条时钟线组成。 -

时钟线

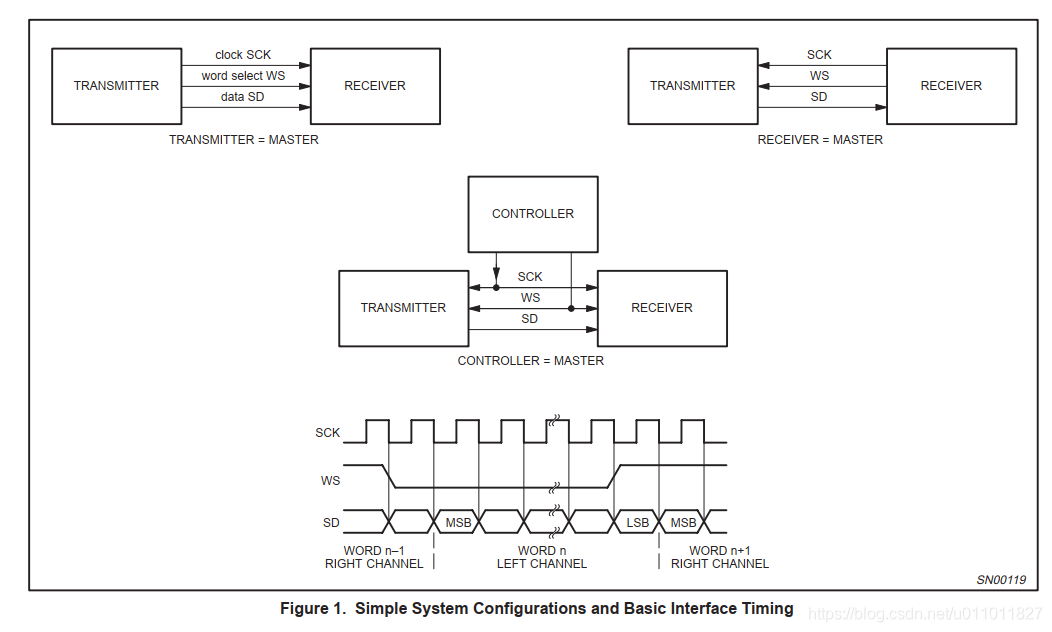

由于发射机和接收机具有相同的时钟信号用于同步数据传输,发射机作为主机,必须产生位时钟、选字信号和数据。然而,在复杂的系统中,可能有多个发射机和接收机,这使得很难定义主机。在这样的系统中,通常有一个系统主控器控制各个ic之间的数字音频数据流。然后,发射机必须在外部时钟的控制下生成数据,从而充当从机。

图1演示了一些简单的系统配置和基本的接口计时。注意,系统主机可以与发射机或接收机组合,并且可以在软件控制下或通过引脚编程来启用或禁用。

3.0 I2S总线

如图1所示,总线有三条线路:

•连续串行时钟(SCK); // 标准虽然是这样子,但是例如stm32F407 实现了5条线,(SCK,WS,SDIN,SDOUT,MCK)

•单词选择(WS);

•串行数据(SD);

生成sck和ws的设备是主设备

3.1串行数据

-

发送器发送

首先在SD线上发送msb(msb补码)当系统字长大于发送器字长时,该字被截断(最低有效数据位被设置为“0”)以进行数据传输。msb有一个固定的位置,而lsb的位置取决于单词的长度。 -

接收器接收

如果接收器接收(被发送)的比特数大于其字长,则忽略lsb之后的比特数。如果接收器接收(被发送)的比特少于其字长,则丢失的比特在内部设置为零。 -

接收与发送的位数

因为发射机和接收机的字长可能不同.发射机不需要知道接收机可以处理多少位,接收机也不需要知道传输了多少位。 -

一次发送

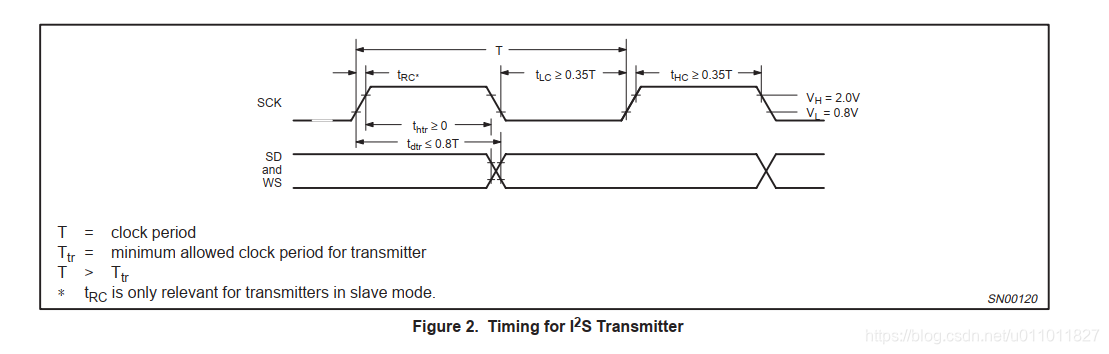

一次发送中的ws在ws改变后,发送器总是在一个时钟周期内发送下一个Word(这个word可能是16字节,32字节,48字节)的msb。一次发送中的clk发射机发送的串行数据可以与时钟信号的后缘(从高到低)或前缘(从低到高)同步。然而,串行数据必须锁存在串行时钟信号前沿的接收器中,因此在传输与前沿同步的数据时存在一些限制(参见图2和表1)。

3.2 Word Select

-

WS 现用来表示正在传输的信道,同步一个个word 的发送

•Ws=0;通道1(左); // 这里对应的是飞利浦指定的I2S标准格式下的 左声道和右声道. 左(0)右1, 如果为左对齐的话,左1右0•WS=1;通道2(右)。 -

一次发送中的ws (补充)

ws可能在串行时钟的后缘或前缘发生变化,但不需要对称。在从机中,该信号锁定在时钟信号的前沿。ws行在传输msb之前更改一个时钟周期。这允许从发送器导出将被设置用于传输的串行数据的同步时序。此外,它使接收器能够存储前一个单词并开始接收下一个单词(参见图1)。

4.0 时序

-

主机

在i2s格式中,任何设备都可以通过提供必要的时钟信号来充当系统主机。 -

延迟

从机通常从外部时钟输入导出其内部时钟信号。这意味着,考虑到外部(主)时钟(MCLK)与数据和/或字选择信号之间的传播延迟,总延迟简单地是:•外部(主)时钟和从机内部时钟之间的延迟•内部时钟与数据和/或字选择信号之间的延迟。对于数据和WS输入,外部到内部的时钟延迟没有任何影响,因为它只会延长有效的设置时间(见图2)。时间间隔的主要部分是调节发射机的传播延迟和设置接收机所需的时间之间的差异。 -

速率

所有时序要求都是相对于设备的时钟周期或最小允许时钟周期来规定的。这意味着未来可以使用更高的数据速率。

这篇关于I2S (二) 总线规范 翻译的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!