adder专题

【FPGA】Verilog:全加器与半加器 | Full Adder | Half Adder

0x00 全加器(Full Adder) 值的加法运算逻辑电路,全加器不仅可以包括输入值,还可以将进位值纳入加法运算,是实现各种运算电路的基本运算电路。输出由 sum (S) 和 carry (C) 组成,加法运算中产生的进位称为 carry out ,从前一位传递过来并需纳入当前位加法运算的进位称为 carry in 。 input (输入值2个,) 中,如果 1 的个数是奇数,

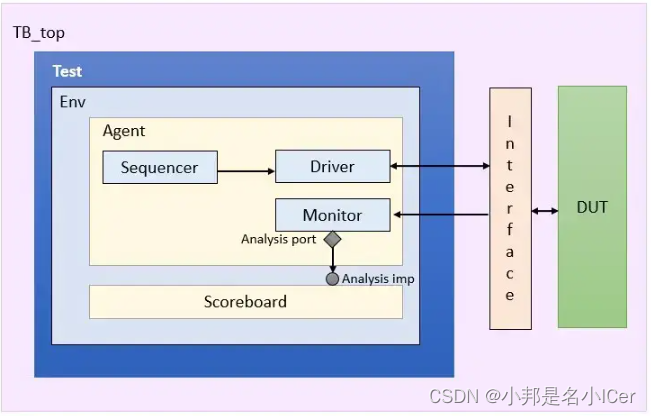

30 UVM Adder Testbench Example

1 Adder Design 加法器设计在时钟的上升沿产生两个变量的加法。复位信号用于clear out信号。注:加法器可以很容易地用组合逻辑开发。引入时钟和重置,使其具有测试台代码中时钟和重置的样子/风格。 module adder(input clk, reset, input [7:0] in1, in2, output reg [8:0] out);always@(posedge cl