1149.1专题

【JTAG】1149.1协议详解

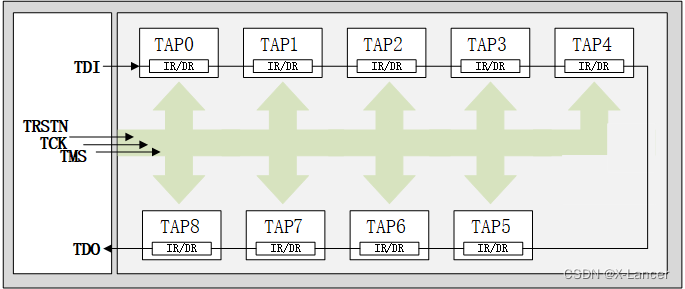

目录 一、简介 二、测试访问端口 2.1 端口说明 2.2 TAP 控制器 2.3 指令、数据寄存器 三、边界扫描结构 3.1 结构概览 3.2 BSR基本结构类型 3.3 EXTEST指令 四、多TAP扫描链 一、简介 1149.1协议定义了可包含在集成电路中的测试逻辑,以提供标准化的方法,其主要包含以下两点: 1.测试板级(PCB)

JTAG 标准IEEE STD 1149.1-2013学习笔记(四)Test logic controllers

文章目录 一、TAP控制器的状态转移图二、各状态介绍 注:转载请注明出处 参考JTAG标准第六章测试逻辑控制器(Test logic controllers)。 记录下学习过程,个人水平有限,可能理解有误,后续若发现错误之处,会及时更新。 VersionDate1.02021.12.15 这篇笔记用来介绍TAP 控制器,TAP控制器是同步有限状态机,状态根据 TMS 和 TCK

IEEE 1149.1 学习笔记(四)

指令寄存器 IR 指令寄存器允许指令移位到设计中。相关指令是用来选择即将执行的测试或者是对应TDR 的读取。IEEE1149.1 定义了强制性和可选择的指令,可实现特定设计指令的扩展。当然,IR 也可用于检查component 内部产生的特定设计信息检查。 IR 是基于移位寄存器的设计,除了与串行输出最接近的两个寄存器单元外,还有可选的并行输入。在TAP controller Update-I